Accélérer la conception de systèmes de reconnaissance visuelle avec les microprocesseurs série RZ/V2 de Renesas

Avec la contribution de Rédacteurs nord-américains de DigiKey

2022-09-29

La reconnaissance visuelle en périphérie devenant une fonction de plus en plus critique dans de nombreux produits, l'apprentissage automatique (Machine Learning, ML) et l'intelligence artificielle (IA) trouvent leur place dans un large éventail d'applications. Le problème auquel les développeurs sont confrontés est que la vision assistée par ML/IA peut nécessiter une puissance de calcul plus importante pour exécuter les algorithmes de reconnaissance que celle dont disposent les applications à puissance limitée. Elle ajoute également un coût si des solutions de gestion thermique coûteuses sont requises.

L'objectif pour l'apprentissage automatique/l'intelligence artificielle en périphérie est de trouver l'approche architecturale optimale qui permettra d'équilibrer les performances et la puissance, tout en fournissant un écosystème logiciel robuste dans lequel développer l'application.

Dans ce contexte, cet article présente une solution sous la forme du microprocesseur (MPU) série RZ/V2 de Renesas Electronics avec son accélérateur matériel IA intégré. L'article explore comment un microprocesseur, plutôt qu'un microcontrôleur (MCU) ou un processeur graphique (GPU) haut de gamme, peut résoudre plusieurs problèmes auxquels les concepteurs sont confrontés. Il décrit comment ils peuvent commencer à concevoir des systèmes de reconnaissance visuelle en utilisant la série RZ/V2, et propose quelques conseils et astuces pour faciliter le processus.

Présentation des microprocesseurs série RZ/V2

La série RZ/V2 est une solution qui libère de nombreuses capacités pour les développeurs utilisant un microprocesseur à trois cœurs. Les microprocesseurs série RZ/V2L contiennent deux processeurs Arm Cortex-A55 cadencés à 1,2 gigahertz (GHz) et un cœur de microcontrôleur en temps réel (Arm® Cortex®-M33) cadencé à 200 mégahertz (MHz). De plus, les composants de la série contiennent un processeur graphique basé sur un processeur multimédia Arm Mali-G31 avec des instructions NEON SIMD. La combinaison de ces trois cœurs de traitement et du processeur multimédia offre une solution complète aux développeurs travaillant sur des systèmes de reconnaissance visuelle.

Il existe actuellement deux classes de microprocesseurs dans la série RZ/V2, la série RZ/V2L et la série RZ/V2M. Le RZ/V2L est doté d'un processeur de signal d'image (ISP) simple, d'un moteur graphique 3D et d'un ensemble de périphériques très polyvalents. Le RZ/V2M, quant à lui, ajoute un ISP hautes performances qui prend en charge la résolution 4K à 30 images par seconde (fps). Cet article porte sur la famille RZ/V2L, composée du R9A07G054L23GBG et du R9A07G054L24GBG. La principale différence entre les deux produits est que le R9A07G054L23GBG est fourni en boîtier 456-LFBGA de 15 mm2, tandis que le R9A07G054L24GBG est fourni en boîtier 551-LFBGA de 21 mm2.

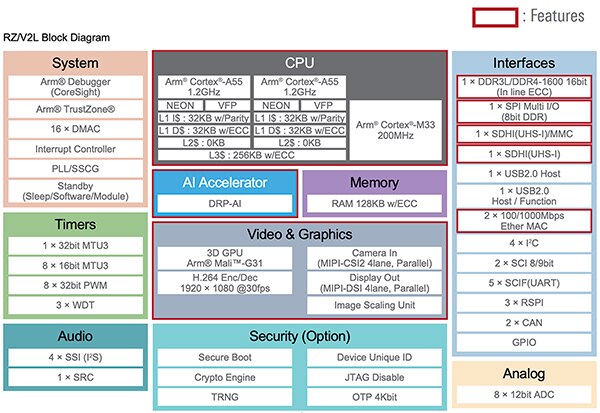

Le schéma fonctionnel de la série RZ/V2L est illustré à la Figure 1. En plus des trois cœurs de traitement, les microprocesseurs comprennent des interfaces pour des périphériques standard tels que mémoire DDR3/DDR4, SPI, USB, Ethernet, I²C, CAN, SCI, GPIO, et un convertisseur analogique-numérique (CAN). En outre, les produits incluent des fonctionnalités de sécurité telles qu'un démarrage sécurisé, un moteur de cryptage et un générateur de nombres véritablement aléatoires (TRNG). Mais ce qui distingue la série de microprocesseurs, c'est l'accélérateur IA DRP (Dynamically Reconfigurable Processor).

Figure 1 : La série de microprocesseurs RZ/V2L prend en charge diverses interfaces périphériques, la sécurité et les options de traitement vidéo. La fonctionnalité essentielle pour les applications de reconnaissance visuelle est l'accélérateur DRP-AI. (Source de l'image : Renesas Electronics Corporation)

Figure 1 : La série de microprocesseurs RZ/V2L prend en charge diverses interfaces périphériques, la sécurité et les options de traitement vidéo. La fonctionnalité essentielle pour les applications de reconnaissance visuelle est l'accélérateur DRP-AI. (Source de l'image : Renesas Electronics Corporation)

L'ingrédient secret de l'accélérateur DRP-AI

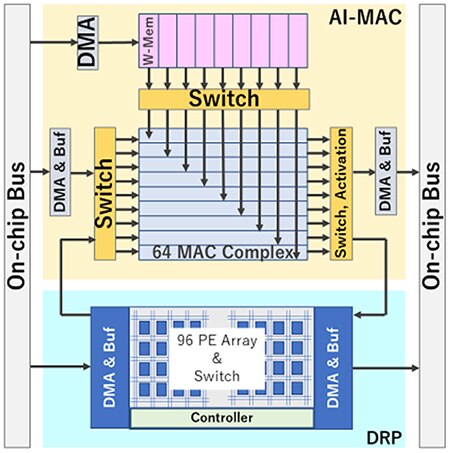

L'accélérateur DRP-AI est l'ingrédient secret qui permet aux microprocesseurs série RZ/V2L d'exécuter des applications de reconnaissance visuelle rapidement, avec une consommation d'énergie réduite et un profil thermique inférieur. Le DRP-AI comprend deux composants, DRP et AI-MAC, qui peuvent traiter efficacement les opérations dans les réseaux convolutifs et les couches de combinaison en optimisant le flux de données avec des commutateurs internes (Figure 2).

Le matériel DRP-AI est dédié à l'exécution des inférences IA. Le DRP-AI utilise une technologie reconfigurable dynamique unique développée par Renesas, offrant flexibilité, traitement haute vitesse et rendement énergétique. De plus, le traducteur DRP-AI, un outil logiciel gratuit, permet aux utilisateurs de mettre en œuvre des modèles IA optimisés qui maximisent rapidement les performances. Plusieurs exécutables générés par le traducteur DRP-AI peuvent être placés dans une mémoire externe. L'application peut alors basculer dynamiquement entre plusieurs modèles IA pendant l'exécution.

Le DRP peut traiter rapidement des activités complexes telles que le pré-traitement d'images et les couches de mise en commun de modèles IA en modifiant dynamiquement la configuration matérielle.

Figure 2 : Le DRP-AI comprend un DRP et un AI-MAC qui, ensemble, peuvent traiter efficacement les opérations dans les réseaux convolutifs et les couches de combinaison en optimisant le flux de données avec des commutateurs internes. (Source de l'image : Renesas Electronics Corporation)

Figure 2 : Le DRP-AI comprend un DRP et un AI-MAC qui, ensemble, peuvent traiter efficacement les opérations dans les réseaux convolutifs et les couches de combinaison en optimisant le flux de données avec des commutateurs internes. (Source de l'image : Renesas Electronics Corporation)

Outil DRP-AI Translator

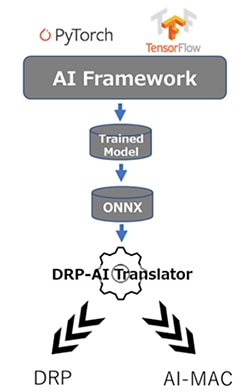

Le traducteur DRP-AI Translator génère des exécutables optimisés pour DRP-AI à partir de modèles ONNX entraînés, indépendamment de toute structure IA. Par exemple, un développeur peut utiliser PyTorch, TensorFlow ou toute autre structure de modélisation IA si elle génère un modèle ONNX. Une fois le modèle entraîné, il est introduit dans le DRP-AI Translator, qui génère les exécutables DRP et AI-MAC (Figure 3).

Figure 3 : Les modèles IA sont entraînés à l'aide de toute structure compatible ONNX. Le modèle ONNX est ensuite introduit dans le DRP-AI Translator, qui génère les exécutables DRP et AI-MAC. (Source de l'image : Renesas Electronics Corporation)

Figure 3 : Les modèles IA sont entraînés à l'aide de toute structure compatible ONNX. Le modèle ONNX est ensuite introduit dans le DRP-AI Translator, qui génère les exécutables DRP et AI-MAC. (Source de l'image : Renesas Electronics Corporation)

Le DRP-AI Translator a trois rôles principaux :

- Planifier chaque opération pour traiter le modèle IA.

- Masquer les surcharges telles que le temps d'accès à la mémoire qui se produit lors de chaque transition d'opération dans la planification.

- Optimiser la structure du graphe réseau.

Le traducteur alloue automatiquement chaque processus du modèle IA à l'AI-MAC et au DRP, ce qui permet à l'utilisateur d'utiliser facilement le DRP-AI sans être un expert en matériel. Le développeur peut alternativement effectuer des appels via le pilote fourni pour exécuter le modèle IA hautes performances. En outre, le DRP-AI Translator peut être mis à jour en permanence pour prendre en charge les nouveaux modèles IA sans modification du matériel.

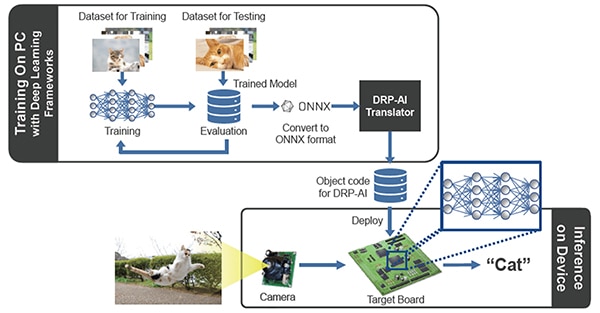

Cas d'utilisation du système et processus

Le processus général d'utilisation des microprocesseurs RZ/V2L pour entraîner et déployer des applications de reconnaissance visuelle est illustré à la Figure 4. Les ingénieurs peuvent acquérir leur jeu de données et l'utiliser pour entraîner leur modèle de reconnaissance visuelle, de manière habituelle. Qu'il s'agisse d'identifier des chats, un produit dans un panier d'achat ou des pièces défectueuses sur une chaîne de montage, le processus d'entraînement est effectué à l'aide de structures IA familières. Une fois le modèle entraîné, il est converti au format ONNX et introduit dans le traducteur DRP-AI Translator, qui génère un code objet pouvant être exécuté sur le matériel DRP-AI. Les données provenant des caméras, des accéléromètres ou d'autres capteurs sont ensuite échantillonnées et injectées dans les exécutables, fournissant le résultat de l'exécution de l'inférence.

Figure 4 : Processus d'entraînement et d'exécution d'un algorithme de reconnaissance visuelle sur les microprocesseurs RZ/V2L. (Source de l'image : Renesas Electronics Corporation)

Figure 4 : Processus d'entraînement et d'exécution d'un algorithme de reconnaissance visuelle sur les microprocesseurs RZ/V2L. (Source de l'image : Renesas Electronics Corporation)

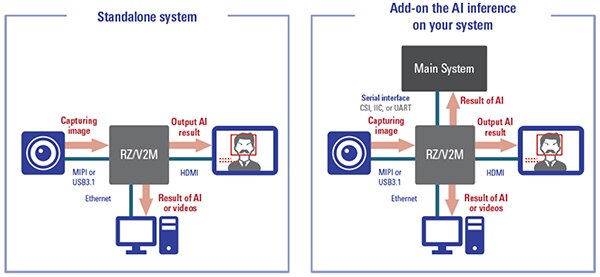

Les ingénieurs peuvent tirer parti des microprocesseurs RZ/V2L de plusieurs manières dans leurs conceptions (Figure 5). Tout d'abord, le microprocesseur RZ/V2L peut être utilisé dans des conceptions autonomes où le RZ/V2L est le seul processeur du système. Avec ses trois cœurs et son matériel d'accélération IA, une puissance de calcul supplémentaire peut ne pas être nécessaire.

Dans le deuxième cas d'utilisation, le RZ/V2L est utilisé comme processeur IA dans un système plus étendu. Dans ce cas d'utilisation, le RZ/V2L exécute les inférences IA et renvoie un résultat à un autre processeur ou système qui agit ensuite sur ce résultat. Le cas d'utilisation choisi dépendra de divers facteurs tels que le coût, l'architecture globale du système, les performances et les exigences de réponse en temps réel.

Figure 5 : Les deux cas d'utilisation des microprocesseurs RZ/V2L sont l'utilisation autonome dans une application ou l'utilisation comme processeur IA dans un système plus étendu. (Source de l'image : Renesas Electronics Corporation)

Figure 5 : Les deux cas d'utilisation des microprocesseurs RZ/V2L sont l'utilisation autonome dans une application ou l'utilisation comme processeur IA dans un système plus étendu. (Source de l'image : Renesas Electronics Corporation)

Exemple d'application concret

Il existe de nombreux cas d'utilisation où la technologie de reconnaissance visuelle peut être déployée. Un exemple intéressant est celui du supermarché. Actuellement, à la caisse dans un magasin, un employé ou un client scanne généralement chaque article du chariot. Une application intéressante serait de reconnaître les produits qui passent sur le tapis roulant à l'aide de la reconnaissance visuelle et de facturer automatiquement ces produits.

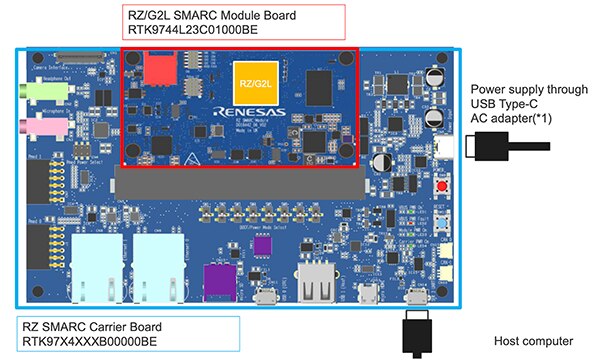

Un prototype peut être construit en utilisant une simple caméra CMOS et la carte d'évaluation RTK9754L23S01000BE de Renesas (Figure 6). La carte de développement embarquée RZ/V2L comporte un système sur module (SOM) et une carte porteuse qui permettent aux développeurs d'être rapidement opérationnels. En outre, la carte de développement prend en charge Linux, ainsi que divers outils tels que le DRP-AI Translator.

Figure 6 : La carte de développement embarquée RZ/V2L est équipée d'un SOM et d'une carte porteuse qui permettent aux développeurs d'être rapidement opérationnels. (Source de l'image : Renesas Electronics Corporation)

Figure 6 : La carte de développement embarquée RZ/V2L est équipée d'un SOM et d'une carte porteuse qui permettent aux développeurs d'être rapidement opérationnels. (Source de l'image : Renesas Electronics Corporation)

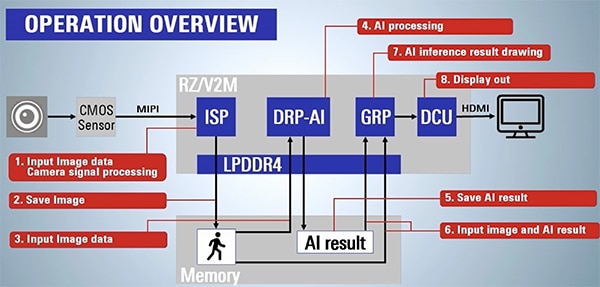

La Figure 7 donne un aperçu opérationnel de ce qui est nécessaire pour acquérir des données d'image et générer un résultat IA. Dans cet exemple d'application, des images du tapis roulant sont capturées à l'aide d'un capteur CMOS via l'ISP embarqué. Ensuite, l'image est enregistrée en mémoire et injectée dans le moteur DRP-AI. Enfin, le moteur DRP-AI exécute l'inférence et fournit un résultat IA. Par exemple, le résultat peut être l'identification d'une banane, d'une pomme ou d'un autre fruit.

Le résultat est souvent accompagné d'un niveau de confiance de 0 à 1. Par exemple, un niveau de confiance de 0,90 signifie que l'IA est sûre d'avoir détecté une pomme. En revanche, un niveau de confiance de 0,52 peut indiquer que l'IA pense qu'il s'agit d'une pomme mais qu'elle n'est pas sûre. Il n'est pas rare de prendre un résultat IA et de le moyenner sur plusieurs échantillons pour améliorer les chances d'obtenir des résultats corrects.

Figure 7 : La carte de développement embarquée RZ/V2L est utilisée pour exécuter une inférence IA qui reconnaît différents fruits sur un tapis roulant. Le schéma montre les étapes nécessaires pour acquérir une image et générer un résultat IA. (Source de l'image : Renesas Electronics Corporation)

Figure 7 : La carte de développement embarquée RZ/V2L est utilisée pour exécuter une inférence IA qui reconnaît différents fruits sur un tapis roulant. Le schéma montre les étapes nécessaires pour acquérir une image et générer un résultat IA. (Source de l'image : Renesas Electronics Corporation)

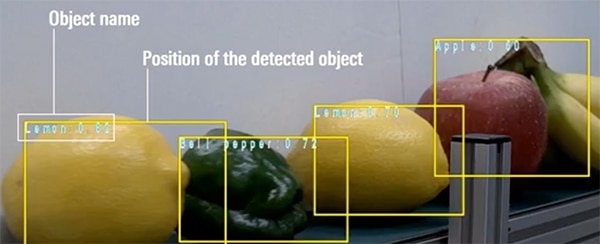

Enfin, dans cet exemple, un cadre est dessiné autour de l'objet détecté, et le nom de l'objet reconnu est affiché avec le niveau de confiance (Figure 8).

Figure 8 : Exemple de résultat du RZ/V2L dans une application de détection des fruits et légumes sur un tapis roulant. (Source de l'image : Renesas Electronics Corporation)

Figure 8 : Exemple de résultat du RZ/V2L dans une application de détection des fruits et légumes sur un tapis roulant. (Source de l'image : Renesas Electronics Corporation)

Conseils et astuces pour débuter avec le RZ/V2L

Les développeurs qui souhaitent se lancer dans l'apprentissage automatique sur les microprocesseurs RZ/V2L de Renesas peuvent exploiter un grand nombre de ressources pour démarrer les opérations. Voici plusieurs conseils et astuces que les développeurs peuvent prendre en compte pour simplifier et accélérer leur développement :

- Débutez avec une carte de développement et des exemples existants pour vous familiariser avec le déploiement et l'exécution d'une application.

- S'il est nécessaire d'exécuter plusieurs inférences, enregistrez les modèles exécutables dans une mémoire externe et utilisez les capacités du DRP-AI pour passer rapidement d'un modèle à l'autre.

- Consultez la documentation et les vidéos disponibles sur le site RZ/V Embedded AI MPUs de Renesas.

- Téléchargez l'outil DRP-AI Translator.

- Téléchargez le pack de support RZ/V2L DRP-AI.

Les développeurs qui suivent ces conseils et astuces constateront qu'ils économisent beaucoup de temps et d'efforts au démarrage.

Conclusion

L'apprentissage automatique et l'intelligence artificielle trouvent leur place dans de nombreuses applications en périphérie, à mesure que la capacité à reconnaître des objets en temps réel devient de plus en plus importante. Pour les concepteurs, la difficulté consiste à trouver l'architecture appropriée pour effectuer l'exécution IA/ML en périphérie. Les processeurs graphiques ont tendance à être gourmands en énergie, tandis que les microcontrôleurs peuvent ne pas avoir une puissance de calcul suffisante.

Comme illustré, la série de microprocesseurs RZ/V avec DRP-AI de Renesas présente plusieurs avantages tels que l'IA à accélération matérielle, ainsi qu'une chaîne d'outils et un support de prototypage étendus.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.