Pourquoi et comment utiliser les FPGA d'Efinix pour l'imagerie IA/ML — 1re partie : démarrage

Avec la contribution de Rédacteurs européens de DigiKey

2023-04-20

Note de l'éditeur : les nouvelles approches en matière d'architectures FPGA offrent un contrôle plus précis et une plus grande flexibilité pour répondre aux besoins de l'apprentissage automatique (ML) et de l'intelligence artificielle (IA). La 1re partie de cette série en deux parties présente une telle architecture d'Efinix et explique comment commencer à l'utiliser à l'aide d'une carte de développement. La 2e partie traite de l'interfaçage de la carte de développement avec des dispositifs et des périphériques externes, tels qu'une caméra.

Les FPGA jouent un rôle essentiel dans de nombreuses applications, du contrôle et de la sécurité industriels à la robotique, l'aérospatiale et l'automobile. Grâce à la nature flexible du cœur logique programmable et à la vaste capacité d'interfaçage, un cas d'utilisation croissant pour les FPGA est le traitement d'image lorsque l'inférence ML doit être déployée. Les FPGA sont parfaits pour mettre en œuvre des solutions dotées de plusieurs interfaces de caméra haute vitesse. De plus, les FPGA permettent également d'implémenter des pipelines de traitement dédiés dans la logique, éliminant ainsi les goulets d'étranglement qui seraient associés aux solutions basées sur des processeurs (CPU) ou des processeurs graphiques (GPU).

Pour de nombreux développeurs, cependant, leurs applications requièrent davantage de fonctionnalités ML/IA et une logique et un contrôle ou un routage plus précis, au-delà de ce que les architectures FPGA classiques avec des blocs logiques combinatoires (CLB) peuvent fournir. Les nouvelles approches des architectures FPGA résolvent ces problèmes. Par exemple, l'architecture Quantum d'Efinix utilise un bloc XLR (eXchangeable Logic and Routing).

Cet article traite des fonctionnalités et attributs clés de l'architecture FPGA d'Efinix, en mettant l'accent sur ses capacités IA/ML et en présentant des implémentations concrètes. Il présente ensuite une carte de développement et les outils associés que les développeurs peuvent utiliser pour démarrer rapidement leur prochaine conception d'imagerie IA/ML.

Dispositifs FPGA d'Efinix

Efinix propose actuellement deux gammes de dispositifs. Ils ont d'abord lancé la gamme Trion, qui offre des densités logiques de 4000 (4K) à 120 K éléments logiques (LE), et est fabriquée à l'aide d'un processus SMIC 40LL. La nouvelle gamme de dispositifs Titanium offre des densités logiques de 35 K à 1 million (M) d'éléments logiques, et est basée sur le très populaire nœud TSMC 16 nanomètres (nm).

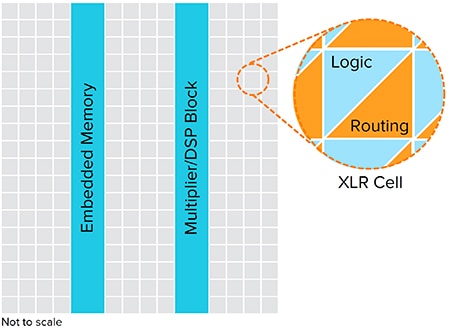

Les deux offres reposent sur l'architecture Quantum, qui est unique dans le monde des FPGA. L'architecture FPGA standard est basée sur des blocs CLB qui, au niveau le plus simple, contiennent une table de correspondance (LUT) et des bascules flip-flop. Les CLB implémentent des équations logiques qui sont ensuite interconnectées via le routage. Avec le bloc XLR, l'architecture Quantum d'Efinix s'affranchit des blocs logiques et de routage distincts.

Ce qui rend un bloc XLR unique, c'est qu'il peut être configuré pour fonctionner comme une cellule logique avec une table LUT, un registre et un additionneur, ou une matrice de routage. Cette approche offre une architecture plus fine qui fournit une flexibilité de routage, permettant aux implémentations lourdes en logique ou en routage d'atteindre les performances souhaitées.

Figure 1 : Ce qui rend un bloc XLR unique, c'est qu'il peut être configuré pour fonctionner soit comme une cellule logique avec une table LUT, un registre et un additionneur, soit comme une matrice de routage. (Source de l'image : Efinix)

Figure 1 : Ce qui rend un bloc XLR unique, c'est qu'il peut être configuré pour fonctionner soit comme une cellule logique avec une table LUT, un registre et un additionneur, soit comme une matrice de routage. (Source de l'image : Efinix)

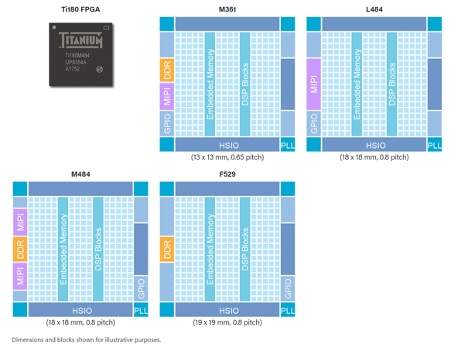

En tant que gamme la plus récente, les dispositifs Titanium offrent les fonctionnalités les plus avancées pour le développeur (Figure 2). En plus du cœur XLR, ils fournissent des liaisons série multi-gigabits qui fonctionnent à 16 gigabits par seconde (Gbps) ou 25,8 Gbps, selon le dispositif sélectionné. Ces liaisons multi-gigabits sont cruciales pour permettre le transfert de données à haut débit sur et hors puce.

Figure 2 : Le FPGA Titanium Ti180 est disponible dans une variété d'options en fonction de la largeur du bus, des E/S et des exigences de mémoire. (Source de l'image : Efinix)

Figure 2 : Le FPGA Titanium Ti180 est disponible dans une variété d'options en fonction de la largeur du bus, des E/S et des exigences de mémoire. (Source de l'image : Efinix)

Les dispositifs Titanium offrent également de nombreuses capacités d'interface entrée/sortie (E/S) qui peuvent être regroupées en tant qu'E/S à usage général (GPIO) et qui peuvent prendre en charge des normes E/S asymétriques telles que CMOS basse tension (LVCMOS) à 3,3 volts (V), 2,5 V et 1,8 V.

Pour l'interfaçage différentiel et haute vitesse, les dispositifs Titanium fournissent des E/S haute vitesse (HSIO) qui prennent en charge les normes E/S asymétriques telles que LVCMOS à 1,2 V, 1,5 V, et SSTL et HSTL. Les normes E/S différentielles prises en charge par les HSIO incluent LVDS, SSTL différentiel et HSTL.

Les FPGA modernes requièrent également une mémoire étroitement couplée à bande passante élevée, qui est utilisée pour stocker des images pour les applications de traitement d'image, des échantillons de données pour le traitement des signaux et, bien sûr, pour exécuter des systèmes d'exploitation et des logiciels pour les processeurs implémentés dans le FPGA. La gamme de dispositifs Titanium offre la possibilité d'interfacer avec des mémoires DDR4 et DDR4(x) basse consommation (LPDDR4(x)). Selon le dispositif Titanium exact sélectionné, la prise en charge de la largeur de bus est x32 (J) ou x16 (M), tandis que certains dispositifs n'offrent pas de prise en charge LPDDR4 (L).

Les FPGA Titanium sont basés sur la mémoire SRAM et nécessitent une mémoire de configuration, la configuration du dispositif étant effectuée soit par SPI maître/esclave soit par JTAG. Pour garantir la sécurité de cette méthode de configuration, le FPGA Titanium utilise le chiffrement AES GCM du flux binaire, et AES GCM et RSA-4096 pour fournir une authentification du flux binaire. Une telle sécurité renforcée est requise car les FPGA sont déployés en périphérie où des acteurs malveillants pourraient accéder et manipuler leur comportement.

Présentation de la carte de développement

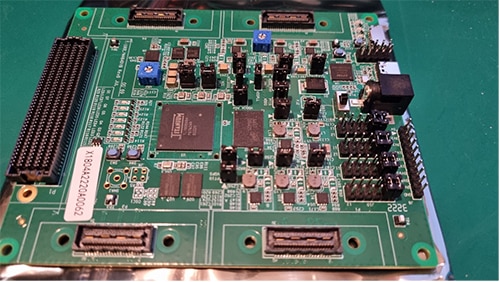

Les cartes de développement constituent un élément essentiel du processus d'évaluation des FPGA, car elles peuvent être utilisées pour explorer les capacités d'un dispositif et prototyper des applications, contribuant ainsi à réduire le risque global. La première carte de développement disponible pour évaluer les FPGA Titanium et commencer le prototypage d'applications est la carte Ti180 M484 (Figure 3). La carte est dotée d'un connecteur de carte mezzanine FPGA (FMC) et de quatre connecteurs QSE de Samtec.

Figure 3 : Outre un FPGA Titanium, le kit de développement Ti180 M484 inclut un connecteur FMC et quatre connecteurs QSE de Samtec. (Source de l'image : Adam Taylor)

Figure 3 : Outre un FPGA Titanium, le kit de développement Ti180 M484 inclut un connecteur FMC et quatre connecteurs QSE de Samtec. (Source de l'image : Adam Taylor)

Le FPGA Ti180 installé sur cette carte de développement fournit 172 000 cellules XLR, 32 horloges globales, 640 éléments de traitement des signaux numériques (DSP) et 13 mégabits (Mb) de RAM embarquée. Les éléments DSP permettent d'implémenter des multiplications 18 x 19 à virgule fixe et des multiplications 48 bits. Ce DSP peut également être optimisé pour les opérations à instruction unique, données multiples (SIMD) exécutées dans une configuration double ou quadruple. Les éléments DSP peuvent également être configurés pour effectuer des opérations en virgule flottante.

Comme la plupart des cartes de développement, la carte de développement Ti180 fournit des boutons et des LED simples. Sa véritable puissance, cependant, réside dans ses capacités d'interfaçage. La carte de développement Ti180 fournit un connecteur FMC à faible nombre de broches qui permet de connecter une large gamme de périphériques. Comme il s'agit d'une norme largement utilisée, il existe de nombreuses cartes FMC qui permettent l'interfaçage de solutions haute vitesse de convertisseurs analogique-numérique (CAN), de convertisseurs numérique-analogique (CNA), de mise en réseau et de mémoire/stockage.

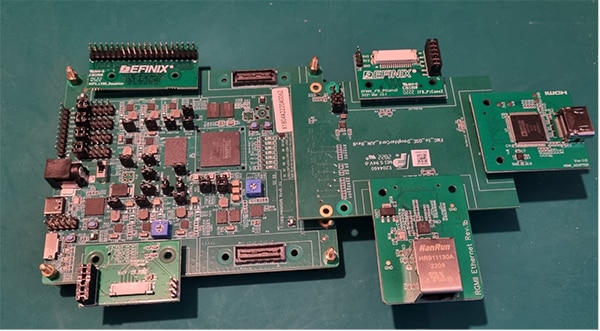

En plus de la connexion FMC, la carte fournit quatre connecteurs QSE de Samtec qui permettent au développeur d'ajouter des cartes d'extension. Ces connecteurs QSE sont utilisés pour fournir des entrées et des sorties MIPI, chaque connecteur QSE fournissant soit une entrée soit une sortie MIPI.

Figure 4 : Le kit de développement Ti180 M484 est illustré avec son choix polyvalent de possibilités d'extension reposant sur les connecteurs QSE et FMC. (Source de l'image : Adam Taylor)

Figure 4 : Le kit de développement Ti180 M484 est illustré avec son choix polyvalent de possibilités d'extension reposant sur les connecteurs QSE et FMC. (Source de l'image : Adam Taylor)

La carte Ti180 fournit également 256 Mb de LPDDR4 pour prendre en charge la mémoire hautes performances requise dans les applications de traitement d'image ou de signal. De plus, la carte de développement fournit une série d'options de cadencement à 25 mégahertz (MHz), 33,33 MHz, 50 MHz et 74,25 MHz, qui peuvent être utilisées avec la boucle à verrouillage de phase (PLL) du dispositif pour générer différentes fréquences internes.

La possibilité de reprogrammer et de déboguer en direct sur la carte pendant le développement est essentielle et requiert une connexion JTAG, qui est fournie via une interface USB-C. Une mémoire non volatile est également fournie sous la forme de deux dispositifs Flash NOR de 256 Mb qui peuvent être utilisés pour démontrer la solution de configuration.

La carte est alimentée par un adaptateur secteur universel de 12 V inclus. Une sortie FMC vers QSE est également incluse, ainsi que des cartes d'extension basées sur QSE pour HDMI, Ethernet, MIPI et LVDS. Pour démontrer les capacités de traitement d'image du Ti180, une carte fille RPI double et deux cartes de caméra IMX477 sont également fournies.

Environnement logiciel

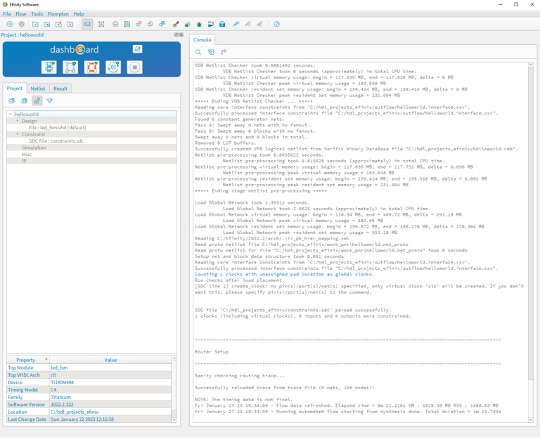

La mise en œuvre de conceptions ciblant la carte de développement Ti180 utilise le logiciel Efinity d'Efinix. Le logiciel permet la génération d'un flux binaire via la synthèse et le placement et le routage. Il fournit également aux développeurs des blocs de propriété intellectuelle (IP), une analyse temporelle et un débogage sur puce.

Notez qu'une carte de développement est requise pour accéder au logiciel Efinity. Contrairement à d'autres fournisseurs, cependant, l'outil n'a pas différentes versions exigeant des licences supplémentaires.

Dans Efinity, de nouveaux projets sont créés en ciblant le dispositif sélectionné. Des fichiers RTL peuvent ensuite être ajoutés au projet et des contraintes créées pour la temporisation et la conception E/S. C'est dans Efinity que les développeurs peuvent également implémenter la conception E/S, en utilisant des HSIO, des GPIO et des E/S spécialisées.

Figure 5 : Dans Efinity, de nouveaux projets sont créés en ciblant le dispositif sélectionné. (Source de l'image : Adam Taylor)

Figure 5 : Dans Efinity, de nouveaux projets sont créés en ciblant le dispositif sélectionné. (Source de l'image : Adam Taylor)

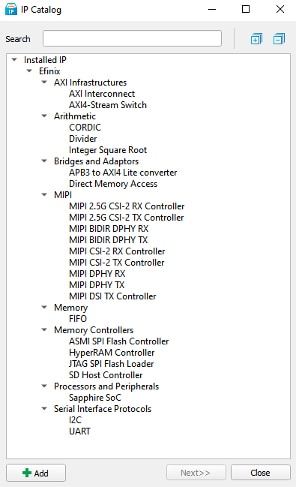

Un élément critique de la conception FPGA est l'utilisation de l'IP, en particulier pour les IP complexes tels que les interconnexions AXI, les contrôleurs de mémoire et les processeurs softcore. Efinity fournit aux développeurs une série de blocs IP qui peuvent être utilisés pour accélérer le processus de conception.

Figure 6 : Efinity fournit aux développeurs un catalogue IP qu'ils peuvent utiliser pour accélérer le processus de conception. (Source de l'image : Adam Taylor)

Figure 6 : Efinity fournit aux développeurs un catalogue IP qu'ils peuvent utiliser pour accélérer le processus de conception. (Source de l'image : Adam Taylor)

Tandis que les FPGA excellent pour la mise en œuvre de structures de traitement parallèles, de nombreuses conceptions FPGA incluent des processeurs softcore. Ceux-ci offrent la possibilité d'implémenter un traitement séquentiel, tel que des communications réseau. Pour permettre le déploiement des processeurs softcore dans les dispositifs d'Efinix, Efinity fournit l'outil de configuration de système sur puce (SoC) Sapphire. Sapphire permet au développeur de définir un système multiprocesseur qui dispose à la fois de caches et d'une cohérence de cache sur plusieurs processeurs, et qui permet d'exécuter un système d'exploitation Linux embarqué. Dans Sapphire, le développeur peut choisir entre un et quatre processeurs softcore.

Le processeur softcore implémenté est le processeur VexRiscV, qui est basé sur l'architecture du jeu d'instructions RISC-V. Le processeur VexRiscV est une implémentation 32 bits qui est dotée d'extensions pour le pipelining et offre un ensemble de fonctionnalités configurables, ce qui le rend idéal pour une implémentation dans les dispositifs d'Efinix. Les configurations en option incluent un multiplicateur, des instructions atomiques, des extensions en virgule flottante et des instructions compressées. Selon la configuration du système SoC, les performances seront comprises entre 0,86 et 1,05 DMIPS/MHz.

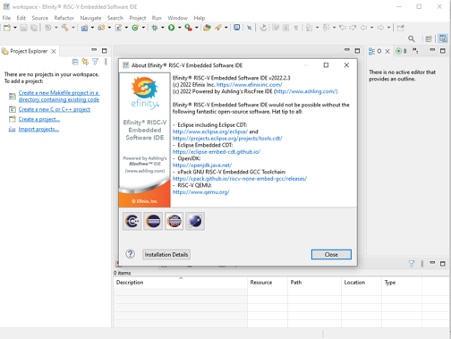

Une fois l'environnement matériel conçu et implémenté dans le dispositif d'Efinix, le logiciel d'application peut être développé à l'aide de l'environnement de développement intégré (IDE) Ashling RiscFree. Ashling RiscFree est un IDE basé sur Eclipse qui permet la création et la compilation de logiciels d'application, ainsi que le débogage sur la cible pour ajuster l'application avant le déploiement.

Figure 7 : Ashling RiscFree est un IDE basé sur Eclipse qui permet la création et la compilation de logiciels d'application, ainsi que le débogage sur la cible. (Source de l'image : Adam Taylor)

Figure 7 : Ashling RiscFree est un IDE basé sur Eclipse qui permet la création et la compilation de logiciels d'application, ainsi que le débogage sur la cible. (Source de l'image : Adam Taylor)

Si une solution Linux embarquée est en cours de développement, tous les artefacts de démarrage nécessaires sont fournis, y compris First Stage Boot Loader, OpenSBI, U-Boot et Linux avec Buildroot. Alternativement, le développeur peut utiliser FreeRTOS si une solution en temps réel est requise.

Implémentation IA

L'implémentation IA d'Efinix s'appuie sur le fonctionnement softcore RISC-V. Elle tire parti de la capacité d'instruction personnalisée du processeur RISC-V pour permettre l'accélération des solutions TensorFlow Lite. L'utilisation du processeur RISC-V permet également aux utilisateurs de créer des instructions personnalisées qui peuvent être utilisées dans le cadre du pré-traitement ou du post-traitement suivant l'inférence IA, créant ainsi une solution plus réactive et déterministe.

Pour démarrer une implémentation IA, la première étape consiste à explorer Model Zoo d'Efinix, qui est une bibliothèque de modèles IA/ML optimisés pour sa technologie finale. Pour les développeurs travaillant avec des dispositifs d'Efinix, Model Zoo est accessible et le réseau entraîné à l'aide de Jupyter Notebooks ou Google Colab. Une fois le réseau entraîné, il peut être converti d'un modèle à virgule flottante en un modèle quantifié à l'aide du convertisseur TensorFlow Lite.

Une fois au format TensorFlow Lite, l'accélérateur tinyML d'Efinix peut être utilisé pour créer une solution déployable sur la solution RISC-V. Le générateur tinyML permet au développeur de personnaliser l'implémentation de l'accélérateur et de générer les fichiers du projet. Avec ce type de déploiement, l'accélération peut s'étendre de 4 fois à 200 fois selon l'architecture et la personnalisation sélectionnées.

Conclusion

Les dispositifs d'Efinix offrent aux développeurs une grande flexibilité grâce à leur architecture XLR unique. La chaîne d'outils permet non seulement d'implémenter la conception RTL, mais également d'implémenter des solutions SoC complexes qui déploient des processeurs softcore RISC-V. Le SoC softcore est complété par une solution IA/ML qui permet le déploiement de l'inférence ML

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.