Activation de l'interface SSD NVMe sur un kit d'évaluation Xilinx ZCU102

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-05-12

Présentation

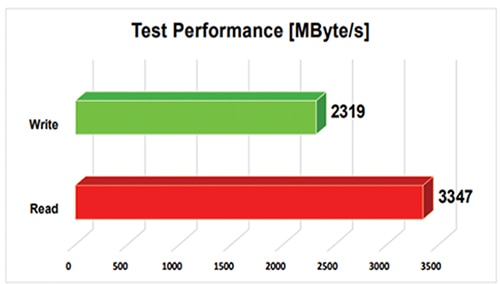

La gamme Zynq® UltraScale+™ MPSoC, reposant sur l'architecture MPSoC UltraScale™ de Xilinx®, intègre un système de traitement (PS) basé sur Arm à deux ou quatre cœurs 64 bits riche en fonctionnalités et une architecture UltraScale logique programmable (PL) de Xilinx dans un seul dispositif. Elle inclut également une mémoire sur puce, des interfaces mémoires externes multiports et un riche ensemble d'interfaces de connectivité périphériques, notamment un émetteur-récepteur de 16,3 Gbps GTH capable de prendre en charge une interface de dispositif de stockage PCI Express® Gen3 comme un disque SSD NVMe. Cet article étudie la solution d'implémentation d'interface SSD NVMe sur le kit d'évaluation ZCU102 de Xilinx, en utilisant le bloc NVMeG3-IP de Design Gateway capable d'atteindre des performances incroyablement rapides : une vitesse d'écriture de 2319 Mo/s et une vitesse de lecture de 3347 Mo/s.

Présentation du kit d'évaluation Zynq® UltraScale+ MPSoC ZCU102

Le kit d'évaluation ZCU102 est une carte d'évaluation à usage général pour le prototypage rapide, reposant sur le dispositif MPSoC XCZU9EG-2FFVB1156E. La carte inclut une mémoire SODIMM DDR4 haute vitesse et des interfaces mémoires de composants, des ports d'extension FMC, des émetteurs-récepteurs série multi-gigabits par seconde, diverses interfaces périphériques et une logique FPGA pour les conceptions utilisateur personnalisées, tous ces éléments fournissant une plateforme de prototypage flexible.

Figure 1 : Kit d'évaluation ZCU102. (Source de l'image : Xilinx Inc.)

Figure 1 : Kit d'évaluation ZCU102. (Source de l'image : Xilinx Inc.)

Le kit d'évaluation ZCU102 fournit des capacités de logique programmable pour la création d'applications de pointe comme les solutions 5G sans fil, les systèmes avancés d'aide à la conduite (ADAS) nouvelle génération et les solutions Internet industriel des objets (IIoT).

Dans tous les cas, pour une application qui nécessite un stockage de données externe offrant des performances et une fiabilité élevées, comme les disques SSD NVMe, une solution appropriée tirant parti de l'émetteur-récepteur GTH pour l'interface PCI Express® Gen3 est requise.

Présentation du stockage SSD NVMe

NVM Express (NVMe) définit l'interface à laquelle le contrôleur hôte peut accéder en tant que SSD par PCI Express. NVM Express optimise le processus d'émission de commande et d'achèvement en utilisant seulement deux registres (émission de commande et achèvement de commande). Par ailleurs, NVMe permet un fonctionnement parallèle en prenant en charge jusqu'à 64 000 commandes dans une même file d'attente. Les 64 000 entrées de commande améliorent les performances de transfert pour l'accès séquentiel et aléatoire.

Les disques NVMe ont ouvert la voie au stockage de données et à l'informatique à très haute vitesse. En utilisant une technologie PCIe Express® Gen3, les disques SSD NVMe modernes peuvent atteindre des vitesses de crête de 40 Gb/s.

Un exemple de dispositif de stockage NVMe est illustré ici.

Implémentation d'un contrôleur hôte NVMe sur le ZCU102

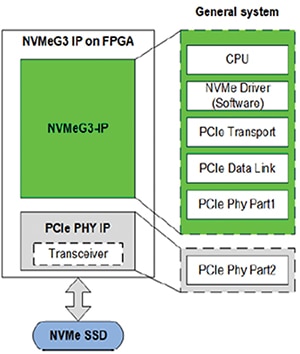

Figure 2 : Implémentation NVMe. (Source de l'image : Design Gateway)

Figure 2 : Implémentation NVMe. (Source de l'image : Design Gateway)

Traditionnellement, l'hôte NVMe est implémenté en utilisant un processeur hôte fonctionnant avec un contrôleur PCIe pour le transfert de données vers et depuis le SSD NVMe. Le protocole NVMe est implémenté pour les communications des pilotes des dispositifs, le périphérique de processeur matériel du contrôleur PCIe étant connecté au moyen d'un bus haute vitesse. Une mémoire DDR externe est requise pour la mise en mémoire tampon des données et la file d'attente des commandes pour transférer les données entre le contrôleur PCIe et le SSD.

Étant donné que le bloc intégré PCIe Gen3 n'est pas disponible sur le dispositif FPGA XCZU9EG-2FFVB1156E du ZCU102, une approche d'implémentation conventionnelle n'est pas possible.

Design Gateway propose une solution en utilisant le bloc NVMeG3-IP (comme illustré à la Figure 2) afin d'activer l'interface SSD NVMe pour un dispositif MPSoC Zynq® UltraScale+™ ne disposant d'aucun bloc intégré PCIe. L'interface NVMe du ZCU102 permet de construire un système RAID à plusieurs canaux offrant de très hautes performances et une consommation en ressources FPGA la plus basse possible. La licence du bloc NVMeG3-IP inclut une conception de référence d'exemple qui permet aux concepteurs de réduire les délais et les coûts de développement.

Présentation du bloc NVMeG3-IP de Design Gateway

Le bloc IP NVMe avec IP logicielle PCIe Gen3 (NVMeG3-IP) est idéal pour accéder à un SSD NVMe sans bloc intégré PCIe, et sans processeur ni mémoire externe. Le NVMeG3-IP inclut une IP logicielle PCIe Gen3 et une mémoire de 256 Ko. Cette solution est recommandée pour une application exigeant un stockage SSD NVMe avec des performances ultrarapides, avec un FPGA économique n'incluant pas de bloc intégré PCIe.

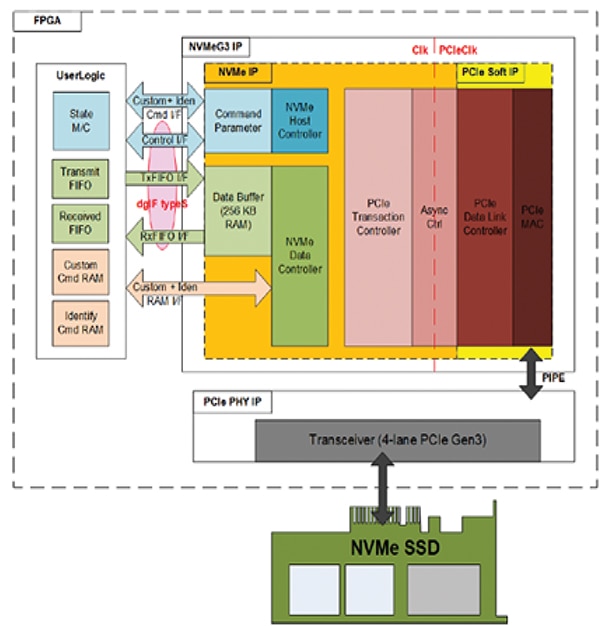

Figure 3 : Schéma fonctionnel du NVMeG3-IP. (Source de l'image : Design Gateway)

Figure 3 : Schéma fonctionnel du NVMeG3-IP. (Source de l'image : Design Gateway)

Fonctionnalités du NVMeG3-IP

Le NVMeG3-IP offre de nombreuses fonctionnalités, notamment :

- Implémentation d'une couche application, d'une couche transaction, d'une couche liaison de données et de quelques parties de la couche physique afin d'accéder au SSD NVMe sans avoir recours au processeur.

- Fonctionnement avec Xilinx PCIe PHY IP configuré en tant que PCIe Gen3 à 4 voies (interface bus de 128 bits)

- Tampon de données RAM de 256 Ko inclus

- Interface utilisateur simple via dgIF typeS

- Prise en charge de six commandes, c'est-à-dire identification, arrêt, écriture, lecture, SMART et Flush (prise en charge de commandes supplémentaires en option)

- Dispositif NVMe pris en charge :

- Code de catégorie de base : 01h (stockage de masse), code de sous-catégorie : 08h (non volatile), interface de programmation : 02h (NVMHCI)

- MPSMIN (taille de page de mémoire minimum) : 0 (4 Ko)

- MDTS (taille de transfert de données maximum) : au moins 5 (128 Ko) ou 0 (aucune limitation)

- Unité LBA : 512 ou 4096 octets

- La fréquence de l'horloge utilisateur doit être supérieure ou égale à celle de l'horloge PCIe (250 MHz pour Gen3)

- Conception de référence disponible :

- ZCU102 avec carte d'adaptateur AB17-M2FMC

- KCU105 avec carte d'adaptateur AB18-PCIeX16/AB16-PCIeXOVR

- VCU118 avec carte d'adaptateur AB18-PCIeX16

Design Gateway a développé le NVMeG3-IP pour qu'il fonctionne comme un contrôleur hôte NVMe pour l'accès à un SSD NVMe. L'interface utilisateur et les fonctionnalités standard sont conçues pour être simples à utiliser sans avoir besoin de connaître le protocole NVMe. La fonctionnalité supplémentaire du NVMeG3-IP est l'IP logicielle PCIe intégrée qui implémente la couche liaison de données et quelques parties de la couche physique du protocole PCIe par logique pure. Ainsi, le NVMeG3-IP peut fonctionner dans un FPGA, qui n'inclut pas de bloc intégré PCIe, en utilisant l'IP logicielle PCIe intégrée et le bloc Xilinx PCIe PHY IP. Xilinx PCIe PHY IP est un bloc de propriété intellectuelle libre de droits incluant un émetteur-récepteur et un égaliseur logique.

Le NVMeG3-IP prend en charge six commandes NVMe, c'est-à-dire identification, arrêt, écriture, lecture et SMART et Flush. Une mémoire BlockRAM de 256 Ko est intégrée dans le NVMeG3-IP pour agir en tant que tampon de données. Le système ne requiert pas de processeur ni de mémoire externe. Pour plus d'informations, consultez la fiche technique du NVMeG3-IP, téléchargeable sur notre site Web.

Les utilisations des ressources FPGA du dispositif FPGA XCZU9EG-2FFVB1156E sont illustrées dans le Tableau 1 ci-dessous.

|

Tableau 1 : Statistiques d'implémentation d'exemple pour les dispositifs Ultrascale/Ultrascale+

Implémentation et résultats de performances du ZCU102

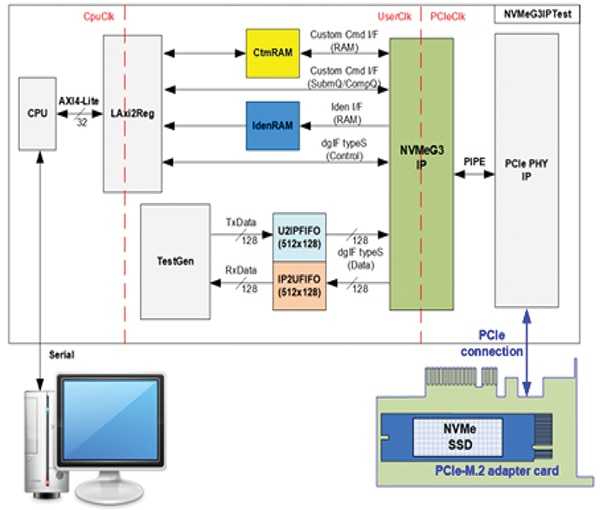

La Figure 4 illustre la vue d'ensemble de la conception de référence basée sur le ZCU102 pour démontrer le fonctionnement du NVMeG3-IP. Le module NVMeG3IPTest du système de démonstration inclut les modules suivants : TestGen, LAxi2Reg, CtmRAM, IdenRAM et FIFO.

Pour plus de détails sur la conception de référence NVMeG3-IP, veuillez consulter le document de conception de référence NVMeG3-IP fourni sur le site Web de Design Gateway.

Figure 4 : Vue d'ensemble de la conception de référence NVMeG3-IP. (Source de l'image : Design Gateway)

Figure 4 : Vue d'ensemble de la conception de référence NVMeG3-IP. (Source de l'image : Design Gateway)

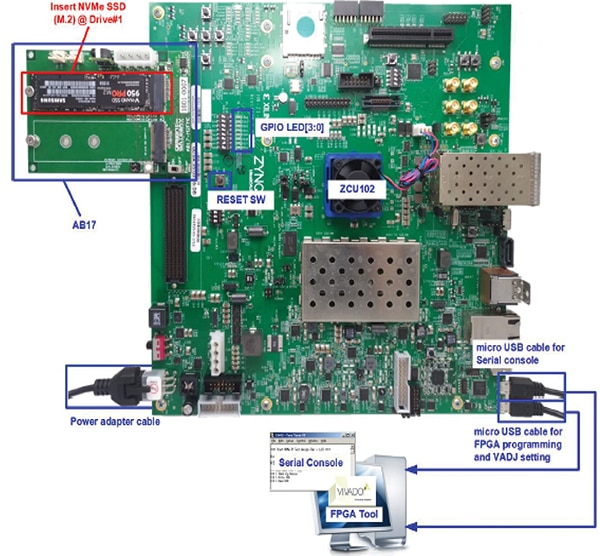

Le système de démonstration est conçu pour écrire/vérifier des données avec le SSD NVMe sur le ZCU102. L'utilisateur contrôle le fonctionnement de test à l'aide d'une console série. Pour que le SSD NVMe interface avec le ZCU102, une carte d'adaptateur AB17-M2FMC est requise, comme illustré à la Figure 5.

Figure 5 : Environnement de démonstration NVMeG3-IP installé sur le ZCU102. (Source de l'image : Design Gateway)

Figure 5 : Environnement de démonstration NVMeG3-IP installé sur le ZCU102. (Source de l'image : Design Gateway)

La Figure 6 illustre un exemple de résultat de test d'exécution du système de démonstration sur le ZCU102 en utilisant le SSD Samsung 970 Pro 512 Go.

Figure 6 : Performances de lecture/écriture du SSD NVMe sur le ZCU102 en utilisant le SSD Samsung 970 PRO S. (Source de l'image : Design Gateway)

Figure 6 : Performances de lecture/écriture du SSD NVMe sur le ZCU102 en utilisant le SSD Samsung 970 PRO S. (Source de l'image : Design Gateway)

Conclusion

Le bloc NVMeG3-IP fournit une solution pour activer l'interface SSD NVMe avec le kit d'évaluation ZCU102, et offre également une solution pour la gamme de dispositifs Zynq® UltraScale+™ MPSoC de Xilinx® lorsqu'aucun bloc intégré PCIe n'est disponible. Le NVMeG3-IP a été conçu avec l'objectif d'atteindre les performances les plus élevées avec la plus faible utilisation possible des ressources FPGA pour un accès au SSD NVMe sans processeur. Il convient parfaitement à un stockage NVMe hautes performances sans l'intervention d'un processeur et il est capable d'implémenter plusieurs interfaces SSD NVMe en utilisant des émetteurs-récepteurs GTH sans limites concernant le nombre de blocs intégrés PCIe disponibles sur le dispositif FPGA.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.