Comment évaluer et utiliser des tampons d'horloge à retard nul pour protéger la temporisation dans des systèmes numériques synchrones

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-07-18

Avec l'augmentation des performances des systèmes numériques, les concepteurs doivent faire de plus en plus attention à la conception des circuits de génération et de distribution d'horloge pour éviter les différences ou les incertitudes dans la temporisation de distribution d'horloge. Ces problèmes peuvent dégrader les performances du système, réduire les marges de temporisation ou provoquer des erreurs fonctionnelles. Pour éviter les problèmes associés à un décalage de temporisation, les concepteurs peuvent utiliser des tampons d'horloge à retard nul.

Les systèmes numériques synchrones typiques utilisent une horloge commune pour maintenir les opérations en séquence. Cette horloge doit être distribuée à tous les éléments séquentiels pour maintenir le fonctionnement du système à la fréquence souhaitée, souvent à l'aide d'un système en boucle fermée pour réduire le décalage de temporisation. Les tampons d'horloge à retard nul utilisent des boucles à verrouillage de phase (PLL) pour garantir que les sorties d'horloge en tampon sont alignées avec l'entrée d'horloge de référence, assurant ainsi une temporisation d'horloge presque parfaite.

Cet article décrit les tampons d'horloge à retard nul, explique comment ils fonctionnent en utilisant des solutions d'exemple de Cypress Semiconductor, d'Integrated Device Technology Inc. (IDT) et d'ON Semiconductor, et décrit en détail comment contrôler un décalage d'horloge. Il analyse également les méthodes de test pour garantir la stabilité de ces dispositifs.

Décalage d'horloge

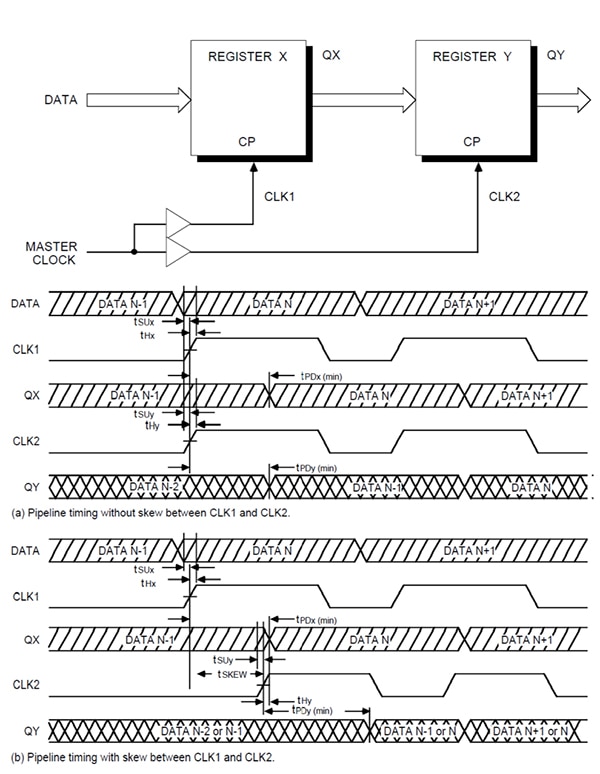

Dans les systèmes numériques synchrones, les horloges peuvent arriver à des moments différents au niveau des différents composants du circuit, ce qui provoque un décalage d'horloge. Le décalage d'horloge peut réduire les marges de temporisation et provoquer une défaillance du système (Figure 1).

Figure 1 : Exemple simple illustrant les impacts qu'un décalage d'horloge peut avoir sur les opérations d'un registre à chevauchement. Une horloge décalée peut enfreindre les exigences de configuration et/ou de maintien, ce qui entraîne un état de sortie indéterminé. (Source de l'image : IDT)

Figure 1 : Exemple simple illustrant les impacts qu'un décalage d'horloge peut avoir sur les opérations d'un registre à chevauchement. Une horloge décalée peut enfreindre les exigences de configuration et/ou de maintien, ce qui entraîne un état de sortie indéterminé. (Source de l'image : IDT)

Prenons un système synchrone simple composé de deux registres. Les données se chevauchent dans les registres : la sortie du registre X, QX, est l'entrée du registre Y. Les horloges, désignées CLK1 et CLK2, sont transférées aux registres via des tampons indépendants. S'il n'existe aucun décalage entre les horloges, comme dans le schéma (a), l'état N des données, qui est conforme aux exigences de configuration du registre (tSUx) et de temps de maintien (tHx), est cadencé dans la sortie de registre X (QX) lors du premier front d'horloge après le temps de propagation du registre. Le même front d'horloge sur CLK2 entraîne la lecture de l'état précédent de QX(N-1) par le registre, puis son apparition sur la sortie QY après le temps de propagation du registre.

En cas de décalage temporel entre CLK1 et CLK2, comme dans le schéma (b), l'état de QX peut être en transition lorsque CLK2 se produit. L'entrée du registre Y peut ne pas satisfaire aux exigences de configuration ou de temps de maintien du registre, et la sortie peut être indéterminée et provoquer une erreur.

Pour garantir un décalage d'horloge minimal, les concepteurs font correspondre les longueurs de pistes du circuit imprimé, sélectionnent des tampons et autres composants d'horloge avec des temps de propagation similaires, et équilibrent la charge sur les diverses sources d'horloge. Si ces techniques peuvent aider, il faut généralement utiliser des tampons d'horloge à retard nul pour pouvoir bien contrôler le décalage d'horloge.

Contrôle du décalage d'horloge

Un décalage d'horloge peut avoir plusieurs sources possibles. Les plus évidentes sont les signaux d'horloge acheminés via des interconnexions du circuit imprimé de diverses longueurs. D'autres sources de décalage incluent des horloges qui passent par différents dispositifs actifs avec différents temps de propagation, des tampons d'horloge avec des charges différentes ou des différences de température dans les tampons. Si certains de ces effets peuvent être contrôlés, les concepteurs utilisent souvent des dispositifs actifs pour resynchroniser les horloges avec une horloge de référence à l'aide de PLL.

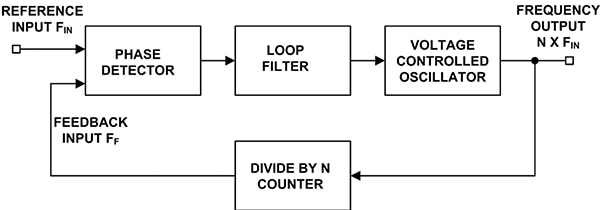

Les circuits PLL sont utilisés pour le contrôle de la fréquence et de la phase. Ils peuvent être configurés en tant que multiplicateurs de fréquence, démodulateurs, générateurs de suivi ou circuits d'extraction du signal d'horloge. Chacune de ces applications demande différentes caractéristiques. Cependant, elles utilisent toutes le même concept de circuit de base illustré à la Figure 2.

Figure 2 : Schéma fonctionnel d'une PLL configurée en tant que multiplicateur de fréquence. Il s'agit en fait d'un système de commande à rétroaction qui contrôle la phase d'un oscillateur commandé en tension (VCO). (Source de l'image : DigiKey Electronics)

Figure 2 : Schéma fonctionnel d'une PLL configurée en tant que multiplicateur de fréquence. Il s'agit en fait d'un système de commande à rétroaction qui contrôle la phase d'un oscillateur commandé en tension (VCO). (Source de l'image : DigiKey Electronics)

La Figure 2 montre le schéma fonctionnel d'une PLL de base configurée en tant que multiplicateur de fréquence. Le fonctionnement de ce circuit est représentatif de toutes les PLL. Il s'agit en fait d'un système de commande à rétroaction qui contrôle la phase d'un oscillateur commandé en tension (VCO). Le signal d'entrée est appliqué à une entrée d'un détecteur de phase. L'autre entrée est un signal de rétroaction provenant de la sortie d'un compteur de division par N. Normalement, les fréquences des deux signaux sont pratiquement identiques.

La sortie du détecteur de phase est une tension proportionnelle à la différence de phase entre les deux entrées. Ce signal est appliqué au filtre à boucle. C'est le filtre à boucle qui détermine les caractéristiques dynamiques de la PLL. Le signal filtré contrôle le VCO. Notez que la sortie du VCO présente une fréquence qui correspond à N fois l'entrée fournie à l'entrée de référence de fréquence (FIN). Le signal de sortie est renvoyé au détecteur de phase via le compteur de division par N.

Normalement, le filtre à boucle est conçu pour correspondre aux caractéristiques requises par l'application de la PLL. Si la PLL doit acquérir et suivre un signal, la bande passante du filtre à boucle est supérieure à celle nécessaire avec une fréquence d'entrée fixe. La plage de fréquences que la PLL accepte et sur laquelle elle se verrouille est appelée la plage de capture. Une fois que la PLL est verrouillée et suit un signal, la plage de fréquences qu'elle suit est appelée la plage de suivi. Généralement, la gamme de suivi est plus étendue que la gamme de capture. Le filtre à boucle de la PLL détermine également la vitesse à laquelle la fréquence du signal peut changer tout en maintenant le verrouillage. Il s'agit de la vitesse de balayage maximum. Plus la bande passante du filtre à boucle est étroite, plus l'erreur de phase pouvant être générée est petite. Cela se fait aux dépens d'une réponse plus lente et d'une gamme de capture réduite. Les PLL utilisées dans les applications d'horloge fonctionnent essentiellement à des fréquences fixes.

Tampons d'horloge à retard nul

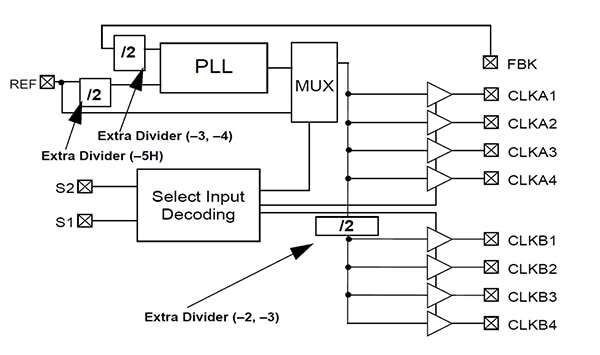

Un tampon d'horloge à retard nul est un dispositif qui peut mettre en tampon un signal d'horloge, en produisant plusieurs sorties d'horloge à partir d'une seule entrée d'horloge de référence. Les différentes sorties d'horloge mises en tampon présentent un retard réduit ou nul par rapport à l'entrée d'horloge de référence et un faible décalage entre elles. Le schéma fonctionnel simplifié d'un tampon à retard nul CY2308SXC-3T de Cypress Semiconductor est illustré à la Figure 3.

Figure 3 : Le tampon à retard nul à huit sorties CY2308SXC-3T utilise une PLL pour synchroniser toutes les sorties avec un décalage temporel proche de zéro. (Source de l'image : Cypress Semiconductor)

Figure 3 : Le tampon à retard nul à huit sorties CY2308SXC-3T utilise une PLL pour synchroniser toutes les sorties avec un décalage temporel proche de zéro. (Source de l'image : Cypress Semiconductor)

Un tampon à retard nul est conçu avec une PLL intégrée qui accepte une entrée de référence (REF) et une entrée de rétroaction (FBK) en tant qu'entrées de son détecteur de phase. L'entrée de rétroaction est commandée par l'une des sorties sélectionnées par l'utilisateur. Le détecteur de phase interne de la PLL ajuste la phase de sortie du VCO de sorte que ses deux entrées ne présentent aucune différence de phase ou de fréquence. L'une des sorties d'horloge mises en tampon, accompagnée de sa charge, est sélectionnée pour être le signal de rétroaction vers la PLL via le détecteur de phase. Quels que soient les changements de charge au niveau de cette sortie, la PLL les compense de manière dynamique, ce qui entraîne un retard nul de l'entrée vers la sortie de rétroaction, peu importe la charge de sortie.

La gamme CY2308 présente deux rangées de quatre sorties, qui fonctionnent sur une plage de fréquences de 10 à 133 mégahertz (MHz). Le décalage temporel de l'entrée à la sortie est inférieur à 250 picosecondes (ps) et le décalage d'horloge entre les sorties est inférieur à 200 ps. Le décalage temporel de l'entrée à la sortie est ajustable en changeant la capacité de charge au niveau de la sortie utilisée pour l'entrée de rétroaction.

La gamme de produits offre plusieurs configurations de diviseur par deux. Le composant sélectionné est la variante « -3 » qui a deux diviseurs de ce type, comme sur le schéma fonctionnel. Cette configuration permet à l'utilisateur d'obtenir des sorties équivalentes à deux ou quatre fois la fréquence d'entrée d'horloge de référence.

Le tampon à retard nul le plus couramment utilisé est configuré avec cinq sorties et est disponible auprès de plusieurs fabricants différents. Le CY2305SXI-1HT de Cypress Semiconductor, le 2305-1DCGI8 d'IDT et le NB2305AI1HDR2G d'ON Semiconductor sont des dispositifs très similaires. Ils sont tous équipés de cinq sorties d'horloge mises en tampon, d'un port CLKOUT simple et d'une quadruple rangée de sorties d'horloge. Contrairement au CY2308, le point de rétroaction de la PLL est fixe au niveau du signal CLKOUT simple.

Dynamique d'un tampon à retard nul

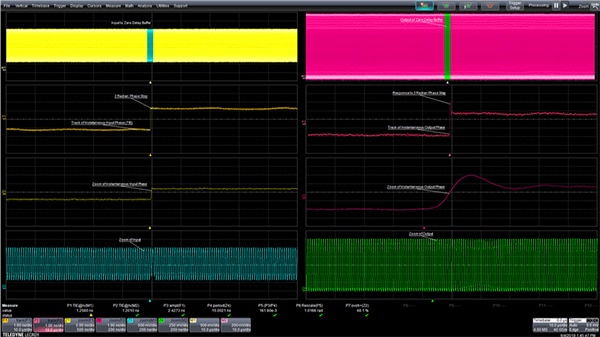

Les PLL dans les tampons à retard nul sont en fait des systèmes de contrôle à rétroaction. La dynamique est contrôlée par le filtre à boucle de la PLL. Comme pour n'importe quel système de commande, il est important d'évaluer la dynamique de la boucle de rétroaction en réponse à une entrée transitoire. Pour ce faire, une méthode consiste à appliquer une entrée avec un changement d'échelon pour évaluer la réponse à un échelon (Figure 4).

Figure 4 : Évaluation de la réponse à un échelon du tampon à retard nul CY2305 à l'aide d'un échelon de phase à 1 radian à 66,67 MHz. La représentation en haut à gauche correspond au signal d'entrée tandis que la représentation en haut à droite correspond à la sortie. (Source de l'image : DigiKey Electronics)

Figure 4 : Évaluation de la réponse à un échelon du tampon à retard nul CY2305 à l'aide d'un échelon de phase à 1 radian à 66,67 MHz. La représentation en haut à gauche correspond au signal d'entrée tandis que la représentation en haut à droite correspond à la sortie. (Source de l'image : DigiKey Electronics)

Le signal d'entrée est un signal sinusoïdal de 66,67 MHz avec un échelon d'un radian au centre de la fenêtre de signaux acquis. Cette forme d'onde a été générée par un générateur de formes d'ondes arbitraire (AWG). L'entrée et la sortie du tampon à retard nul CY2305 ont été acquises à l'aide d'un oscilloscope avec un paramètre de base temporelle de 10 microsecondes (µs) par division.

La représentation en haut à gauche de la Figure 4 correspond au signal d'entrée tandis que la représentation en haut à droite correspond à la sortie. L'erreur d'intervalle de temps (TIE) est la différence de temps du front d'horloge mesuré par rapport à sa position idéale. Elle est mesurée pour chaque forme d'onde. Dans l'absolu, il s'agit de la phase instantanée du signal référencé à une fréquence d'horloge fixe, qui est ici de 66,67 MHz. Les valeurs TIE pour chaque cycle d'horloge de l'entrée et de la sortie sont représentées en tant que forme d'onde appelée « piste TIE ». La piste d'entrée est la deuxième représentation en haut à gauche. Ici, l'échelon de la phase est visible avec une amplitude de 2,4 nanosecondes (ns). Cette valeur représente un décalage de phase d'un radian pour la fréquence d'horloge de 66,67 MHz.

La deuxième représentation en haut à droite est la piste TIE de la sortie. La piste de sortie montre quelques dépassements avant de se stabiliser à une nouvelle valeur moyenne adaptée au changement d'entrée. La troisième représentation montre un gros plan horizontal de la piste d'entrée (à gauche) et de la piste de sortie (à droite). Les détails de l'échelon d'entrée montrent une transition nette.

Le zoom sur la sortie montre quelques dépassements avant une rapide stabilisation à une nouvelle valeur moyenne en environ un cycle d'une durée approximative de 500 ns. Il s'agit d'une réponse à un échelon correcte pour un si grand échelon de phase. La stabilisation se fait rapidement et il n'y a aucun signe de réponse oscillatoire instable.

Les deux représentations du bas montrent des vues agrandies horizontalement de l'entrée (à gauche) et de la sortie (à droite). Le grand échelon de phase est clairement visible au niveau de l'entrée, mais la réponse de sortie lente est moins visible à cette échelle temporelle.

Conclusion

Les concepteurs de systèmes numériques hautes performances doivent continuer à porter une grande attention à la conception des circuits de génération et de distribution d'horloge afin d'éviter les différences ou les incertitudes dans la temporisation de la distribution d'horloge. Ces problèmes peuvent dégrader les performances du système, réduire les marges de temporisation ou provoquer des erreurs fonctionnelles.

Comme indiqué ici, le tampon à retard nul est un bon outil pour un contrôle actif lors de la propagation de plusieurs signaux d'horloge et du maintien de la synchronisation avec un signal d'horloge de référence. Il permet un excellent suivi, même avec des changements de charge importants au niveau de la sortie détectée. Cependant, comme démontré, les concepteurs doivent évaluer soigneusement la dynamique de la boucle de rétroaction d'un tampon à retard nul pour s'assurer que le tampon répond bien aux exigences de l'application.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.