Utiliser des SoC FPGA pour les systèmes temps réel critiques connectés et sécurisés

Avec la contribution de Rédacteurs nord-américains de DigiKey

2023-02-16

Les réseaux de portes programmables par l'utilisateur (FPGA), les sous-systèmes de microcontrôleurs RISC-V compatibles avec Linux, les architectures de mémoire avancées et les interfaces de communication hautes performances sont des outils importants pour les concepteurs. Cela est particulièrement vrai pour les concepteurs de systèmes connectés sécurisés, de systèmes critiques en termes de sécurité et d'un large éventail de systèmes déterministes temps réel critiques, comme l'intelligence artificielle (IA) et l'apprentissage automatique (ML).

Cependant, l'intégration de ces divers éléments dans un système sécurisé, connecté et déterministe peut s'avérer être une activité difficile et fastidieuse, tout comme la configuration des interconnexions haute vitesse pour les divers éléments du système. Les concepteurs doivent inclure une unité de gestion de la mémoire, une unité de protection de la mémoire, une capacité de démarrage sécurisé et des émetteurs-récepteurs de classe gigabit pour une connectivité haute vitesse. La conception requiert une gestion de l'alimentation active et statique et le contrôle des courants d'appel. Certaines conceptions nécessitent un fonctionnement sur la plage de températures commerciales étendue, de 0°C à +100°C de température de jonction (TJ), tandis que les systèmes en environnements industriels doivent fonctionner avec une valeur TJ de -40°C à +100°C.

Pour relever ces défis et d'autres encore, les concepteurs peuvent se tourner vers les systèmes sur puce (SoC) FPGA qui offrent une combinaison de basse consommation d'énergie, de rendement thermique et de sécurité de niveau défense pour les systèmes intelligents, connectés et déterministes.

Cet article examine l'architecture d'un tel SoC FPGA et la manière dont il prend en charge le développement efficace de systèmes connectés et déterministes. Il présente ensuite brièvement le benchmark EEMBC CoreMark-Pro, qui compare la puissance de traitement à la consommation d'énergie, et donne un aperçu des performances de référence d'un SoC FPGA représentatif. Il étudie la manière dont la sécurité est intégrée dans ces SoC FPGA et présente des exemples de SoC FPGA de Microchip Technology, ainsi qu'une plateforme de développement pour accélérer le processus de conception. Il conclut par une courte liste de cartes d'extension de MikroElektronika qui peuvent être utilisées pour implémenter une série d'interfaces de communication ainsi que des fonctions de localisation GNSS (système global de navigation par satellite).

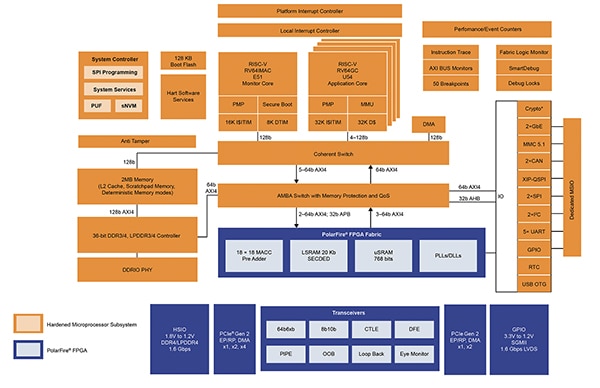

SoC avec structure FPGA

La puce de ce SoC est une structure FPGA qui contient les éléments du système, du FPGA au sous-système de microcontrôleur RISC-V construit avec la logique FPGA renforcée. Le sous-système de microcontrôleur comprend un cluster de microcontrôleurs RISC-V à quatre cœurs, un cœur de moniteur RISC-V, un contrôleur de système et un sous-système de mémoire déterministe de niveau 2 (L2). Le FPGA dans ces SoC inclut jusqu'à 460 K éléments logiques, des émetteurs-récepteurs jusqu'à 12,7 gigabits par seconde (Gbps) et d'autres blocs entrée/sortie (E/S), notamment des E/S à usage général (GPIO) et Peripheral Component Interconnect Express (PCIe) 2. L'architecture globale est conçue pour être fiable. Elle inclut la correction d'erreur simple et la détection d'erreur double (SECDED) sur toutes les mémoires, l'analyse de puissance différentielle (DPA), la protection de mémoire physique et 128 kilobits (Kb) de mémoire de démarrage Flash (Figure 1).

Figure 1 : Tous les éléments dans ce SoC FPGA, y compris les sous-systèmes RISC-V, sont implémentés sur la structure FPGA. (Source de l'image : Microchip Technology)

Figure 1 : Tous les éléments dans ce SoC FPGA, y compris les sous-systèmes RISC-V, sont implémentés sur la structure FPGA. (Source de l'image : Microchip Technology)

Microchip propose son écosystème Mi-V, composé de ressources de conception et d'outils tiers, pour prendre en charge l'implémentation de systèmes RISC-V. Il est conçu pour accélérer l'adoption de l'architecture de jeu d'instructions (ISA) RISC-V pour les cœurs RISC-V renforcés et pour les cœurs logiciels RISC-V. Les éléments de l'écosystème Mi-V incluent l'accès aux éléments suivants :

- Licences de propriété intellectuelle (IP)

- Matériel

- Systèmes d'exploitation et intergiciels

- Débogueurs, compilateurs et services de conception

Les microcontrôleurs RISC-V renforcés du SoC FPGA incluent plusieurs capacités de débogage, comme l'interface AXI (Advanced Extensible Interface) configurable en cours d'exécution et le suivi des instructions. L'interface AXI permet aux concepteurs de surveiller les données écrites ou lues dans diverses mémoires et de savoir quand elles sont écrites ou lues.

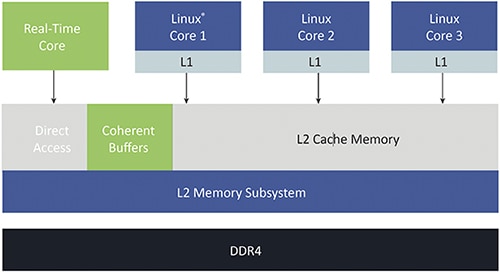

Le sous-système de microcontrôleur RISC-V utilise un pipeline à cinq étages, à émission unique d'instructions (single-issue) et dans l'ordre. Il n'est pas vulnérable aux failles Spectre ou Meltdown qui peuvent affecter les architectures dans le désordre. Les cinq microcontrôleurs sont cohérents avec le sous-système de mémoire, prenant en charge un mélange de systèmes temps réel en mode de multitraitement asymétrique (AMP) déterministe et Linux. Les capacités du sous-système RISC-V incluent (Figure 2) :

- Exécution d'opérations en temps réel critique et Linux

- Configuration de L1 et L2 en tant que mémoire déterministe

- Sous-système de mémoire DDR4

- Désactiver/activer la prédiction de branchement

- Opération pipeline dans l'ordre

Figure 2 : Le sous-système RISC-V comprend plusieurs éléments de processeur et de mémoire. (Source de l'image : Microchip Technology)

Figure 2 : Le sous-système RISC-V comprend plusieurs éléments de processeur et de mémoire. (Source de l'image : Microchip Technology)

Plus de traitement avec moins d'énergie

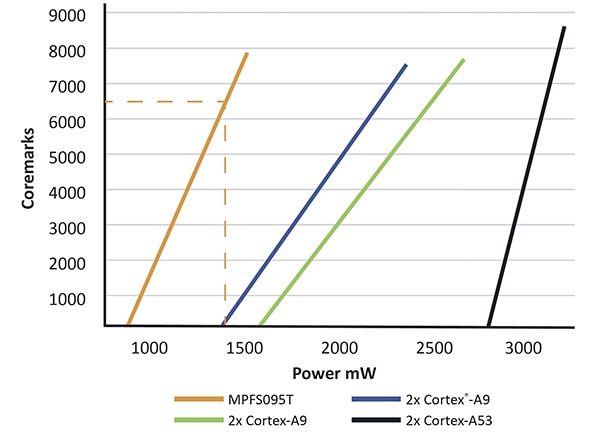

Outre leurs avantages en termes de fonctionnement système, notamment la prise en charge du traitement temps réel critique, ces SoC FPGA sont hautement écoénergétiques. Le benchmark EEMBC CoreMark-PRO est une norme industrielle pour la comparaison du rendement et des performances des microcontrôleurs dans les systèmes embarqués. Il a été conçu spécifiquement pour évaluer les performances du matériel et pour remplacer le benchmark Dhrystone.

Les charges de travail CoreMark-PRO incluent une diversité de caractéristiques de performances, de parallélisme au niveau des instructions et d'utilisation de la mémoire, sur la base de quatre charges de travail à virgule flottante et de cinq charges de travail à nombre entier commun. Les charges de travail à virgule flottante comprennent une routine d'algèbre linéaire dérivée de LINPACK, une transformation de Fourier rapide, un algorithme de réseau neuronal pour l'évaluation des modèles, et une version améliorée du benchmark de boucles de Livermore. La compression JPEG, un analyseur XML, la compression ZIP et un algorithme de hachage sécurisé 256 bits (SHA-256) constituent la base des charges de travail à nombre entier.

Les modèles MPFS095T de ces SoC FPGA, comme le MPFS095TL-FCSG536E, peuvent fournir jusqu'à 6500 Coremarks à 1,3 watt (W) (Figure 3).

Figure 3 : Le SoC FPGA MPFS095T (ligne orange) fournit 6500 Coremarks à 1,3 W. (Source de l'image : Microchip Technology)

Figure 3 : Le SoC FPGA MPFS095T (ligne orange) fournit 6500 Coremarks à 1,3 W. (Source de l'image : Microchip Technology)

Considérations relatives à la sécurité

Les applications critiques en termes de sécurité et temps réel critiques pour ces SoC FPGA exigent une forte sécurité en plus d'un haut rendement énergétique et de puissantes capacités de traitement. Les fonctions de sécurité de base de ces SoC FPGA incluent la programmation de flux binaires sécurisés DPA, un générateur de nombres véritablement aléatoires (TRNG) et une fonction physique inclonable (PUF). Elles comprennent également un démarrage sécurisé standard et défini par l'utilisateur, une protection de la mémoire physique qui fournit des restrictions d'accès à la mémoire en fonction de l'état des privilèges de la machine, y compris les modes machine, superviseur ou utilisateur, et une immunité aux attaques Meltdown et Spectre.

La sécurité commence par une gestion sécurisée de la chaîne d'approvisionnement, notamment l'utilisation de modules de sécurité matériels (HSM) pendant le test et le conditionnement des plaquettes. L'utilisation d'un certificat FPGA x.509 numériquement signé de 768 octets, embarqué dans chaque SoC FPGA, renforce la sécurité de la chaîne d'approvisionnement.

Ces SoC FPGA intègrent de nombreux détecteurs de fraude sur la puce pour garantir un fonctionnement sûr et fiable. Si une altération est détectée, un indicateur de fraude est émis et permet au système de réagir en conséquence. Les détecteurs de fraude disponibles incluent :

- Moniteurs de tension

- Capteurs de température

- Détecteurs de fréquence d'horloge et de perturbation d'horloge

- Détecteur JTAG actif

- Détecteur Mesh actif

La sécurité est en outre garantie par des contre-mesures CPA de chiffrement par bloc symétrique AES-256, des capacités d'assimilation cryptographique intégrées pour garantir l'intégrité des données, une fonction PUF intégrée pour le stockage des clés et des capacités d'abrogation pour la structure FPGA et toutes les mémoires intégrées.

Exemples de SoC FPGA

Microchip Technology combine ces capacités et ces technologies dans ses SoC FPGA PolarFire, avec plusieurs niveaux de vitesse, caractéristiques de température et tailles de boîtiers, afin de répondre aux besoins des concepteurs pour un large éventail de solutions avec de 25 K à 460 K éléments logiques. Quatre classes de température sont disponibles (toutes répertoriées pour TJ), de 0°C à +100°C pour la plage commerciale étendue, de -40°C à +100°C pour la plage industrielle, de -40°C à +125°C pour la plage automobile et de -55°C à +125°C pour la plage militaire.

Les concepteurs peuvent choisir entre des dispositifs à niveau de vitesse standard et des dispositifs à niveau à vitesse -1 qui sont 15 % plus rapides. Ces SoC FPGA peuvent fonctionner à 1,0 volt (V) pour un fonctionnement à la puissance la plus faible, ou à 1,05 V pour des performances supérieures. Ils sont disponibles en différentes tailles de boîtiers, notamment 11 millimètres (mm) x 11 mm, 16 mm x 16 mm et 19 mm x 19 mm.

Pour les applications exigeant un fonctionnement à température commerciale étendue, un fonctionnement à vitesse standard et 254 K éléments logiques dans un boîtier de 19 mm x 19 mm, les concepteurs peuvent utiliser le MPFS250T-FCVG484EES. Pour les solutions plus simples qui nécessitent 23 K éléments logiques, les concepteurs peuvent se tourner vers le MPFS025T-FCVG484E, également doté d'un fonctionnement à température commerciale étendue et d'un niveau de vitesse standard dans un boîtier de 19 mm x 19 mm. Le MPFS250T-1FCSG536T2, avec 254 K éléments logiques, est conçu pour les systèmes automobiles hautes performances. Il présente une plage de températures de fonctionnement de -40°C à +125°C et un niveau de vitesse -1 pour une horloge 15 % plus rapide, dans un boîtier compact de 16 mm x 16 mm avec 536 billes sur un pas de 0,5 mm (Figure 4).

Figure 4 : Le MPFS250T-1FCSG536T2 pour systèmes automobiles est fourni en boîtier de 16 mm x 16 mm avec 536 billes et un pas de 0,5 mm. (Source de l'image : Microchip Technology)

Figure 4 : Le MPFS250T-1FCSG536T2 pour systèmes automobiles est fourni en boîtier de 16 mm x 16 mm avec 536 billes et un pas de 0,5 mm. (Source de l'image : Microchip Technology)

Plateforme de développement SoC FPGA

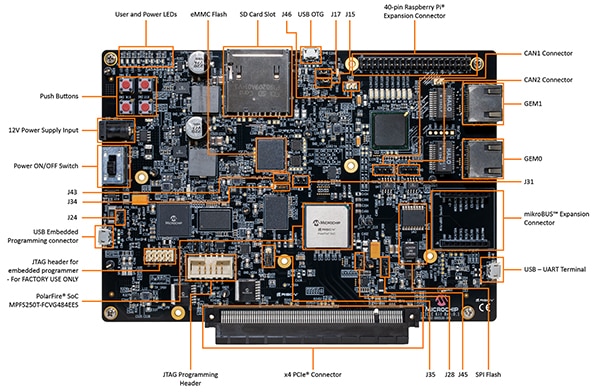

Pour accélérer la conception de systèmes avec le SoC FPGA PolarFire, Microchip propose le kit PolarFire SoC Icicle MPFS-ICICLE-KIT-ES qui permet d'explorer le sous-système de microprocesseur RISC-V compatible Linux à cinq cœurs, avec une exécution en temps réel, basse consommation. Le kit inclut une licence Libero Silver gratuite, nécessaire pour évaluer les conceptions. Il prend en charge les fonctionnalités de programmation et de débogage dans un seul langage.

Ces SoC FPGA sont pris en charge par le kit de développement logiciel (SDK) d'accélérateur VectorBlox, qui permet des applications IA/ML basse consommation en facteur de forme compact. L'accent est mis sur la simplification du processus de conception, de sorte que les concepteurs n'ont pas besoin d'avoir une expérience préalable en conception FPGA. Le SDK d'accélérateur VectorBlox permet aux développeurs de programmer des réseaux neuronaux écoénergétiques avec C/C++. Le kit Icicle présente de nombreuses fonctionnalités pour fournir un environnement de développement complet, y compris un système de capteur de puissance multi-rail pour surveiller les différents domaines de puissance, un port racine PCIe et des mémoires embarquées — y compris LPDDR4, QSPI et eMMC Flash — pour exécuter Linux et Raspberry Pi, et des ports d'extension mikroBUS pour une multitude d'options de connectivité filaire et sans fil, ainsi que des extensions fonctionnelles telles que la capacité de localisation GNSS (Figure 5).

Figure 5 : Cet environnement de développement SoC FPGA complet inclut des connecteurs pour les cartes d'extension Raspberry Pi (en haut à droite) et mikroBUS (en bas à droite). (Source de l'image : Microchip Technology)

Figure 5 : Cet environnement de développement SoC FPGA complet inclut des connecteurs pour les cartes d'extension Raspberry Pi (en haut à droite) et mikroBUS (en bas à droite). (Source de l'image : Microchip Technology)

Cartes d'extension

Voici quelques exemples de cartes d'extension mikroBUS :

MIKROE-986, pour ajouter la connectivité de bus CAN avec une interface périphérique série (SPI).

MIKROE-1582, pour l'interface entre le microcontrôleur et un bus RS-232.

MIKROE-989, pour la connexion avec un bus de communication RS422/485.

MIKROE-3144, pour la prise en charge des technologies LTE Cat M1 et NB1 permettant une connectivité simple et fiable avec les dispositifs IoT 3GPP.

MIKROE-2670, pour permettre la fonctionnalité GNSS avec réception simultanée des constellations GPS et Galileo, plus BeiDou ou GLONASS, résultant en une haute précision de positionnement dans les situations de faibles signaux ou d'interférences dans les canyons urbains.

Conclusion

Les concepteurs peuvent se tourner vers les SoC FPGA pour développer des systèmes déterministes critiques en termes de sécurité et temps réel critiques connectés. Les SoC FPGA fournissent un vaste choix d'éléments système, y compris une structure FPGA, un sous-système de microcontrôleur RISC-V avec des mémoires hautes performances, des interfaces de communication haute vitesse et de nombreuses fonctions de sécurité. Pour aider les concepteurs à démarrer, des cartes et des environnements de développement sont disponibles et incluent tous les éléments nécessaires, y compris des cartes d'extension qui peuvent être utilisées pour implémenter de nombreuses fonctions de communication et de localisation.

Lectures recommandées

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.