Tirer parti de l'I3C pour des communications plus rapides, plus simples et plus flexibles entre circuits intégrés

Avec la contribution de Rédacteurs nord-américains de DigiKey

2024-12-17

Les interfaces série embarquées pour les communications de circuit intégré à circuit intégré sont dominées par I²C (Inter-Integrated Circuit) et SPI (Serial Peripheral Interface), disponibles depuis les années 1980. Ces interfaces sont largement utilisées pour connecter des capteurs et des circuits intégrés basse vitesse à des microcontrôleurs (MCU) pour une communication intracarte sur de courtes distances. Cependant, à mesure que les systèmes numériques deviennent plus rapides, ces interfaces, limitées à des débits de données typiques de 1 mégabit par seconde (Mb/s) pour I²C et 10 Mb/s pour SPI, sont devenues un facteur restrictif. D'autres limitations, notamment les lignes d'activation de puce ou d'interruption dédiées, requièrent des connexions de signaux supplémentaires, augmentant le nombre de fils et la complexité des connexions de bus.

Le bus I3C (Improved Inter-Integrated Circuit) est destiné à améliorer les communications entre circuits intégrés. Il offre des débits de données plus élevés, une plus grande flexibilité et une véritable interface à deux fils avec des interruptions intrabandes (IBI) au lieu d'interruptions externes.

Cet article présente les caractéristiques de l'interface I3C et explique pourquoi elle peut constituer une bonne mise à niveau par rapport aux interfaces série I²C et SPI. Des microcontrôleurs, des commutateurs de circuit intégré et des capteurs typiques sont utilisés pour illustrer son application.

Bus de communication embarqués

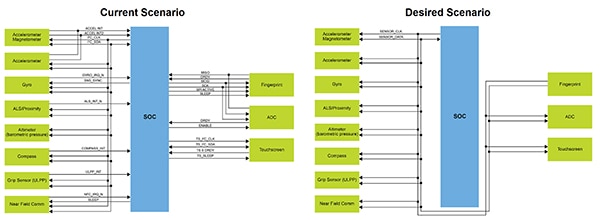

Les interconnexions série embarquées comme I²C et SPI sont employées depuis de nombreuses années pour les communications intracartes. Elles sont principalement utilisées comme bus de communication entre les capteurs et les dispositifs d'interface utilisateur et leurs processeurs de contrôle. Le nombre de capteurs dans les systèmes typiques est passé de dix à vingt dans les téléphones et à beaucoup plus dans les véhicules. Dans le même temps, les exigences en matière de communications sont devenues plus difficiles à satisfaire pour les concepteurs, car la demande en matière de vitesse plus élevée, de consommation d'énergie plus faible et de nombre réduit de conducteurs ne cesse d'augmenter. Les concepteurs doivent répondre à ces exigences tout en maintenant le contrôle du processeur via des interruptions et des lignes d'activation (Figure 1).

Figure 1 : Les communications embarquées doivent prendre en charge des vitesses plus élevées, une consommation d'énergie plus faible et un nombre minimal de fils. (Source de l'image : NXP Semiconductors)

Figure 1 : Les communications embarquées doivent prendre en charge des vitesses plus élevées, une consommation d'énergie plus faible et un nombre minimal de fils. (Source de l'image : NXP Semiconductors)

La technologie actuelle implémente l'interface du capteur et du dispositif de contrôle utilisateur à l'aide d'interfaces I²C à deux fils ou SPI à quatre fils. Les lignes d'interruption, d'activation et autres lignes de contrôle sont séparées des lignes d'horloge et de données, ce qui se traduit par un plus grand nombre de lignes par interface.

Les concepteurs ont besoin d'une approche d'interface plus avant-gardiste qui élimine ces conducteurs supplémentaires des interconnexions et gère ces opérations intrabandes en utilisant uniquement les lignes d'horloge et de données. De plus, le bus doit pouvoir fonctionner à des vitesses plus élevées et avec des pertes de puissance moindres.

Interface I3C

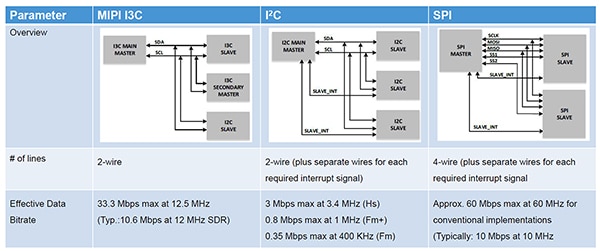

L'interface I3C a été développée par l'Alliance MIPI (Mobile Industry Processor Interface) pour répondre à ces exigences. L'interface est disponible à la fois en tant que MIPI I3C pour les membres MIPI et en tant que MIPI I3C Basic avec des fonctionnalités réduites pour les non-membres. Comme les anciennes interfaces I²C et SPI, la forme améliorée est sérielle et est implémentée à l'aide de deux fils pour minimiser le nombre de broches et le nombre de trajets de signaux entre les composants. Elle offre un débit de données atteignant 12,5 Mb/s avec une horloge de 12,5 mégahertz (MHz) en mode SDR (Single Data Rate). Elle fonctionne à des niveaux de puissance inférieurs et utilise une architecture de conception simple mais flexible.

En outre, la norme I3C conserve une rétrocompatibilité limitée avec le système I²C, ce qui permet aux périphériques I²C existants d'être connectés au bus I3C, tout en permettant au bus de passer à des débits de données plus élevés pour la communication entre les périphériques I3C compatibles. Une comparaison des configurations systèmes est présentée à la Figure 2.

Figure 2 : La comparaison des configurations de base des interfaces I3C, I²C et SPI montre la vitesse améliorée et le câblage plus simple de l'interface I3C. (Source de l'image : NXP Semiconductors)

Figure 2 : La comparaison des configurations de base des interfaces I3C, I²C et SPI montre la vitesse améliorée et le câblage plus simple de l'interface I3C. (Source de l'image : NXP Semiconductors)

L'interface SPI à quatre fils peut fonctionner plus rapidement et prend en charge la communication en duplex intégral. L'interface I²C communique en semi-duplex sur un bus à deux fils comprenant des lignes d'horloge (SCL) et de données (SDA). Les deux requièrent des lignes supplémentaires pour prendre en charge les interruptions et d'autres fonctions de contrôle telles que la sélection de puce. L'interface I3C réduit le nombre de fils utilisés dans l'interface à deux, éliminant ainsi les lignes d'interruption, d'activation et de sélection de puce distinctes utilisées dans I²C et SPI. Cette réduction du nombre de fils constitue un avantage significatif dans un système nécessitant dix à vingt capteurs individuels reliés au processeur, chacun avec plusieurs fils secondaires. Les interruptions et autres lignes de contrôle sont remplacées par des IBI. Dans cette méthode, un capteur ou un périphérique cible impose son adresse dans l'en-tête d'adresse du bus I3C pour notifier une interruption au processeur.

La différence de fréquences d'horloge entre I²C et I3C est significative. L'interface I²C est généralement cadencée à 100 kilohertz (kHz), 400 kHz ou 1 MHz, tandis que l'interface I3C peut être cadencée à 12,5 MHz. Auparavant, l'interface SPI était utilisée pour les fréquences d'horloge supérieures à 1 MHz. Le choix de la conception se faisait entre la fréquence d'horloge et le nombre de fils. L'interface I3C a changé les choses en offrant des fréquences d'horloge et des débits de données plus élevés avec une véritable topologie à deux fils.

Les sorties push-pull, qui peuvent commuter plus rapidement que les circuits d'attaque à drain ouvert ou à collecteur, contribuent de manière significative à l'augmentation de la fréquence d'horloge d'I3C. Pour maintenir la compatibilité avec les périphériques I²C, l'interface I3C peut basculer entre les circuits d'attaque à drain ouvert et push-pull en fonction de l'état du bus. La conception à drain ouvert ou à collecteur est utilisée lors de l'adressage initial ou de l'arbitrage, lorsque les périphériques I²C et I3C peuvent être simultanément sur la ligne. L'I3C utilise le mode push-pull lorsque la communication est unidirectionnelle et qu'il n'y a aucune possibilité de communication simultanée d'un périphérique I²C.

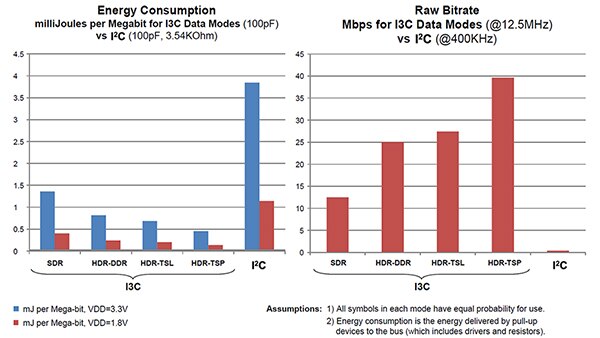

En plus du mode SDR standard, l'I3C prend en charge plusieurs modes HDR (High Data Rate) en option. Ces modes HDR fonctionnent avec la même fréquence d'horloge mais émettent avec une densité de données plus élevée. Le premier des modes HDR est HDR-DDR (HDR Double Data Rate), où les données sont cadencées sur les deux fronts du signal d'horloge, offrant ainsi un débit de données presque deux fois supérieur. Pour une horloge de 12,5 MHz, le mode DDR atteint un débit de données effectif de 20 Mb/s.

Les symboles ternaires HDR ont deux versions : symbole ternaire HDR, pur (HDR-TSP) pour les périphériques I3C uniquement, et symbole ternaire HDR, hérité (HDR-TSL) pour les bus incluant à la fois les périphériques I²C et I3C. Les modes de symboles ternaires atteignent trois bits de données par horloge en utilisant des symboles à trois bits (ternaires) codés sur les lignes SCL et SDA.

Le mode HDR-BT (HDR Bulk Transport) offre le plus haut volume de données en prenant en charge les communications sur des lignes de données SDA quadruples, doubles ou simples. Cela se traduit par des performances huit, quatre ou deux fois supérieures au débit de données simple à la même fréquence d'horloge.

Ces augmentations de la vitesse de transfert de données permettent aux périphériques d'être activés pendant une période plus courte, réduisant ainsi le rapport cyclique d'alimentation du bus. Cela réduit la consommation d'énergie par rapport à I²C (Figure 3). La transition de circuits d'attaque à collecteur ouvert avec résistances d'excursion haute externes à des circuits d'attaque push-pull réduit davantage la consommation d'énergie, car les résistances d'excursion haute nécessitent une puissance importante pour fonctionner.

Figure 3 : L'interface I3C offre des améliorations en termes de débit de données et de consommation d'énergie par rapport à I²C. (Source de l'image : NXP Semiconductors)

Figure 3 : L'interface I3C offre des améliorations en termes de débit de données et de consommation d'énergie par rapport à I²C. (Source de l'image : NXP Semiconductors)

Adressage

I²C utilise des adresses statiques d'une longueur de 7 ou 10 bits pour chaque périphérique de bus. Dans l'interface I3C, l'adressage statique a été remplacé par un adressage dynamique à 7 bits, où le maître du bus définit l'adresse du périphérique pendant l'attribution d'adresse dynamique (DAA) et la stocke dans un registre de périphériques. L'adressage statique, comme dans le cas d'un périphérique I²C, peut toujours être utilisé dans I3C.

Grâce à l'adressage dynamique, les adresses des périphériques peuvent être modifiées ultérieurement. Cela permet la connexion à chaud, qui permet d'ajouter un nouveau périphérique au bus pendant qu'il fonctionne. Le nouveau périphérique, connecté au bus I3C, signale sa présence au maître I3C en envoyant une demande de connexion à chaud. Le contrôleur maître reconnaît la demande et attribue une adresse pour ajouter le périphérique au bus.

IBI

I3C est un véritable bus à deux fils qui utilise des IBI au lieu de lignes d'interruption dédiées comme I²C. Les IBI se produisent lorsqu'un périphérique cible signale sa disponibilité au maître en abaissant la ligne SDA. Le maître démarre ensuite l'horloge sur la ligne SCL et le périphérique cible transmet son adresse sur le bus I3C pour avertir le contrôleur d'une interruption.

Codes de commande communs

Les codes de commande communs (CCC) sont des commandes standardisées que le contrôleur peut transmettre sous forme de diffusion générale à tous les périphériques I3C simultanément ou à un périphérique cible spécifique. Ces commandes concernent les éléments liés à la gestion des bus. Le format du protocole CCC commence par l'adresse de diffusion I3C, qui est reconnue par tous les périphériques I3C sur le bus. Tout périphérique I²C sur le bus n'accusera pas réception de la demande car il s'agit d'une adresse I²C réservée.

Chaque commande inclut un champ ID de descripteur de 8 bits et peut être suivie d'une charge utile de commande. Une commande envoyée à un périphérique spécifique transmet l'adresse du périphérique dans le premier octet de la charge utile. Il existe plus de quarante commandes CCC, y compris les suivantes :

- ENTDAA (Enter Dynamic Address Assignment)

- SETNEWDA (Set New Dynamic Address Assignment)

- ENEC (Enable Events)/DISEC (Disable Events )

- RSTDAA (Reset Dynamic Address Assignment)

- ENTHDRx (Enter High Data Rate Mode)

- GETDCR (Get Device Characteristics Register)

Les fournisseurs sont autorisés à utiliser une gamme dédiée d'ID CCC pour implémenter leurs propres commandes.

Détection d'erreurs et récupération

Contrairement à I²C, I3C inclut des dispositions pour la détection des erreurs et la récupération. Six méthodes d'erreur et de récupération pour les périphériques cibles sont obligatoires, et une autre est facultative. Des méthodes d'erreur et de récupération supplémentaires sont également disponibles spécifiquement pour les erreurs côté maître.

Composants pris en charge par I3C

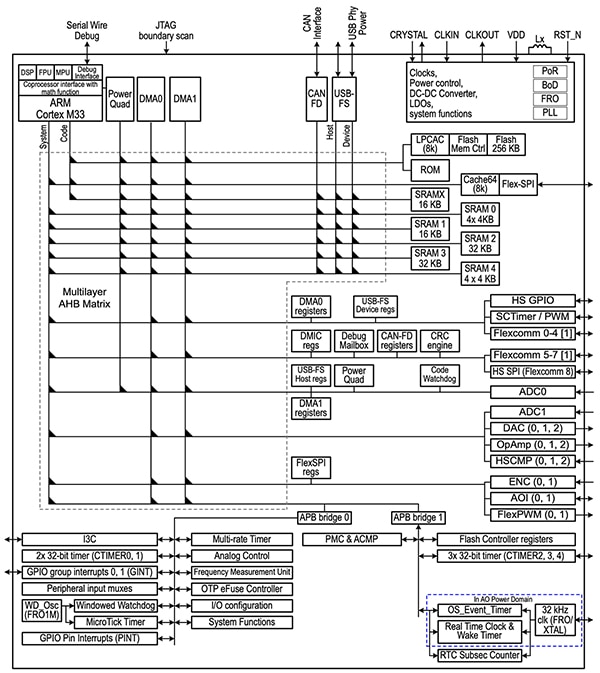

Comme illustré à la Figure 2 (à gauche), un réseau I3C de base comprend au moins un contrôleur maître et un ou plusieurs esclaves ou cibles I3C. Le maître principal peut être un microcontrôleur tel que le LPC5534JHI48-00MP de NXP Semiconductors (Figure 4). Il s'agit d'un microcontrôleur Arm® Cortex®-M33 32 bits avec 128 kilo-octets (Ko) de SRAM et 256 Ko de Flash. Son interface Flexcomm prend en charge huit interfaces série différentes, dont I3C.

Figure 4 : Le microcontrôleur LPC5534JHI48/00MP inclut une interface I3C et sept autres interfaces série. (Source de l'image : NXP Semiconductors)

Figure 4 : Le microcontrôleur LPC5534JHI48/00MP inclut une interface I3C et sept autres interfaces série. (Source de l'image : NXP Semiconductors)

Le bus I3C permet l'ajout de maîtres secondaires introduits sur le bus en tant qu'esclaves. L'I3C peut avoir plusieurs maîtres, mais un seul peut être le contrôleur. Une fois enregistré, le maître secondaire peut demander le statut de maître actuel, et si le maître actuel accepte, son contrôle est transféré au maître secondaire demandeur.

Le P3T2030CUKAZ de NXP est un capteur I3C typique. Ce capteur de température convertit les températures de -40°C à +125°C en une valeur numérique 12 bits avec une précision de ±2°C. Il inclut une interface série en mode SDR I²C et I3C.

Un capteur plus sophistiqué est le gyroscope et accéléromètre MEMS (microsystème électromécanique) à trois axes ICM-42605 de TDK InvenSense. En tant que gyroscope, il mesure les vitesses de rotation de ±15,2 à ±2000 degrés par seconde (°/s). Sa plage en tant qu'accéléromètre est de ±2 à ±15 g. Il détecte le mouvement, l'inclinaison, le contact ou les pas (podomètre). En tant que capteur I3C, il fonctionne à 12,5 MHz en mode SDR et à 25 MHz en mode DDR.

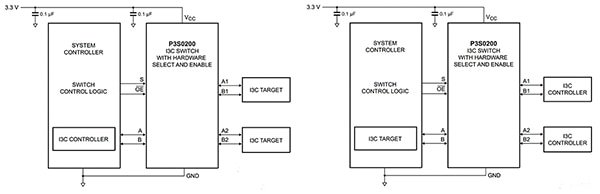

Des circuits intégrés tels que le commutateur I3C P3S0200GMX de NXP peuvent reconfigurer le bus I3C en routant les signaux de bus I3C entre un contrôleur I3C et plusieurs ensembles de périphériques cibles, ou entre une seule cible et plusieurs contrôleurs I3C tel que déterminé par un microcontrôleur externe (Figure 5).

Figure 5 : Le commutateur I3C P3S0200GMX peut être utilisé pour reconfigurer un bus I3C en routant les signaux de bus I3C entre un contrôleur I3C et plusieurs ensembles de périphériques cibles, ou entre une seule cible et plusieurs contrôleurs I3C. (Source de l'image : NXP Semiconductors)

Figure 5 : Le commutateur I3C P3S0200GMX peut être utilisé pour reconfigurer un bus I3C en routant les signaux de bus I3C entre un contrôleur I3C et plusieurs ensembles de périphériques cibles, ou entre une seule cible et plusieurs contrôleurs I3C. (Source de l'image : NXP Semiconductors)

La commutation entre deux cibles peut être requise si les deux cibles ont la même adresse et ne peuvent pas résider sur le même bus. Alternativement, une seule cible peut devoir être partagée entre deux processus, exigeant un commutateur entre les deux contrôleurs I3C.

Conclusion

I3C est une interface série qui étend le bus I²C en augmentant son débit de données, en réduisant le nombre de fils et en ajoutant de la flexibilité au contrôle du bus. Cette amélioration permet d'augmenter l'utilité des interfaces I²C et SPI existantes.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.