Utiliser des MOSFET SiC pour améliorer le rendement de conversion de puissance

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-10-29

Les tendances en matière d'exigences de puissance supérieures, d'obligations réglementaires et de normes quant au rendement et aux problèmes d'interférences électromagnétiques (EMI) entraînent la nécessité pour les alimentations d'utiliser des dispositifs de commutation de puissance en raison de leur rendement supérieur et de leur plage de fonctionnement étendue. Dans le même temps, les concepteurs subissent une pression constante pour réduire les coûts et économiser de l'espace. Face à ces exigences, une alternative aux MOSFET classiques basés silicium (Si) s'avère nécessaire.

Le carbure de silicium (SiC) apparaît clairement comme une option maintenant qu'il a évolué et en est à sa troisième génération. Les FET SiC offrent de nombreux avantages de performances, notamment en termes de rendement, de plus grande fiabilité, de réduction des problèmes de gestion thermique et d'empreinte réduite. Ils s'appliquent à l'ensemble du spectre de puissance et ne nécessitent pas de changement radical quant aux techniques de conception, bien que des réglages puissent être nécessaires.

Cet article offre une brève comparaison entre Si et SiC, fournit des exemples de dispositifs SiC de Wolfspeed et indique la manière de les utiliser pour commencer la conception.

MOSFET SiC et Si

Tout d'abord, il est important de clairement définir la technologie et la terminologie : les FET SiC sont des MOSFET, tout comme leurs prédécesseurs au silicium. Au sens large, leurs structures physiques internes sont semblables et il s'agit de dispositifs à trois bornes offrant des connexions à la source, au drain et à la grille.

La différence est indiquée dans leur nom : les FET SiC utilisent le carbure de silicium en tant que matériau de base plutôt que le silicium uniquement. Nombreux sont les spécialistes du secteur à y faire référence sous le terme de « dispositifs SiC », en omettant de mentionner la partie MOSFET. Dans le présent article, nous les appellerons « FET SiC ».

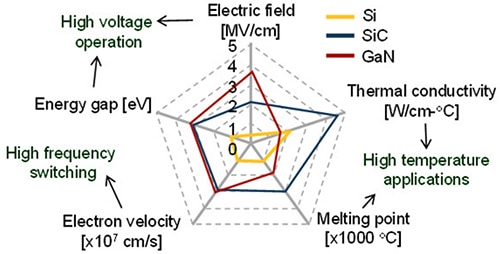

Pourquoi utiliser un composé SiC en tant que matériau ? Pour différentes raisons physiques profondes, le SiC présente trois caractéristiques électriques principales qui diffèrent considérablement du silicium, chacune offrant des avantages opérationnels. Il en existe d'autres, mais qui sont plus subtiles (Figure 1).

Figure 1 : Comparaison approximative entre les propriétés matérielles clés des matériaux solides basés SiC, Si et GaN. Par rapport au Si, le SiC présente une tension de claquage plus élevée, une conductivité thermique supérieure et une bande interdite plus large. (Source de l'image : Researchgate)

Figure 1 : Comparaison approximative entre les propriétés matérielles clés des matériaux solides basés SiC, Si et GaN. Par rapport au Si, le SiC présente une tension de claquage plus élevée, une conductivité thermique supérieure et une bande interdite plus large. (Source de l'image : Researchgate)

Les avantages sont les suivants :

- Une tension de claquage critique de champ électrique plus élevée d'environ 2,8 mégavolts par centimètre (MV/cm) par rapport à 0,3 MV/cm pour le Si. Le fonctionnement à une tension nominale donnée est donc possible avec une couche bien plus fine, ce qui réduit grandement la résistance à l'état passant.

- Une conductivité thermique supérieure, qui favorise une densité de courant plus élevée dans une section transversale.

- Une bande interdite plus large (la différence d'énergie, en eV, entre le haut de la bande de valence et le bas de la bande de conduction dans les semi-conducteurs et les isolateurs), qui permet d'avoir un courant de fuite plus faible à hautes températures. C'est la raison pour laquelle les FET et les diodes SiC sont souvent appelés « dispositifs à large bande interdite » (WBG).

Par conséquent, en termes approximatifs, les dispositifs basés SiC peuvent bloquer des tensions jusqu'à dix fois supérieures à celles des dispositifs au silicium et peuvent commuter environ dix fois plus rapidement avec une résistance à l'état passant de moitié ou moins à 25°C. Dans le même temps, leur capacité à fonctionner à une température bien plus élevée de 200°C (contre 125°C pour le Si) facilite la conception et la gestion thermiques.

Le rôle fondamental du circuit d'attaque de grille pour pouvoir bénéficier de ces avantages

Un dispositif de puissance ne fonctionne pas sans son circuit d'attaque de grille, qui transforme des signaux de commande numériques de faible niveau en signaux de tension et de courant nécessaires, parallèlement à la temporisation requise par le dispositif de puissance (tout en fournissant également une protection contre la plupart des types d'erreurs externes). Pour les FET SiC, le circuit d'attaque doit inclure des fonctions supplémentaires afin de :

- Réduire les pertes de commutation et conduction, ainsi que les pertes au niveau du circuit d'attaque. Ces pertes incluent l'émission d'énergie à l'état bloqué et à l'état débloqué, l'effet Miller et les exigences du courant d'attaque de grille. L'énergie à l'état bloqué dépend de la résistance de grille et de la tension grille-source à l'état bloqué. Pour limiter ces pertes, davantage de courant doit être puisé au niveau de la grille. Pour ce faire, le circuit d'attaque peut appliquer une polarisation négative à la tension de grille lors du blocage. De même, l'énergie à l'état débloqué est réduite en limitant la résistance de grille.

- Réduire l'effet Miller et ses conséquences négatives (la capacité parasite peut entraîner un déblocage involontaire dans certains cas et avec certaines configurations d'application). Ce déblocage provoqué par l'effet Miller augmente l'énergie de recouvrement inverse et ajoute aux pertes. Pour y remédier, le circuit d'attaque peut utiliser une fonction appelée protection contre l'effet Miller, qui contrôle le courant d'attaque lors de la commutation de l'étage de puissance.

- Fournir le courant absorbé et le courant source nécessaires aux tensions appropriées. Les dispositifs SiC nécessitent généralement un circuit d'attaque de grille à polarisation positive plus élevée (+20 V) que les MOSFET au silicium afin de réduire les pertes. Ils peuvent également nécessiter une tension de grille désactivée négative entre -2 V et -6 V. Le courant de grille requis est déterminé par les calculs habituels basés sur la charge de grille (Qg), VDD, le courant de drain ID, la tension grille-source et la résistance de grille. Il est généralement de l'ordre de quelques ampères. Ce courant doit présenter des valeurs nominales d'absorption et de source adéquates à une vitesse de balayage proportionnelle à la vitesse de commutation du FET SiC.

- Modeler et réduire les parasites au niveau carte et dispositif (capacités et inductances parasites) pouvant entraîner des oscillations, des dépassements de courant/tension et des déclenchements incorrects aux vitesses de commutation plus élevées de ces dispositifs. Les MOSFET au silicium présentent une petite « queue » de courant qui agit comme un amortisseur ou un circuit d'amortissement afin de réduire les dépassements et les oscillations dans une certaine mesure. Les MOSFET SiC ne disposent pas de cet élément, et les dépassements de tension de drain et les oscillations peuvent donc être supérieurs et entraîner des problèmes. Pour limiter ces parasites, il faut prêter une attention particulière aux problèmes de disposition, en réduisant les longueurs de matériau conducteur et en positionnant le circuit d'attaque aussi près que possible de son dispositif d'alimentation. Même quelques centimètres peuvent faire une différence, car l'effet de ces capacités et inductances parasites est plus important aux vitesses de commutation supérieures des FET SiC. La réduction des oscillations présente également un deuxième avantage, car elle limite la génération des EMI associées à la commutation haute vitesse du circuit d'attaque et du côté charge du dispositif.

Malgré les problèmes supplémentaires liés à l'utilisation de MOSFET SiC, il existe des circuits intégrés standard conçus à cet effet par différents fournisseurs, avec des attributs correspondant aux besoins spécifiques des dispositifs SiC. Il convient de noter que dans de nombreuses conceptions, les circuits d'attaque de grille et les FET SiC doivent être isolés galvaniquement des circuits basse tension. Cela peut être implémenté par l'intermédiaire de techniques d'isolement optiques, capacitives ou à transformateur d'impulsions à l'aide de composants standard. L'isolement est nécessaire tout d'abord pour des raisons de sécurité, afin de protéger les utilisateurs contre les hautes tensions en cas de dysfonctionnements des circuits, mais aussi dans les nombreuses topologies de circuit où le MOSFET n'est par nature pas mis à la terre, comme dans les configurations en pont.

Les nouveaux dispositifs offrent de bonnes performances

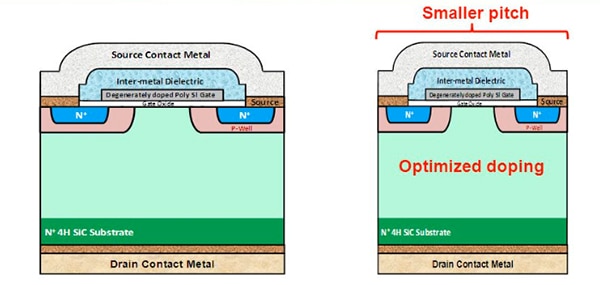

Le premier MOSFET SiC encapsulé commercial, le CMF20120D, a été lancé par Wolfspeed en janvier 2011 (Wolfspeed est la branche de Wolfspeed dédiée à la puissance et la RF ; son nom a été annoncé en 2015). À cette époque, des plaquettes SiC étaient déjà disponibles depuis quelques années. La valeur nominale de ce premier MOSFET SiC était de 1200 V/98 A avec une résistance à l'état passant de 80 mΩ (le tout à 25°C), dans un boîtier TO-247. Wolfspeed a rapidement enchaîné avec un traitement de 2e génération et propose actuellement des MOSFET SiC de 3e génération désignés comme dispositifs C3M (Figure 2).

Figure 2 : La comparaison de la structure de traitement SiC de 2e génération (à gauche) et de 3e génération (à droite) de Wolfspeed présente peu de différences, mais ces coupes transversales ne montrent pas l'amélioration obtenue quant aux spécifications de performances. (Source de l'image : Wolfspeed)

Figure 2 : La comparaison de la structure de traitement SiC de 2e génération (à gauche) et de 3e génération (à droite) de Wolfspeed présente peu de différences, mais ces coupes transversales ne montrent pas l'amélioration obtenue quant aux spécifications de performances. (Source de l'image : Wolfspeed)

Par exemple, la plateforme C3M0280090J fait partie des premières plateformes MOSFET SiC de 900 V de l'industrie. Elle est optimisée pour les applications d'électronique de puissance haute fréquence, notamment les onduleurs d'énergie renouvelable, les systèmes de charge de véhicules électriques et les alimentations industrielles triphasées (Tableau 1).

|

Tableau 1 : Les principales caractéristiques du MOSFET SiC C3M0280090J de Wolfspeed montrent qu'il est parfaitement adapté aux onduleurs d'énergie renouvelable, aux systèmes de charge de véhicules électriques et aux alimentations industrielles triphasées. (Source du tableau : Wolfspeed)

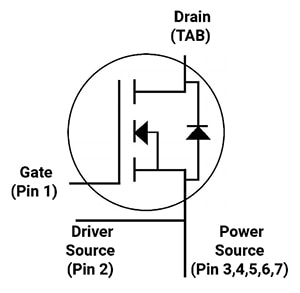

En plus des spécifications de tension/courant, ce dispositif est optimisé pour la commutation haute vitesse avec de faibles capacités, dispose d'un boîtier à faible impédance avec une connexion à la source du circuit d'attaque (Figure 3), inclut une diode intrinsèque rapide à faible charge de recouvrement inverse (Qrr) et présente une fuite en surface étendue (~7 millimètres [mm]) entre le drain et la source.

Figure 3 : Le C3M0280090J de Wolfspeed dispose d'un boîtier à faible impédance avec une connexion à la source du circuit d'attaque. (Source de l'image : Wolfspeed)

Figure 3 : Le C3M0280090J de Wolfspeed dispose d'un boîtier à faible impédance avec une connexion à la source du circuit d'attaque. (Source de l'image : Wolfspeed)

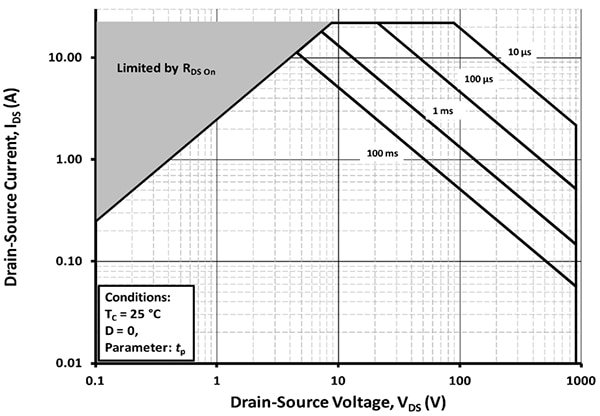

Cette plateforme de 900 V permet d'avoir des systèmes de conversion de puissance nouvelle génération plus compacts et à rendement supérieur, à un coût équivalent à celui des solutions à base de silicium, mais avec des spécifications supérieures. Le graphique de l'aire de sécurité (SOA) résume les capacités de ce FET SiC (Figure 4). Lorsque la tension drain-source (VDS) est faible, le courant maximal est limité par la résistance à l'état passant. À une tension VDS modérée, le composant peut supporter 15 A pendant de courtes périodes.

Figure 4 : Le graphique SOA correspondant au C3M0280090J de Wolfspeed illustre ses capacités IDS et VDS. (Source de l'image : Wolfspeed)

Figure 4 : Le graphique SOA correspondant au C3M0280090J de Wolfspeed illustre ses capacités IDS et VDS. (Source de l'image : Wolfspeed)

Le boîtier affecte les performances

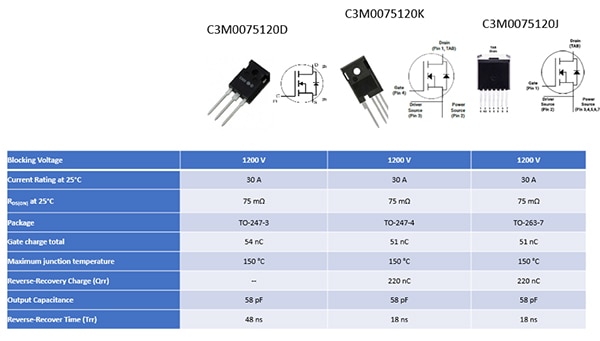

Wolfspeed propose également trois dispositifs présentant des spécifications similaires (le C3M0075120D, le C3M0075120K et le C3M0075120J), mais dont la différence majeure concerne le boîtier (Figure 5).

Figure 5 : Wolfspeed propose le même FET SiC de 1200 V dans trois boîtiers différents, avec des spécifications à peu près équivalentes, mais pas identiques. (Source de l'image : Wolfspeed)

Figure 5 : Wolfspeed propose le même FET SiC de 1200 V dans trois boîtiers différents, avec des spécifications à peu près équivalentes, mais pas identiques. (Source de l'image : Wolfspeed)

Même si les chiffres parlent d'eux-mêmes, les choses ne s'arrêtent pas là. Le dispositif au suffixe D se trouve dans un boîtier à trois bornes (TO-247-3), alors que le suffixe K est quant à lui dans un boîtier à quatre bornes (TO-247-4). Ces deux dispositifs, tout comme celui au suffixe J à sept bornes, incluent une broche de source Kelvin qui réduit les effets des pointes de tension induites par L × di/dt dans le circuit de grille. Une tension supérieure peut ainsi être appliquée à la grille et à la source, ce qui donne une commutation dynamique plus rapide. Les résultats démontrent une réduction potentielle des pertes de commutation qui peuvent être divisées par 3,5 lorsque les dispositifs sont mesurés à une valeur proche de leur courant nominal.

Les cartes d'évaluation et les conceptions de référence accélèrent la réussite

À l'opposé des conceptions RF en gigahertz, la création d'un circuit hautes performances pour un fonctionnement à des tensions et une plage de puissances plus élevées nécessite tout de même de prêter attention aux détails. Toutes les subtilités et les particularités des composants et de la disposition sont amplifiées, et le circuit physique ne laisse passer aucun problème ni aucun oubli.

Afin d'aider les concepteurs à évaluer des FET SiC comme le C3M0075120D et le C3M0075120K, Wolfspeed propose le kit d'évaluation abaisseur-élévateur KIT-CRD-3DD12P qui permet de démontrer les performances de commutation haute vitesse de ces dispositifs (Figure 6). Il est conçu pour accepter aussi bien le boîtier à trois bornes du C3M0075120D que le boîtier à quatre bornes du C3M0075120K aux caractéristiques similaires. Le concepteur peut ainsi tester et comparer les performances des MOSFET 3e génération (C3M) de Wolfspeed dans différents boîtiers.

Figure 6 : Le kit d'évaluation KIT-CRD-3DD12P constitue un moyen pratique d'évaluer aussi bien les performances du C3M0075120D dans un boîtier TO-247 à trois bornes que celles du C3M0075120K à quatre bornes. Vous remarquerez le grand dissipateur thermique et l'inductance torique qui permettent d'obtenir des performances thermiques supérieures. (Source de l'image : Wolfspeed)

Figure 6 : Le kit d'évaluation KIT-CRD-3DD12P constitue un moyen pratique d'évaluer aussi bien les performances du C3M0075120D dans un boîtier TO-247 à trois bornes que celles du C3M0075120K à quatre bornes. Vous remarquerez le grand dissipateur thermique et l'inductance torique qui permettent d'obtenir des performances thermiques supérieures. (Source de l'image : Wolfspeed)

Le kit d'évaluation se présente dans une configuration en demi-pont et permet l'ajout d'un MOSFET ou d'une diode sur le dessus et le dessous, pour pouvoir configurer la carte selon des topologies de conversion de puissance courantes, par exemple en tant qu'abaisseur synchrone ou en tant qu'élévateur synchrone. Il permet également l'ajout de diodes sur le dessus ou le dessous, afin que les utilisateurs évaluent une topologie de convertisseur abaisseur ou élévateur asynchrone.

En outre, pour réduire la perte de puissance, le kit s'accompagne d'une inductance à faible perte constituée de « sendust ». Également appelée « Kool Mµ », cette poudre métallique magnétique (composée de 85 % de fer, 9 % de silicium et 6 % d'aluminium) est utilisée comme alternative au permalloy en raison de ses spécifications améliorées pour les paramètres magnétiques et thermiques clés.

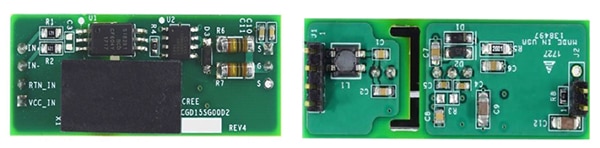

Pour les utilisateurs qui ont besoin de concevoir leur propre sous-circuit de circuit d'attaque de grille, Wolfspeed propose également la conception de référence de circuit d'attaque de grille CGD15SG00D2 pour ces FET SiC 3e génération (Figure 7).

Figure 7 : Le dessus (à gauche) et le dessous (à droite) de la conception de référence de circuit d'attaque de grille CGD15SG00D2, une carte complète avec nomenclature intégrale et la possibilité pour l'utilisateur de comparer les performances des boîtiers TO-247 à trois et quatre bornes avec le même MOSFET SiC. (Source de l'image : Wolfspeed)

Figure 7 : Le dessus (à gauche) et le dessous (à droite) de la conception de référence de circuit d'attaque de grille CGD15SG00D2, une carte complète avec nomenclature intégrale et la possibilité pour l'utilisateur de comparer les performances des boîtiers TO-247 à trois et quatre bornes avec le même MOSFET SiC. (Source de l'image : Wolfspeed)

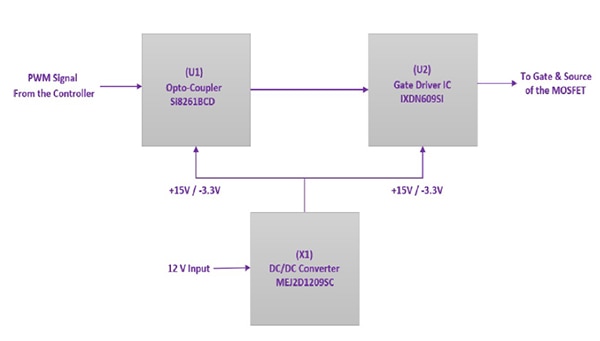

Le schéma fonctionnel de haut niveau (Figure 8) du CGD15SG00D2 illustre les fonctions de cette conception de référence, notamment un photocoupleur (U1), un circuit intégré d'attaque de grille (U2) et une alimentation isolée (X1). Le photocoupleur (isolement de 5000 VCA) accepte les signaux à modulation de largeur d'impulsion (PWM) et fournit une immunité en mode commun de 35/50 kilovolts/microseconde (kV/µs) (minimum/typique). Les fonctionnalités suivantes sont également notables :

- Une rainure qui permet d'améliorer la spécification de fuite en surface imposée entre le côté logique et le côté puissance du circuit imprimé, ainsi qu'une fente d'amélioration de la fuite en surface de 9 mm entre les circuits principaux et secondaires de la carte.

- Une alimentation isolée de 2 watts prenant en charge le fonctionnement de MOSFET plus grands à des fréquences plus élevées.

- Des résistances de déblocage et de blocage de grille séparées avec une diode dédiée afin que l'utilisateur puisse personnaliser et optimiser les signaux de déblocage et de blocage.

- Une inductance de mode commun au niveau de l'entrée de puissance logique pour améliorer l'immunité aux EMI.

Figure 8 : Ce schéma fonctionnel de haut niveau de la conception de référence du circuit d'attaque de grille CGD15SG00D2 illustre ses principaux blocs fonctionnels, à savoir un photocoupleur (U1), un circuit intégré d'attaque de grille (U2) et une alimentation isolée (X1). (Source de l'image : Wolfspeed)

Figure 8 : Ce schéma fonctionnel de haut niveau de la conception de référence du circuit d'attaque de grille CGD15SG00D2 illustre ses principaux blocs fonctionnels, à savoir un photocoupleur (U1), un circuit intégré d'attaque de grille (U2) et une alimentation isolée (X1). (Source de l'image : Wolfspeed)

Conclusion

Les MOSFET SiC 3e génération de Wolfspeed présentent d'importantes améliorations des performances en termes de rendement et de capacités thermiques pour les applications de commutation de puissance par rapport aux MOSFET Si traditionnels. Associés à un circuit d'attaque adapté, ils offrent des performances fiables et constantes, que ce soit pour les applications émergentes ou bien établies.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.