Principes de base du décalage de niveau logique

Mélange de tensions de niveaux logiques haut et bas dans les communications et les GPIO

Présentation

Les dernières conceptions de dispositifs numériques sont de plus en plus petites, rapides et efficaces. La logique 5 V de base est rejointe par des normes de tension encore plus basses, comme 3,3 V, 2,5 V, 1,8 V et moins, ce qui nécessite une méthodologie permettant à des systèmes différents de communiquer de manière fiable et efficace. Les concepteurs doivent s'assurer qu'il est possible d'atteindre un 1 logique ou un 0 logique de manière prévisible sur toutes ces plateformes.

La translation/l'isolement des tensions logiques binaires ou à deux niveaux favorise un comportement de circuit prévisible. Les concepteurs peuvent penser qu'un signal de 3,3 V sur une broche de 5 V « devrait fonctionner », mais ce n'est pas toujours le cas dans toutes les conditions. Inversement, une tension de 5 V sur une broche de 3,3 V compatible 5 V fonctionne certainement dans la plupart des cas, mais cette méthode est plus coûteuse en raison de composants supplémentaires et de la « consommation » de la tension excédentaire dans certains cas.

Y a-t-il une alternative ?

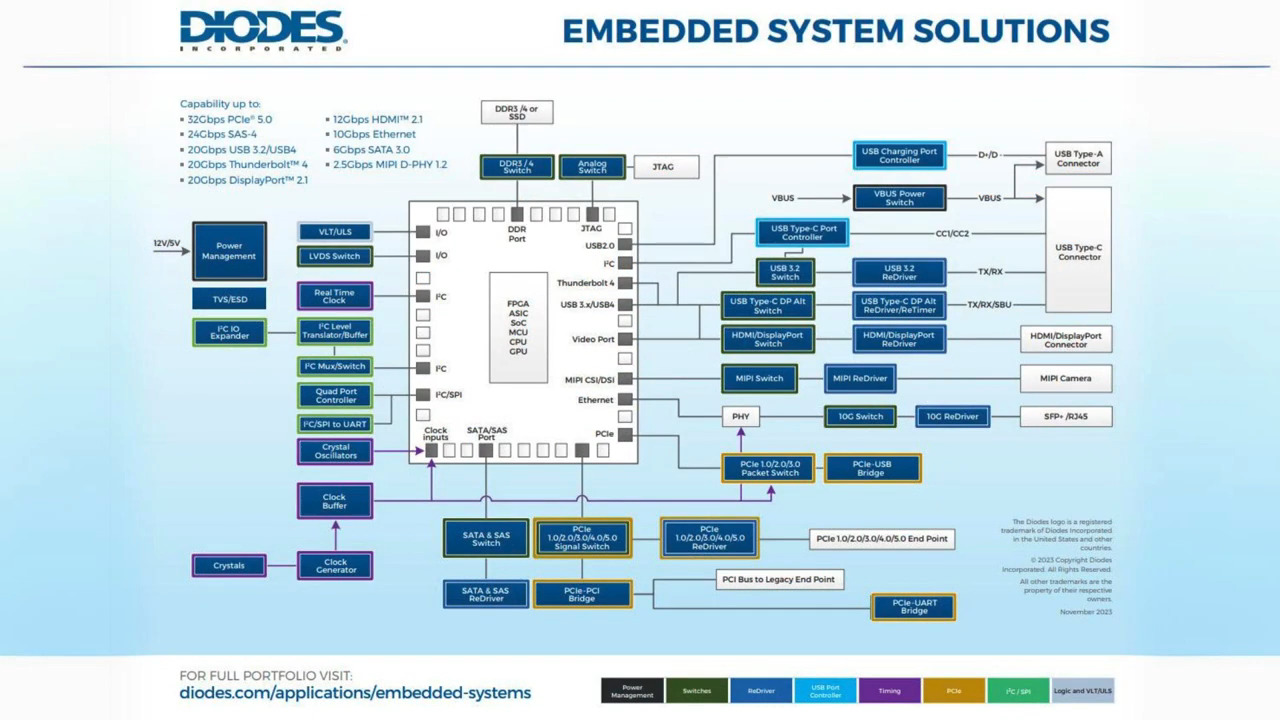

Les translateurs/dispositifs de décalage de niveau permettent de résoudre les problèmes de translation courants et peuvent même fournir des fonctions utiles supplémentaires, comme l'inversion, une sortie push-pull, trois états ou une fonctionnalité différentielle. Mais a-t-on réfléchi à une solution moins complexe permettant des niveaux de tension logique plus étendus et une communication bidirectionnelle ? Un MOSFET compact discret peut accomplir une translation à haute fréquence et à haut rendement. Le décalage de niveau pour une communication telle qu'une connexion broche à broche GPIO directe et I²C se fait à l'aide de ces semi-conducteurs peu coûteux et de quelques dispositifs passifs supplémentaires. En choisissant les MOSFET appropriés, il est possible d'atteindre des tensions logiques supérieures, comme 12 V ou 18 V, qui peuvent également être utilisées pour la surveillance des circuits automobiles, par exemple.

Remarque : I²C en mode HS (haute vitesse) peut nécessiter des composants plus poussés, comme le translateur bidirectionnel PCA9306 de NXP.

Exemple : BS170 (transistor à effet de champ à mode d'enrichissement à canal N)

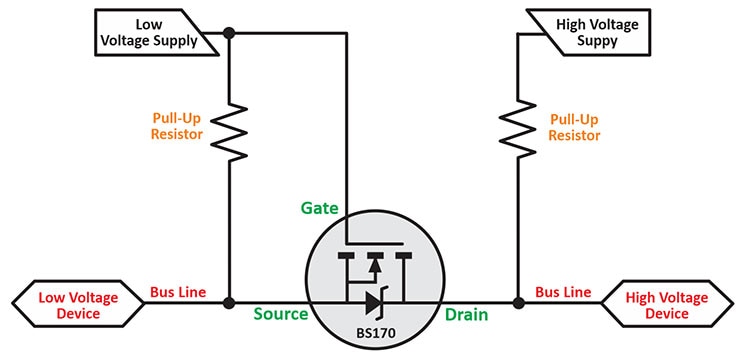

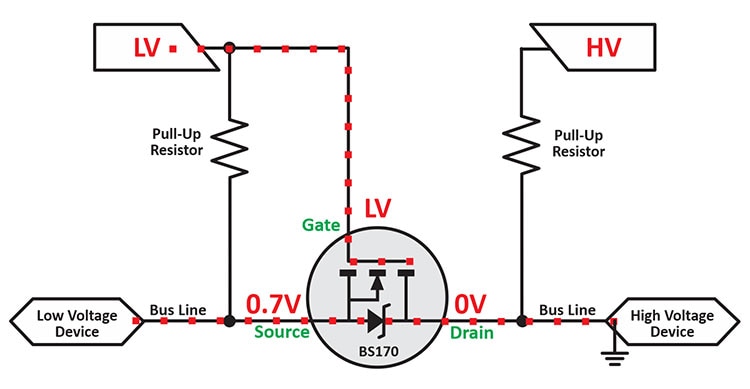

Le BS170 est conçu pour réduire la résistance à l'état passant tout en fournissant des performances de commutation fiables et rapides adaptées aux applications de commutation à faible courant et basse tension. La Figure 1 montre les connexions requises pour établir une communication de base ou un décalage de niveau logique GPIO.

Figure 1 : Circuit MOSFET de translation de niveau de base à un bus.

Figure 1 : Circuit MOSFET de translation de niveau de base à un bus.

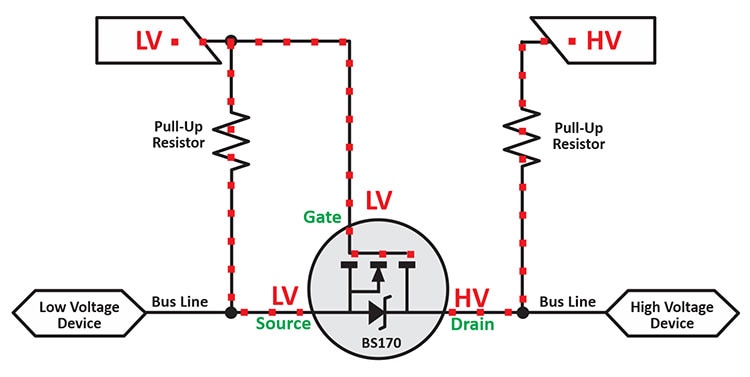

Les niveaux logiques élevés de chaque côté du MOSFET sont atteints à l'aide de résistances d'excursion haute vers leurs alimentations respectives, fournissant une conversion de signaux I²C en mode rapide (400 kHz) ou d'autres interfaces numériques aussi rapides. La grille du MOSFET est maintenue au niveau d'alimentation basse tension. Lorsqu'aucun dispositif n'amène la ligne de bus à l'état bas, la ligne de bus au niveau de la source du MOSFET est placée à l'état haut par les résistances d'excursion haute à basse tension. La tension grille-source (VGS) du MOSFET est inférieure au seuil, et le MOSFET n'effectue pas de conduction. Cela permet à la ligne de bus au niveau du drain du MOSFET d'être amené à l'état haut par la résistance d'excursion haute à tension plus élevée. Les lignes de bus de chaque côté du MOSFET sont maintenues à l'état haut, mais à des niveaux de tension différents. Voir la Figure 2.

Figure 2 : Translation de tension à l'état haut logique.

Figure 2 : Translation de tension à l'état haut logique.

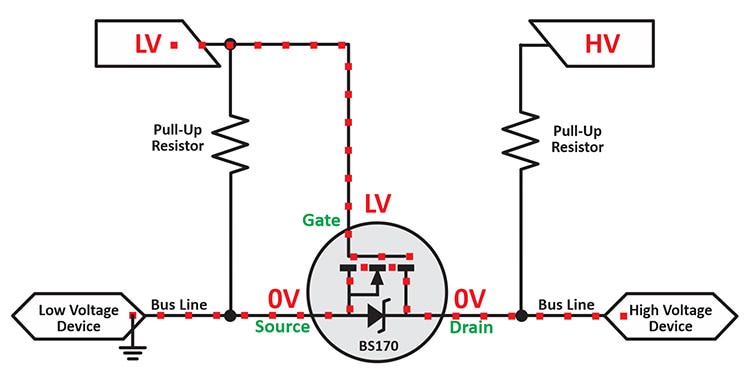

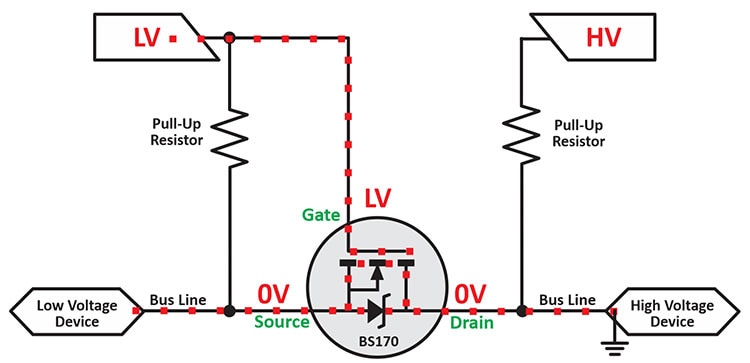

Si le dispositif basse tension place la ligne de bus à l'état bas au niveau de la source du MOSFET et si la grille reste au niveau de l'alimentation basse tension, la tension VGS augmente au-dessus du seuil et le MOSFET commence à effectuer une conduction. La ligne de bus au niveau du drain du MOSFET est alors également amenée à l'état bas. Voir la Figure 3.

Figure 3 : Translation de tension à l'état bas logique initiée par un dispositif basse tension.

Figure 3 : Translation de tension à l'état bas logique initiée par un dispositif basse tension.

Si le dispositif haute tension place la ligne de bus à l'état bas au niveau du drain du MOSFET, la diode de substrat du MOSFET permet à la source d'être également partiellement placée à l'état bas en raison d'une petite chute de tension au niveau de la diode. Voir la Figure 4.

Figure 4 : Translation de tension à l'état bas quasi logique initiée par un dispositif haute tension.

Figure 4 : Translation de tension à l'état bas quasi logique initiée par un dispositif haute tension.

Lorsque la source du MOSFET est partiellement placée à l'état bas, la tension VGS passe au-dessus du seuil et le MOSFET commence à effectuer une conduction en contournant la diode de substrat. Voir la Figure 5.

Figure 5 : Translation de tension à l'état bas logique complète initiée par un dispositif haute tension.

Figure 5 : Translation de tension à l'état bas logique complète initiée par un dispositif haute tension.

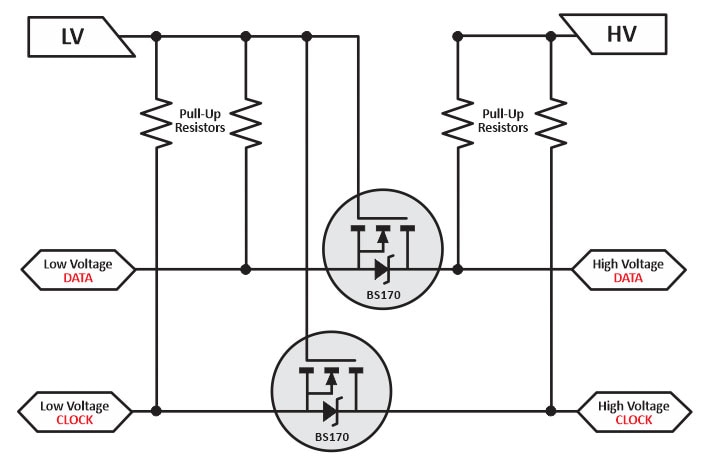

Les trois états montrent les niveaux logiques transférés dans les deux sens du système de bus, indépendamment de la section de commande. De nombreuses combinaisons d'alimentations haute tension et basse tension sont possibles en fonction des capacités du MOSFET. Que le conflit de niveaux logiques implique une communication GPIO point-à-point, de sortie de capteur ou multiligne bidirectionnelle, les dispositifs de décalage de niveau MOSFET sont des outils utiles. La Figure 6 montre l'implémentation d'un circuit de communication bidirectionnel à deux lignes avec translation utilisant deux MOSFET.

Figure 6 : Circuit de communication de données bidirectionnel à deux lignes avec translation.

Figure 6 : Circuit de communication de données bidirectionnel à deux lignes avec translation.

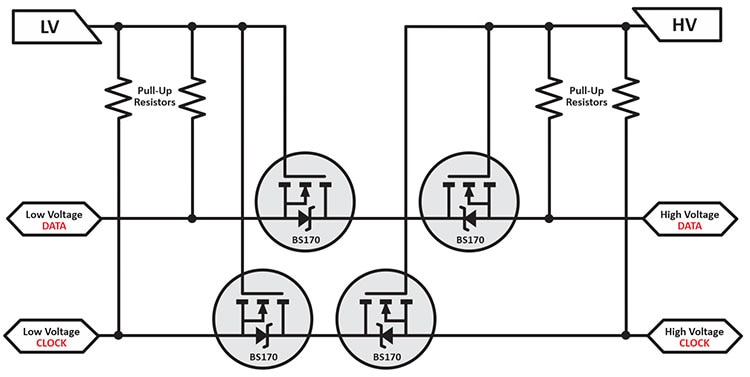

Isolement

Pour éviter des niveaux logiques aléatoires lorsque le dispositif haute tension est éteint ou en cas de perte de puissance au niveau de l'alimentation haute tension, des MOSFET supplémentaires peuvent être implémentés « drain à drain » pour isoler les lignes de bus logiques haute tension.

Figure 7 : Lignes de bus isolées dans un circuit de communication de données avec translation.

Figure 7 : Lignes de bus isolées dans un circuit de communication de données avec translation.

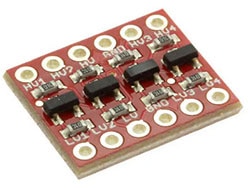

Cartes de développement

Pour en savoir plus sur la translation de niveau logique, plusieurs fabricants produisent des cartes de développement équipées de MOSFET ou de dispositifs de translation logique, avec les dispositifs passifs requis pour permettre une connexion et des tests rapides.

Résumé

Pour réussir avec cette méthode de translation logique simple et efficace, il est essentiel de bien choisir le MOSFET et la résistance d'excursion haute. Les fiches techniques des dispositifs typiques contiennent les informations nécessaires pour les tests. Les résistances d'excursion haute pour le BS170 dans la plage de 4,7 kΩ à 10 kΩ peuvent convenir dans la plupart des cas. Des circuits intégrés de convertisseur de niveau logique dédiés peuvent également fournir des fonctionnalités supplémentaires, comme une protection DES de 15 kV sur les E/S et les entrées de tension d'alimentation.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum