Concevoir et certifier des systèmes RTD fonctionnellement sûrs

Avec la contribution de Rédacteurs nord-américains de DigiKey

2023-07-24

Le capteur de température à résistance (RTD), composé d'un transducteur et de son circuit de mise en forme des signaux AFE (circuit d'entrée analogique), est largement utilisé, précis et fiable. Cependant, pour les applications critiques et haute fiabilité, il est souvent nécessaire de concevoir et de garantir un système fonctionnellement sûr via les processus de certification des composants Route 1S ou Route 2S.

La certification d'un système pour la sécurité fonctionnelle est un processus complexe, car tous les composants du système doivent être examinés pour les modes et mécanismes de défaillance potentiels. Il existe différentes méthodes pour diagnostiquer les pannes, et l'utilisation de composants déjà certifiés facilite cette charge de travail ainsi que le processus de certification.

Il convient de noter que la « fiabilité » est liée à la sécurité fonctionnelle mais différente. En termes simples, « fiable » fait référence à une conception et à une implémentation fonctionnant selon les spécifications sans problème ni défaillance, tandis que « fonctionnellement sûr » signifie que toute défaillance doit être détectée par la conception. La fiabilité et la sécurité fonctionnelle sont toutes les deux nécessaires pour les applications critiques.

Cet article examine les bases des RTD et de leurs circuits de mise en forme des signaux dans le contexte d'une certification fonctionnellement sûre. Il aborde ensuite les différents niveaux de certification de défaillance et de fiabilité, et ce qui est nécessaire pour les atteindre via les deux processus. Deux circuits intégrés AFE RTD à plusieurs canaux, la paire AD7124 d'Analog Devices, ainsi qu'une configuration de carte d'évaluation associée, sont utilisés pour illustrer les points clés.

Rôle de la sécurité fonctionnelle

Le rôle de la sécurité fonctionnelle est d'éviter tout risque inacceptable de blessure ou d'atteinte à la santé des personnes grâce à la mise en œuvre correcte d'une ou de plusieurs fonctions automatiques de protection/sécurité. Elle garantit que le produit, le dispositif ou le système continue de fonctionner en toute sécurité en cas de dysfonctionnement. Elle est nécessaire dans un large éventail d'applications industrielles, commerciales et même certaines applications grand public, telles que :

- Véhicules autonomes

- Sécurité des machines et robotique

- Systèmes de contrôle industriel (ICS)

- Produits domotiques grand public

- Usines intelligentes et chaînes d'approvisionnement

- Systèmes instrumentés de sécurité et systèmes de contrôle de zones dangereuses

Par exemple, dans une conception fonctionnellement sûre, la fonction d'un interrupteur marche/arrêt principal doit toujours permettre de couper l'alimentation, même si d'autres composants du système sont défaillants (Figure 1).

Figure 1 : Dans un système fonctionnellement sûr, il ne peut y avoir aucun doute ni aucune ambiguïté quant au fait que cet interrupteur fera ce pour quoi il est conçu. (Source de l'image : Pilla via City Electric Supply Co.)

Figure 1 : Dans un système fonctionnellement sûr, il ne peut y avoir aucun doute ni aucune ambiguïté quant au fait que cet interrupteur fera ce pour quoi il est conçu. (Source de l'image : Pilla via City Electric Supply Co.)

Principes de base des RTD

Pourquoi s'intéresser à la température et à la sécurité fonctionnelle ? Une bonne raison est que la température est le paramètre physique le plus souvent mesuré. Il est souvent lié aux applications critiques ou de sécurité, et il est pris en charge par une vaste sélection de transducteurs. Parmi ceux-ci figurent les RTD, qui sont conceptuellement simples : ils exploitent le coefficient de température de résistance (TCR) connu et reproductible de métaux tels que le nickel, le cuivre et le platine. Les RTD en platine avec une résistance de 100 ohms (Ω) et 1000 Ω à 0°C sont les plus largement utilisés et peuvent être utilisés sur une plage de -200°C à +850°C.

Ces RTD ont une relation résistance-température hautement linéaire sur cette plage de températures ; pour les situations ultra-haute précision, il existe des tables et des facteurs de correction et de compensation qui peuvent être appliqués. Le RTD en platine avec une résistance nominale de 100 Ω (PT100) a une résistance typique de 18 Ω à -200°C et de 390,4 Ω à +850°C.

L'utilisation d'un RTD nécessite qu'il soit excité par un courant connu qui est généralement maintenu à environ 1 milliampère (mA) pour minimiser l'auto-échauffement. D'autres valeurs de courant sont également utilisées, en fonction de la résistance RTD nominale.

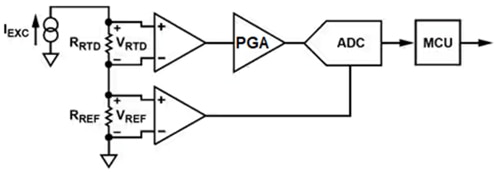

La chute de tension à travers le RTD est mesurée simultanément via un AFE composé d'un amplificateur à gain programmable (PGA) et, dans la plupart des cas, d'un convertisseur analogique-numérique (CAN) en conjonction avec un microcontrôleur (MCU) (Figure 2).

Figure 2 : L'utilisation d'un RTD pour mesurer la température nécessite de faire passer un courant connu dans le RTD et de mesurer la chute de tension à travers celui-ci, puis d'appliquer la loi d'Ohm. (Source de l'image : Digi-Key)

Figure 2 : L'utilisation d'un RTD pour mesurer la température nécessite de faire passer un courant connu dans le RTD et de mesurer la chute de tension à travers celui-ci, puis d'appliquer la loi d'Ohm. (Source de l'image : Digi-Key)

La topologie de circuit de ce schéma de base est identique à l'utilisation d'une résistance de détection pour déterminer le courant à travers une charge, mais ici les variables connues et inconnues sont inversées. Pour la détection du courant, la résistance est connue tandis que le courant est inconnu, donc le calcul est I = V/R. Pour les RTD, le courant est connu, mais la résistance ne l'est pas, donc le calcul est R = V/I.

Le PGA est requis pour maintenir l'intégrité des signaux et maximiser la plage dynamique, car les niveaux de tension dans le RTD peuvent s'étendre de dizaines de millivolts à des centaines de millivolts, selon la température et le type de RTD.

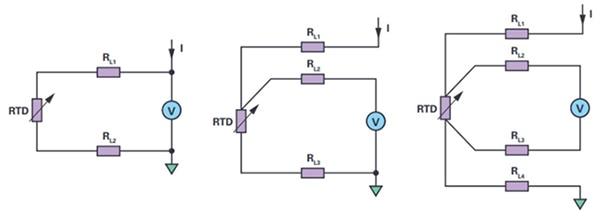

La connexion physique entre la source d'excitation, le RTD et le PGA peut être une interface à deux, trois ou quatre fils. Bien que deux fils suffisent en principe, il existe des problèmes associés à la chute IR dans les fils de connexion, ainsi qu'à d'autres artefacts. L'utilisation de topologies à trois et quatre fils dans une connexion Kelvin plus avancée permet d'obtenir des performances plus précises et régulières, même si cela augmente les coûts de câblage (Figure 3).

Figure 3 : Le RTD peut être commande et détecté via seulement deux fils (à gauche), mais l'utilisation de trois fils (au centre) et même de quatre fils (à droite, connexion Kelvin) permet d'éliminer diverses sources d'erreur dues aux fils. (Source de l'image : Analog Devices)

Figure 3 : Le RTD peut être commande et détecté via seulement deux fils (à gauche), mais l'utilisation de trois fils (au centre) et même de quatre fils (à droite, connexion Kelvin) permet d'éliminer diverses sources d'erreur dues aux fils. (Source de l'image : Analog Devices)

Commencer par la terminologie et les normes

Comme avec de nombreuses spécialités, la sécurité fonctionnelle comporte de nombreux termes, ensembles de données et acronymes uniques qui sont largement utilisés dans les discussions connexes. Ils incluent :

- Intensité de défaillance (FIT) : le nombre de défaillances auxquelles s'attendre sur un milliard (109) d'heures de fonctionnement du dispositif.

- Analyse des modes de défaillance et de leurs effets (FMEA) : processus d'examen d'autant de composants, assemblages et sous-systèmes que possible pour identifier les modes de défaillance potentiels dans un système, ainsi que leurs causes et leurs effets.

- Analyses des modes de défaillance, des effets et des diagnostics (FMEDA) : technique d'analyse systématique permettant d'obtenir les taux de défaillance au niveau du sous-système/produit, les modes de défaillance et la capacité de diagnostic.

Les données FIT ainsi que les analyses FMEDA sont requises sur les différents composants du système pour une analyse complète. L'analyse FMEA ne fournit que des informations qualitatives, tandis que l'analyse FMEDA offre des informations à la fois qualitatives et quantitatives, permettant aux utilisateurs de mesurer le niveau de criticité des modes de défaillance et de les classer par importance. L'analyse FMEDA ajoute des informations sur les risques, les modes de défaillance, l'analyse des effets et des diagnostics, et la fiabilité.

- Niveau d'intégrité de sécurité (SIL) : il existe quatre niveaux d'intégrité distincts associés à SIL : SIL 1, SIL 2, SIL 3 et SIL 4. Plus le niveau SIL est élevé, plus le niveau de sécurité associé est élevé et plus la probabilité qu'un système ne fonctionne pas correctement est faible.

Une valeur SIL 2 indique que plus de 90 % des défaillances du système peuvent être diagnostiquées. Pour certifier une conception, le concepteur du système doit fournir à l'organisme de certification des preuves des défaillances potentielles, de leur caractère sûr ou dangereux et de la manière dont elles peuvent être diagnostiquées.

- La norme CEI 61508, officiellement intitulée « Sécurité fonctionnelle des systèmes électriques/électroniques/électroniques programmables relatifs à la sécurité » (et appelée de manière informelle simplement « Sécurité fonctionnelle électronique »), est la spécification pour les conceptions fonctionnellement sûres. Elle documente le flux de conception nécessaire pour développer un composant certifié SIL. La documentation doit être générée pour chaque étape, du concept et de la définition à la conception, la configuration, la fabrication, l'assemblage et le test.

Ce processus, connu sous le nom de Route 1S, est complexe. Cependant, il existe une alternative au processus Route 1S, appelé flux Route 2S. Il s'agit d'un processus « éprouvé en utilisation » et applicable lorsque de grands volumes du produit ont été intégrés dans des produits et systèmes finaux et sont utilisés sur le terrain avec des milliers d'heures de fonctionnement cumulées.

Avec le flux Route 2S, un produit peut être certifié en fournissant à l'autorité de certification les preuves suivantes :

- Volumes utilisés sur le terrain

- Analyse de tous les retours sur le terrain et information que les retours n'étaient pas dus à des défaillances dans le composant lui-même

- Fiche technique de sécurité détaillant les diagnostics et la couverture qu'ils apportent

- FMEDA des broches et des puces

Fusion des interfaces RTD avec le flux SIL Route 2S

La certification d'un système est un long processus, car tous les composants du système doivent être examinés pour les mécanismes de défaillance potentiels, et il existe différentes méthodes pour diagnostiquer les défaillances. L'utilisation de composants déjà certifiés réduit l'effort requis et raccourcit le processus de certification.

Un composant d'interface RTD hautement intégré et mature est essentiel pour faciliter la certification Route 2S, car il définit un ensemble de solutions complet et peut donc être entièrement caractérisé avec des données associées à l'utilisation sur le terrain et aux défaillances. Cela diffère de l'utilisation de plusieurs petits circuits intégrés, où les diverses interfaces et interactions doivent être analysées pour la configuration d'interconnexion spécifique utilisée.

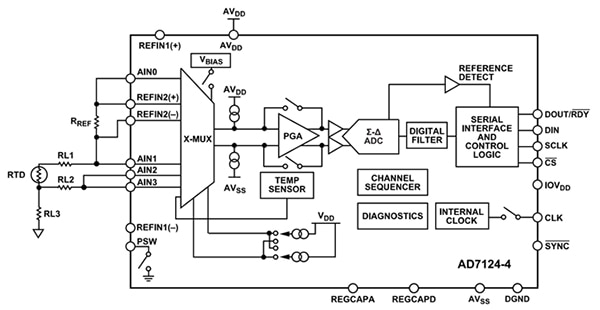

Un exemple est l'AD7124-4 à quatre canaux (Figure 4), et le modèle similaire à huit canaux AD7124-8 (ci-après appelés collectivement « AD7124 » lorsqu'il est question des nombreuses caractéristiques qu'ils partagent). Ces composants conviennent parfaitement au flux Route 2S en raison de leurs fonctions d'autotest et de diagnostic embarquées, ainsi que de leurs « antécédents » sur le terrain.

Figure 4 : L'AD7124-4 à quatre canaux est une chaîne de signaux capteur-processeur RTD fonctionnellement complète. (Source de l'image : Analog Devices)

Figure 4 : L'AD7124-4 à quatre canaux est une chaîne de signaux capteur-processeur RTD fonctionnellement complète. (Source de l'image : Analog Devices)

Ces circuits intégrés sont des solutions complètes pour la mesure RTD à plusieurs canaux et ils incluent tous les éléments constitutifs nécessaires d'un capteur vers une sortie numérisée et pour la communication avec un microcontrôleur associé. Ils incluent un multiplexeur multicanal, un PGA, un CAN sigma-delta 24 bits, les sources de courant pour les RTD, les références de tension pour le fonctionnement interne, une horloge système, le filtrage analogique et numérique et des interfaces série à trois ou quatre fils pour les interconnexions compatibles avec SPI, QSPI, MICROWIRE et DSP.

Cependant, la présence de ces fonctions ne fournit pas en soi une base pour la qualification SIL Route 2S. Pour une conception fonctionnellement sûre, un ensemble de diagnostics intégrés est requis pour les nombreuses fonctions qui composent le système RTD. Les multiples diagnostics embarqués dans l'AD7124 minimisent à la fois la complexité et le temps de conception, et éliminent le besoin de dupliquer la chaîne de signaux pour la couverture de diagnostic.

Ces diagnostics incluent, mais sans s'y limiter, la surveillance de l'alimentation, de la tension de référence et de l'entrée analogique ; la détection d'un fil nu vers les RTD ; la vérification des performances de conversion et d'étalonnage ; la vérification des fonctionnalités de la chaîne de signaux ; la surveillance des fonctions de lecture/écriture ; et la surveillance du contenu du registre.

Comment ces déclarations de « haut niveau » se traduisent-elles en diagnostics sur puce nécessaires ? La réponse comporte de nombreuses facettes, notamment :

Diagnostic SPI : pour chaque écriture sur l'AD7124, le processeur génère une valeur de contrôle par redondance cyclique (CRC) qui est ajoutée aux informations envoyées au CAN. Le CAN génère ensuite sa propre valeur CRC à partir des informations reçues et la compare à la valeur CRC reçue du processeur. Si les deux valeurs concordent, les informations sont intactes et seront écrites dans le registre sur puce correspondant.

Si les valeurs ne correspondent pas, cela signifie que la transmission est corrompue, et le circuit intégré définit un indicateur d'erreur qui signale qu'une corruption des données s'est produite. L'AD7124 s'auto-protége également en n'écrivant pas les informations corrompues dans un registre.

Une procédure CRC similaire est utilisée lorsque des informations sont lues depuis l'AD7124 vers le processeur système. Enfin, l'interface compte également les impulsions d'horloge pour s'assurer qu'il n'y a que huit de ces impulsions avec chaque trame de données de lecture ou d'écriture, garantissant ainsi qu'aucun problème d'horloge ne s'est produit.

Vérifications de la mémoire : un contrôle CRC est également utilisé pour valider le contenu des registres à la mise sous tension ou chaque fois que les registres sur puce sont modifiés (comme lors de la modification du gain). Le processus CRC est également exécuté périodiquement pour garantir qu'aucun bit de mémoire n'a été « inversé » en raison de bruit ou d'autres causes. S'il y a un changement et que le processeur est ensuite informé que les paramètres de registre ont été corrompus, il peut réinitialiser le CAN et recharger les registres.

Vérifications de la chaîne de signaux : toutes les tensions statiques critiques peuvent être vérifiées via le CAN, y compris les rails d'alimentation, les sorties de régulateur à faible chute de tension (LDO) et les tensions de référence ; la présence ou l'absence de condensateur externe dans le LDO peut également être vérifiée. De plus, une tension connue peut être appliquée à l'entrée CAN pour vérifier le CAN et les réglages de la fonction de gain. Des courants connus peuvent être injectés dans les entrées analogiques pour rechercher un RTD ouvert ou en court-circuit.

Conversion et étalonnage : les résultats de la conversion CAN sont vérifiés en permanence pour voir s'ils passent tous à zéro ou à pleine échelle, l'un ou l'autre indiquant un problème. Le flux binaire du modulateur au cœur du CAN est surveillé pour s'assurer qu'il n'est pas saturé, et si une saturation se produit (ce qui signifie qu'il y a eu 20 uns ou zéros consécutifs du modulateur), un indicateur d'erreur est défini.

Fréquence de l'horloge maître : la fréquence de cette horloge contrôle non seulement les taux de conversion mais établit également les fréquences de rejet des filtres numériques 50/60 Hertz (Hz). Un registre interne dans l'AD7124 permet au processeur auxiliaire de chronométrer et donc de vérifier la précision de l'horloge maître.

Fonctionnalités additionnelles : l'AD7124 inclut un capteur de température, qui peut également être utilisé pour surveiller la température de la puce. Les deux versions ont une capacité de décharge électrostatique (DES) de 4 kilovolts (kV) pour des performances robustes, et sont logées dans un boîtier LFCSP de 5 millimètres (mm) × 5 mm convenant aux conceptions à sécurité intrinsèque.

En raison de la complexité interne, de la sophistication et des fonctionnalités d'autotest avancées de l'AD7124-4 et de l'AD7124-8, il est logique de disposer d'un moyen permettant de tester et d'évaluer les circuits intégrés.

Pour ce faire, Analog Devices propose deux cartes connectées : la carte d'évaluation EVAL-AD7124-4SDZ pour l'AD7124-4 (Figure 5) et la carte d'interface auxiliaire EVAL-SDP-CB1Z SDP (plateforme de démonstration système) (Figure 6). La première est spécifique à l'AD7124-4 et fonctionne en conjonction avec la deuxième qui fournit la communication avec le PC de l'utilisateur et le logiciel d'évaluation via une liaison USB.

Figure 5 : L'EVAL-AD7124-4SDZ est une carte d'évaluation pour l'AD7124-4. (Source de l'image : Analog Devices)

Figure 5 : L'EVAL-AD7124-4SDZ est une carte d'évaluation pour l'AD7124-4. (Source de l'image : Analog Devices)

Figure 6 : La carte d'interface EVAL-SDP-CB1Z est un complément de la carte d'évaluation EVAL-AD7124-4SDZ, fournissant une connexion USB à un PC hôte. (Source de l'image : Analog Devices)

Figure 6 : La carte d'interface EVAL-SDP-CB1Z est un complément de la carte d'évaluation EVAL-AD7124-4SDZ, fournissant une connexion USB à un PC hôte. (Source de l'image : Analog Devices)

Le dispositif d'évaluation est pris en charge par le logiciel AD7124-4 EVAL+, qui configure entièrement les fonctionnalités de registre du dispositif AD7124-4 et teste le circuit intégré. Il fournit également une analyse dans le domaine temporel sous la forme de graphiques de forme d'onde, d'histogrammes et d'analyses de bruit associées pour l'évaluation des performances du CAN.

Transition vers une conception fonctionnellement sûre

Il est important de réaliser que l'AD7124-4 et l'AD7124-8 ne sont pas répertoriés SIL, ce qui signifie qu'ils ne sont pas conçus et développés selon les directives de développement telles que définies par la norme CEI 61508. Cependant, grâce à une compréhension de l'application finale et à l'utilisation appropriée des divers diagnostics, ils peuvent être évalués pour une utilisation dans une conception répertoriée SIL.

Le chemin vers la certification Route 1S comporte plusieurs considérations pour analyser et traiter les défaillances, qui peuvent être systémiques ou aléatoires. Les défaillances systémiques sont dues à des défauts de conception ou de fabrication, comme une interruption bruyante due à un manque de filtrage sur la broche d'interruption externe ou à une marge insuffisante pour un signal. En revanche, les défaillances aléatoires sont dues à des causes physiques telles que la corrosion, les contraintes thermiques ou l'usure.

Un problème important concerne les défaillances dangereuses non détectées, qui sont traitées par diverses techniques. Pour minimiser les défaillances aléatoires, les concepteurs peuvent utiliser une ou plusieurs des trois tactiques suivantes :

- Composants plus fiables et moins sollicités.

- Diagnostics reposant sur des mécanismes de détection intégrés mis en œuvre via du matériel ou des logiciels.

- Tolérance aux pannes via des circuits redondants. L'ajout d'un chemin redondant permet de tolérer une seule défaillance. C'est ce que l'on appelle un système HFT 1 (Hardware Fault Tolerance 1), ce qui signifie qu'une seule défaillance ne peut pas entraîner la défaillance du système.

Un outil pour comprendre la couverture du niveau SIL est une table qui met en relation la fraction de défaillance sûre (SFF) (le niveau de couverture de diagnostic) et la tolérance aux défaillances matérielles (la redondance) (Figure 7).

|

|||||||||||||||||||||||

Figure 7 : Cette table caractérise la fraction de défaillance sûre (SFF) par rapport à la tolérance aux défaillances matérielles (HFT) et fournit des indications sur la couverture SIL. (Source de l'image : Analog Devices)

Les rangées indiquent le niveau de couverture de diagnostic, tandis que les colonnes indiquent la tolérance aux défaillances matérielles. Un HFT de 0 signifie que si une seule défaillance se produit dans le système, la fonction de sécurité sera perdue. Un niveau de diagnostic plus élevé réduit la quantité nécessaire de redondance du système ou améliore le niveau SIL de la solution avec le même niveau de redondance.

Il convient de noter que l'analyse FMEDA d'une application de température typique utilisant ces dispositifs montre une fraction de défaillance sûre (SFF) supérieure à 90 % conformément à la norme CEI 61508. Deux CAN traditionnels seraient normalement nécessaires pour fournir ce niveau de couverture via la redondance, mais l'AD4172 ne requiert qu'un seul CAN, ce qui permet de réaliser des économies importantes en termes de coûts de nomenclature (BOM) et d'espace carte.

Documentation pour les conceptions répertoriées SIL

Une documentation complète est nécessaire pour obtenir la certification Route 1S. Les documents sources nécessaires incluent :

- Fiche technique de sécurité (manuel de sécurité pour un composant répertorié SIL)

- Analyses FMEDA de broche et de puce, avec modes de défaillance, effets et analyse pour les deux

- Liste de contrôle pour l'annexe F (définie par la CEI 61508)

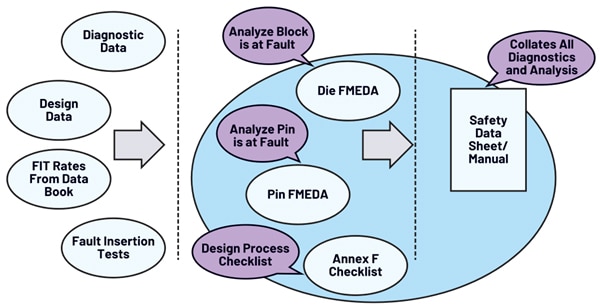

Cette documentation, à son tour, provient de diverses sources (Figure 8) :

- Les données de diagnostic de la fiche technique capturent toutes les fonctionnalités de diagnostic disponibles dans le composant.

- Les données de conception font référence aux données internes. Par exemple, la surface de puce et l'impact de chaque bloc interne du composant.

- Les informations FIT, avec les taux pour divers composants, sont disponibles dans le manuel de données.

- Des tests d'insertion de défaillances sont effectués pour les blocs qui ne peuvent pas être analysés à l'aide des données de conception et de diagnostic. Ces tests sont planifiés en fonction des exigences de l'application et les résultats des tests d'insertion de défaillances sont utilisés pour renforcer les documents FMEDA et FMEA.

Figure 8 : Les diverses sources de documentation sont agrégées et extraites pour fournir l'ensemble d'informations complet nécessaire à la certification SIL. (Source de l'image : Analog Devices)

Figure 8 : Les diverses sources de documentation sont agrégées et extraites pour fournir l'ensemble d'informations complet nécessaire à la certification SIL. (Source de l'image : Analog Devices)

Si l'on regarde les spécificités plus en détail :

- Le manuel de sécurité ou la fiche technique de sécurité utilise toutes les informations compilées pour fournir les exigences nécessaires pour permettre l'intégration de l'AD7124-4 ou de l'AD7124-8. Il rassemble tous les diagnostics et analyses provenant de divers documents et ensembles de données.

- L'analyse FMEDA de puce pour l'AD7124-4 et l'AD7124-8 analyse les principaux blocs du schéma d'application, identifie les modes de défaillance et les effets, et vérifie le diagnostic et les analyses pour une fonction de sécurité particulière. Par exemple, l'analyse du module d'horloge montre les modes de défaillance, l'effet de chacun sur la sortie, le niveau de couverture de diagnostic et une analyse de l'impact (Figure 9).

|

Figure 9 : Ce tableau définit le mode de défaillance, les effets, les diagnostics et l'analyse du bloc d'horloge maître. (Source de l'image : Analog Devices)

L'analyse FMEDA de puce résulte en une présentation quantitative des taux de défaillance pour les défaillances sûres, les défaillances dangereuses détectées et les défaillances dangereuses non détectées. Tous ces éléments sont utilisés pour calculer la fraction SFF.

L'analyse FMEDA de broche aborde les défaillances sous un angle différent. Elle analyse les différents types de défaillances sur les broches de l'AD7124-4 et de l'AD7124-8 et leurs conséquences pour l'application RTD. Elle le fait pour chaque broche individuelle et décrit le résultat pour chaque cas d'utilisation : broche ouverte, en court-circuit à l'alimentation/à la terre ou en court-circuit aux broches adjacentes.

La liste de contrôle de l'annexe F est une liste de vérification des mesures de conception pour éviter les défaillances systématiques. Elle inclut :

- Présentation des produits

- Informations d'application

- Concept de sécurité

- Prévisions de durée de vie

- FIT

- Calculs FMEDA—SFF et DC

- Mécanismes de sécurité du matériel

- Description du diagnostic

- Robustesse CEM

- Fonctionnement dans des configurations redondantes

- Annexes et liste de documents

En résumé, la certification de sécurité fonctionnelle pour un composant nouvellement introduit via Route 1S est un processus long, complexe, chronophage, intense et complet. Heureusement, Route 2S, comme mentionné ci-dessus, est une approche alternative viable pour certains composants.

Route 2S : une voie alternative

La méthode connue sous le nom de Route 2S peut s'appliquer à un composant mis sur le marché avec l'expérience et les données de terrain, et désigné comme « éprouvé en utilisation ». Elle est basée sur une analyse des retours clients et du nombre de dispositifs expédiés. Elle ne peut pas être utilisée avec des nouveaux composants qui n'ont pas un long historique d'utilisation réelle.

La méthode Route 2S permet la certification SIL comme si le composant avait été entièrement analysé selon la norme CEI 61508. Elle est disponible pour les concepteurs de modules et de systèmes s'ils ont utilisé avec succès le circuit intégré en question dans le passé et connaissent le taux de défaillance sur le terrain. Grâce aux fonctionnalités de test et de vérification embarquées et aux données de performances, l'AD7214-4 et le l'AD7214-8 sont de bons candidats pour Route 2S.

L'application de Route 2S nécessite des données détaillées et statistiquement significatives sur les retours et les défaillances de terrain. Cette exigence est beaucoup plus difficile à satisfaire pour les fournisseurs de circuits intégrés que pour les fournisseurs de cartes ou de modules. En effet, les premiers n'ont généralement pas une connaissance suffisante de l'application finale ou du pourcentage d'unités défectueuses renvoyées pour analyse.

Conclusion

La méthode Route 1S pour la certification fonctionnellement sûre des nouveaux produits est complète, exhaustive et détaillée. Elle est également exigeante sur le plan technique et prend beaucoup de temps. En revanche, la méthode Route 2S permet aux produits commercialisés d'être certifiés en fonction de l'expérience sur le terrain, des défaillances et des données d'analyse. Il s'agit d'une méthode utile qui est prise en charge par les circuits intégrés d'interface RTD AD7214-4 et AD7214-8 car ils ont l'historique requis. Tout aussi important, ces circuits intégrés intègrent de nombreuses fonctions et caractéristiques de diagnostic et d'autotest qui en font des candidats appropriés pour une telle certification.

Contenu connexe

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.