Pourquoi et comment appliquer des transistors à effet de champ GaN à des applications d'alimentation à découpage haute tension efficaces

Avec la contribution de Rédacteurs nord-américains de DigiKey

2023-01-26

Le rendement énergétique est une priorité pour les systèmes électroniques face aux exigences sociétales et réglementaires. La densité de puissance et le rendement de conversion énergétique sont essentiels à la réussite d'une conception, en particulier pour les applications telles que les véhicules électriques (VE), les communications à haute tension et les infrastructures industrielles.

Pour répondre à ces exigences, les concepteurs de systèmes d'alimentation à découpage doivent abandonner les transistors bipolaires à grille isolée (IGBT) et les transistors à effet de champ à semi-conducteur à oxyde métallique (MOSFET) basés silicium (Si) classiques, car ils approchent rapidement de leurs limites théoriques.

Les concepteurs doivent plutôt envisager des dispositifs basés sur des matériaux à large bande interdite (WBG) tels que le nitrure de gallium (GaN). Les dispositifs GaN commutent plus rapidement que les dispositifs Si. Ils supportent des niveaux de tension et de puissance plus élevés, sont beaucoup plus petits pour un niveau de puissance donné et fonctionnent avec un rendement beaucoup plus élevé.

Cet article examine les principes de base des FET GaN, montre leurs avantages par rapport aux dispositifs Si traditionnels dans les circuits d'alimentation à découpage, présente des exemples concrets de Nexperia et discute de leur application.

Principes de base des FET GaN

Les éléments fondamentaux des circuits de conversion de puissance sont les commutateurs à semi-conducteurs haute tension. Les concepteurs se sont attachés à améliorer les performances de ces dispositifs via la diminution des pertes par conduction en réduisant la résistance série à l'état passant, la diminution des pertes de commutation en augmentant les vitesses de transition, et la réduction des effets parasites. Ces efforts de conception ont, en général, été couronnés de succès pour les MOSFET et les IGBT en silicium, mais le rythme des améliorations s'est ralenti à mesure que le fonctionnement de ces dispositifs a atteint leurs limites théoriques.

En conséquence, des composants WBG en carbure de silicium (SiC) et en GaN ont été introduits ces dernières années et sont désormais produits en série. Ces dispositifs offrent des plages de tensions de fonctionnement plus étendues, des temps de commutation plus rapides et un rendement supérieur.

La bande interdite d'un semi-conducteur est l'énergie minimum requise pour exciter les électrons afin de les faire passer de leur état lié à un état libre pour conduire l'électricité (Tableau 1).

|

Tableau 1 : Résumé des principales propriétés qui distinguent les semi-conducteurs à large bande interdite — comme le GaN et le SiC — du Si. (Source du tableau : Art Pini)

Les dispositifs fabriqués avec des semi-conducteurs à large bande interdite peuvent fonctionner à des tensions, des fréquences et des températures beaucoup plus élevées que les matériaux semi-conducteurs classiques tels que le silicium. Une bande interdite plus large est particulièrement importante pour permettre aux dispositifs de fonctionner à des températures beaucoup plus élevées. La tolérance aux hautes températures signifie que, dans des conditions normales, ces dispositifs peuvent fonctionner à des niveaux de puissance beaucoup plus élevés. Les semi-conducteurs WBG présentant un champ électrique critique et une mobilité plus élevés ont la résistance à l'état passant drain-source (RDS(ON)) la plus faible, réduisant les pertes par conduction.

La plupart des matériaux à large bande interdite ont également une vitesse d'électrons libres élevée, ce qui leur permet de fonctionner à des vitesses de commutation supérieures.

Par rapport au Si, qui a une bande interdite de 1,12 électronvolt (eV), le GaN et le SiC sont des semi-conducteurs composés dont les bandes interdites sont environ trois fois plus élevées, soit 3,4 eV et 3,3 eV respectivement. Cela signifie que les deux peuvent supporter des tensions et des fréquences plus élevées.

En raison de sa plus grande mobilité des électrons, le GaN convient mieux aux applications hautes performances et haute fréquence. Les vitesses de commutation plus rapides et les fréquences de fonctionnement plus élevées permises par les FET de puissance GaN se traduisent par des conceptions de filtres passifs à contrôle des signaux améliorées avec des fréquences de coupure supérieures et des courants ondulés inférieurs. Cela permet d'utiliser des inductances, des condensateurs et des transformateurs plus petits, entraînant une réduction de la taille et du poids globaux.

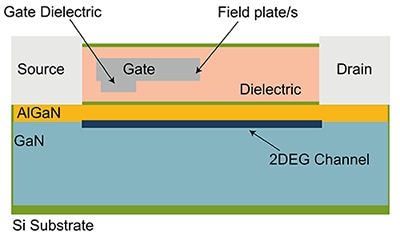

Les FET GaN sont appelés transistors à haute mobilité électronique (HEMT). La mobilité élevée des électrons est fonction de la structure du FET (Figure 1).

Figure 1 : Vue en coupe d'un FET GaN basé sur un substrat Si. (Source de l'image : Nexperia)

Figure 1 : Vue en coupe d'un FET GaN basé sur un substrat Si. (Source de l'image : Nexperia)

Les FET GaN utilisent les installations de production CMOS silicium existantes, ce qui les rend rentables. Une couche GaN est formée sur le substrat Si en déposant une couche germe et une couche échelonnée de GaN et de nitrure d'aluminium-gallium (AlGaN) comme couche d'isolation (non représentée sur le schéma) avant la croissance de la couche de GaN pur. Une deuxième couche AlGaN est déposée sur la couche GaN. Cela crée une polarisation piézoélectrique, avec un excès d'électrons générés immédiatement sous l'AlGaN, qui est un canal hautement conducteur. Cet excès d'électrons est connu comme gaz d'électrons bidimensionnel (2DEG). Ce nom reflète la très haute mobilité des électrons dans cette couche.

Une région de déplétion est formée sous la grille. Le fonctionnement de la grille est similaire à celui d'un MOSFET de puissance silicium à enrichissement à canal N. Une tension positive appliquée à la grille de ce dispositif l'active.

Cette structure est répétée plusieurs fois pour former un dispositif de puissance. Le résultat final est une solution fondamentalement simple, élégante et rentable pour la commutation de puissance.

Pour obtenir un dispositif à tension plus élevée, la distance entre le drain et la grille est augmentée. Comme la résistivité 2DEG GaN est très faible, l'impact sur la résistance de l'augmentation de la tenue en tension de blocage est beaucoup plus faible que pour les dispositifs silicium.

Les FET GaN peuvent être construits pour fonctionner dans l'une des deux configurations suivantes : mode d'enrichissement ou mode de déplétion. Les FET à mode d'enrichissement étant normalement désactivés, une tension positive par rapport au drain/source doit donc être appliquée à la grille pour activer le FET. Les FET à mode de déplétion étant normalement activés, une tension de grille négative par rapport au drain/source doit donc être appliquée pour désactiver le FET. Les FET à mode de déplétion posent problème dans un système d'alimentation car une polarisation négative doit être appliquée au FET à mode de déplétion GaN avant la mise sous tension du système.

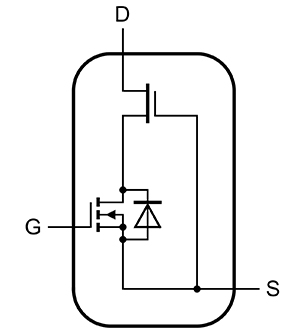

Une façon de contourner ce problème est de combiner un FET silicium basse tension avec un FET GaN à mode de déplétion dans une configuration de circuit cascode (Figure 2).

Figure 2 : Un MOSFET silicium basse tension dans une configuration cascode avec un FET GaN à mode de déplétion permet d'obtenir la robustesse de la structure de grille Si avec les caractéristiques de cadencement haute tension améliorées du dispositif GaN, ainsi que d'avoir — dans le cas d'un FET GaN à mode de déplétion — le dispositif composite désactivé à la mise sous tension. (Source de l'image : Nexperia)

Figure 2 : Un MOSFET silicium basse tension dans une configuration cascode avec un FET GaN à mode de déplétion permet d'obtenir la robustesse de la structure de grille Si avec les caractéristiques de cadencement haute tension améliorées du dispositif GaN, ainsi que d'avoir — dans le cas d'un FET GaN à mode de déplétion — le dispositif composite désactivé à la mise sous tension. (Source de l'image : Nexperia)

Le circuit cascode utilise une structure de grille MOSFET Si qui présente les avantages suivants : limites d'attaque de grille supérieures adaptées aux circuits intégrés d'attaque de grille MOSFET existants, et désactivation du FET GaN à mode de déplétion à la mise sous tension.

L'une des fonctionnalités clés des FET GaN est leur haut rendement. Cela s'explique par une faible résistance série qui réduit les pertes par conduction, des temps de commutation plus rapides qui réduisent les pertes de commutation, et une charge de recouvrement inverse plus faible qui explique leurs faibles pertes de recouvrement inverse.

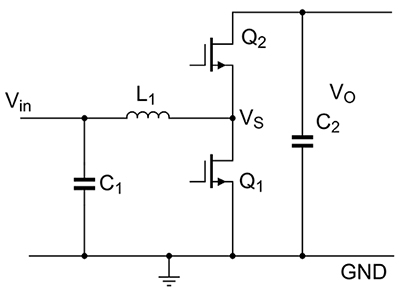

En utilisant une topologie de convertisseur élévateur en demi-pont commune, il est possible de comparer les rendements des FET GaN et des MOSFET Si (Figure 3).

Figure 3 : Schéma d'un convertisseur élévateur en demi-pont utilisé pour comparer les rendements des MOSFET et des FET GaN en échangeant les transistors Q1 et Q2 avec chaque type. (Source de l'image : Nexperia)

Figure 3 : Schéma d'un convertisseur élévateur en demi-pont utilisé pour comparer les rendements des MOSFET et des FET GaN en échangeant les transistors Q1 et Q2 avec chaque type. (Source de l'image : Nexperia)

Le convertisseur élévateur a une tension d'entrée de 240 volts (V). La sortie est de 400 V et la fréquence de commutation est de 100 kilohertz (kHz). Les rendements et les pertes sont comparés sur une plage de puissance allant jusqu'à 3500 watts (W) (Figure 4).

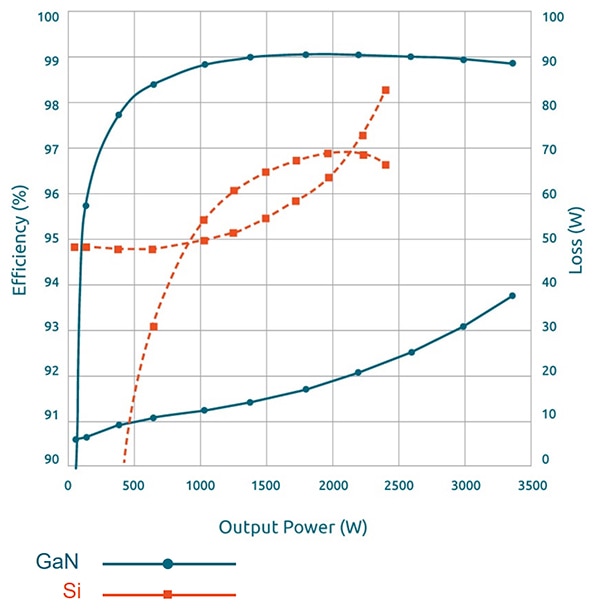

Figure 4 : Comparaison du rendement et de la perte de puissance entre les FET GaN et les MOSFET dans un circuit identique, montrant les avantages des FET GaN. (Source de l'image : Nexperia)

Figure 4 : Comparaison du rendement et de la perte de puissance entre les FET GaN et les MOSFET dans un circuit identique, montrant les avantages des FET GaN. (Source de l'image : Nexperia)

Les FET GaN ont un rendement environ 20 % supérieur à celui des MOSFET, et la perte de puissance est inférieure d'un facteur trois environ. À 2000 W, la perte dans les MOSFET est d'environ 62 W ; dans les FET GaN, elle n'est que de 19 W. Cela signifie que le système de refroidissement peut être plus petit, ce qui améliore le rendement volumétrique du convertisseur élévateur.

Ce qui est moins évident, c'est que la mesure a été effectuée à près de 3500 W pour le FET GaN en raison de sa limite de tension maximum plus élevée. En tant que tel, le FET GaN présente un avantage certain.

Démarrer avec le GaN pour des tensions plus élevées

Pour les applications à plus haute tension, Nexperia propose deux FET GaN de 650 V, le GAN063-650WSAQ et le GAN041-650WSBQ. Les deux dispositifs sont des FET à canal N normalement désactivés. Le GAN063-650WSAQ est répertorié pour une tension drain-source maximum de 650 V et peut supporter un transitoire (avec une largeur d'impulsion inférieure à une microseconde) de 800 V. Il est répertorié pour un courant de drain de 34,5 ampères (A) et une dissipation de puissance de 143 W à 25°C. La résistance à l'état passant drain-source est typiquement de 50 milliohms (mΩ), avec une limite maximum de 60 mΩ.

Le GAN041-650WSBQ présente la même tension drain-source maximum de 650 V avec la même limite transitoire de 800 V. Il se distingue par sa capacité à supporter un courant de drain maximum de 47,2 A et une dissipation de puissance maximum de 187 W à température ambiante. Sa résistance de canal typique est de 35 mΩ, avec un maximum de 41 mΩ.

Une conception de référence de Nexperia utilisant le GAN063-650WSAQ dans une configuration en demi-pont est présentée à la Figure 5.

Figure 5 : Conception recommandée pour un étage de puissance en demi-pont utilisant des FET GaN GAN063-650WSA. Le schéma ne montre que le circuit d'attaque FET et l'étage de sortie en demi-pont, ainsi que les composants associés. (Source de l'image : Nexperia)

Figure 5 : Conception recommandée pour un étage de puissance en demi-pont utilisant des FET GaN GAN063-650WSA. Le schéma ne montre que le circuit d'attaque FET et l'étage de sortie en demi-pont, ainsi que les composants associés. (Source de l'image : Nexperia)

Le schéma montre le circuit d'attaque de grille isolé double haut/bas Si8230, qui est utilisé pour commander les grilles des FET GaN. La sortie du circuit d'attaque de grille est connectée à la grille via une résistance de grille de 30 Ω, ce qui est requis pour tous les dispositifs GaN. La résistance de grille contrôle le temps de charge de la capacité de la grille, affectant les performances de commutation dynamique. Les réseaux R-C entre le drain et la source des FET permettent également de contrôler les performances de commutation. Les niveaux d'attaque de grille pour le FET GaN sont compris entre 0 et 10 à 12 V.

La haute vitesse de commutation des FET GaN (typiquement de l'ordre de 10 à 11 nanosecondes (ns)) nécessite une configuration minutieuse pour minimiser l'inductance parasite, et l'utilisation de circuits d'amortissement RC pour amortir l'oscillation due aux transitoires de tension et de courant. Il y a plusieurs circuits d'amortissement RC (R17 à 19 et C33 à 35) dans la conception entre l'alimentation haute tension et la terre. Les circuits d'amortissement réduisent l'oscillation causée par l'interaction entre le FET GaN et le réseau de dérivation. Les circuits d'amortissement doivent être connectés aussi près que possible du drain du FET haut potentiel. Ils sont implémentés avec des résistances à montage en surface et des condensateurs en céramique à faible résistance série équivalente (ESR) afin de minimiser l'inductance de sortie.

Le réseau de composants formé par R4, D1, C12 et C13 est une alimentation auto-élévatrice pour le circuit d'attaque de grille haut potentiel. D1 doit être une diode rapide à faible capacité, car sa capacité de jonction contribue aux pertes de commutation. R4 limite le courant de charge d'appel ; une valeur dans la plage de 10 Ω à 15 Ω fonctionne bien.

Conclusion

Qu'il s'agisse de véhicules électriques, de communications ou d'infrastructures industrielles, la nécessité d'améliorer le rendement de conversion de puissance et la densité de puissance impose de renoncer aux structures silicium classiques. Comme illustré, les FET GaN ouvrent la voie aux conceptions nouvelle génération en offrant des tensions de fonctionnement plus élevées, des temps de commutation plus rapides et un meilleur rendement. Des composants prêts à l'emploi, soutenus dans certains cas par des conceptions de référence, aident les concepteurs à rapidement lancer leurs projets.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.