Concevoir des alimentations à haute densité d'énergie avec des étages de puissance eGaN intégrés

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-04-16

Les alimentations à découpage à haute densité d'énergie permettent d'accélérer la charge d'une batterie, de réduire la taille des micro-onduleurs solaires et de répondre aux exigences d'alimentation d'une batterie de serveurs, le tout sans générer de chaleur excessive. Toutefois, les ingénieurs atteignent maintenant les limites de performances des MOSFET et IGBT au silicium qui constituent les principaux éléments de commutation des alimentations à découpage conventionnelles. À la place, il est désormais possible d'utiliser des transistors au nitrure de gallium à mode d'enrichissement (eGaN), un semi-conducteur à large bande interdite, pour contourner les limites de vitesse de commutation et de rendement des dispositifs silicium.

Auparavant, le coût et la disponibilité des transistors eGaN en limitaient l'utilisation aux applications d'alimentation les plus ésotériques. Cependant, une plus grande commercialisation a permis de résoudre ce problème. Les transistors eGaN se présentent maintenant comme une option pour un plus large éventail d'applications.

Cet article décrit les avantages des alimentations haute fréquence basées sur des composants de commutation eGaN par rapport à celles basées sur des MOSFET ou IGBT conventionnels au silicium (Si). Il présente ensuite des instructions sur la manière de créer des conceptions d'alimentation à découpage adaptées à des applications comme la charge de batteries ou les batteries de serveurs à l'aide d'étages de puissance eGaN d'EPC, de Texas Instruments et de Navitas Semiconductor.

Avantages de la haute fréquence

Les alimentations à découpage conventionnelles utilisent généralement des fréquences de commutation qui varient de quelques dizaines à quelques centaines de kilohertz (kHz). Le rapport cyclique de la modulation de largeur d'impulsion (PWM) de la fréquence de base détermine la sortie de tension de l'alimentation.

Le principal avantage d'une fréquence de commutation supérieure est une réduction de la taille des composants périphériques comme les inductances, les transformateurs et les résistances. Cela permet au concepteur de réduire la taille des conceptions pour la même puissance de sortie, ce qui augmente la densité d'énergie. En outre, l'ondulation du courant et de la tension à la sortie de l'alimentation à découpage est réduite, ce qui réduit le risque d'interférence électromagnétique (EMI) ainsi que le coût et la taille des circuits filtrants.

Cependant, les IGBT et MOSFET de puissance silicium conventionnels commutent relativement lentement et dissipent une puissance importante chaque fois que les dispositifs s'activent et se désactivent. Ces pertes se multiplient à mesure que la fréquence augmente, ce qui réduit le rendement et augmente la température de la puce. La combinaison de cette commutation lente et de ces pertes de commutation élevées limite la fréquence de commutation pratique des alimentations à découpage actuelles.

Les concepteurs peuvent contourner cette limite en optant pour des semi-conducteurs à large bande interdite. Parmi les semi-conducteurs disponibles, les modèles GaN représentent actuellement la technologie la plus éprouvée et la plus accessible pour cette application, les modèles eGaN étant une version améliorée des modèles GaN.

Comparaison du silicium et du GaN

Le GaN offre plusieurs avantages par rapport au silicium, notamment quelques-uns qui sont liés à la mobilité des électrons plus élevée du matériau. Une plus grande mobilité des électrons confère au semi-conducteur une tension de claquage supérieure (plus de 600 V) et une « densité de courant » supérieure (ampères/centimètre2, A/cm2). Un autre avantage du GaN est que les transistors construits avec ce matériau ne présentent pas de charge de recouvrement inverse, un phénomène pouvant déclencher un dépassement de courant de commutation élevé (oscillation).

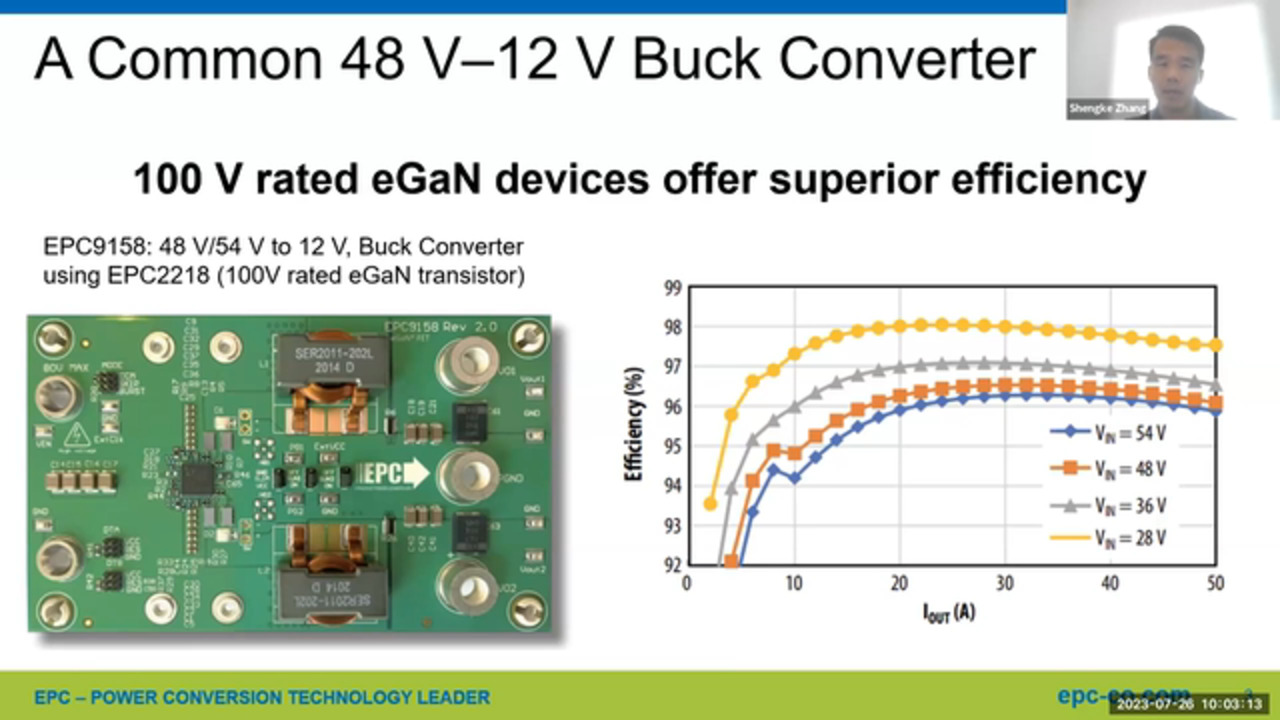

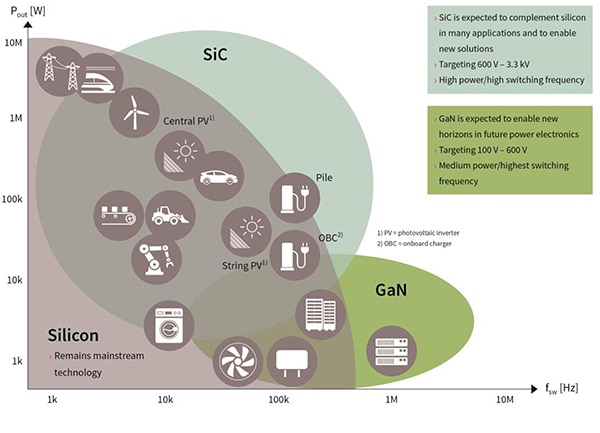

Même si ces caractéristiques sont importantes pour les concepteurs d'alimentation, le point le plus essentiel est peut-être qu'une haute mobilité des électrons permet à un transistor GaN d'effectuer une commutation environ quatre fois plus rapide qu'un MOSFET silicium. En outre, à chaque commutation du dispositif GaN, les pertes représentent environ 10 à 30 % de celles d'un transistor silicium pour une fréquence et un courant de commutation donnés. De ce fait, les transistors à haute mobilité des électrons (HEMT) GaN peuvent être utilisés à des fréquences beaucoup plus élevées que les IGBT, les MOSFET silicium ou les dispositifs au carbure de silicium (SiC) (Figure 1).

Figure 1 : Les transistors HEMT GaN permettent d'obtenir des alimentations à découpage avec des fréquences plus élevées que les dispositifs silicium ou SiC. (Source de l'image : Infineon)

Les transistors HEMT GaN ont mis longtemps à s'imposer pour deux raisons majeures. Premièrement, les dispositifs sont essentiellement des transistors à effet de champ (FET) à mode de déplétion, ce qui fait que le mode par défaut est « activé ». En revanche, les MOSFET silicium sont des dispositifs à mode d'enrichissement avec un mode par défaut « désactivé ». De ce fait, les transistors HEMT GaN nécessitent l'ajout de réseaux de polarisation soigneusement réglés pour fonctionner correctement. Deuxièmement, les transistors sont fabriqués au moyen d'un processus différent des techniques haut volume éprouvées utilisées pour le silicium, ce qui les rend plus chers. Cette complexité de conception et ce coût plus élevé ont limité les applications de transistors HEMT GaN aux alimentations à découpage haut de gamme.

Cependant, la récente commercialisation des transistors HEMT eGaN a permis d'éliminer la nécessité de réseaux de polarisation. En outre, les fournisseurs de puces ont lancé des circuits d'attaque de puissance intégrés basés sur des transistors HEMT eGaN qui simplifient la conception. Des niveaux de production accrus ont également permis de réduire le coût des dispositifs eGaN.

Solutions GaN intégrées

Dans les conceptions d'alimentation à découpage haut de gamme dans lesquelles des transistors HEMT eGaN étaient auparavant utilisés, le prix élevé a obligé les concepteurs à limiter l'utilisation des dispositifs aux transistors de puissance et à revenir aux MOSFET silicium pour les circuits d'attaque de grille. Même si certaines améliorations des performances ont été réalisées par rapport aux conceptions « entièrement au silicium », les éléments silicium dans la conception combinée ont compromis la fréquence de commutation maximale. Par ailleurs, du fait que le GaN et le silicium utilisent des technologies de traitement différentes, le circuit d'attaque de grille et les transistors de puissance devaient être fabriqués en tant que composants distincts, ce qui augmentait le coût et l'empreinte de la carte à circuit imprimé.

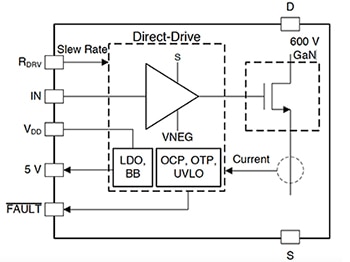

Les prix eGaN inférieurs ont permis aux fabricants de puces de résoudre ces deux problèmes. Texas Instruments, par exemple, propose son étage de puissance eGaN de 70 mΩ, 600 V LMG3411R070 avec un circuit d'attaque de grille intégré (Figure 2).

Figure 2 : Le LMG3411R070 de Texas Instruments intègre un étage de puissance eGaN de 70 mΩ et 600 V à son circuit d'attaque. (Source de l'image : Texas Instruments)

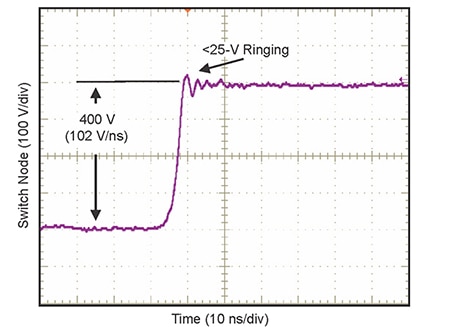

La puce peut commuter 100 V/nanoseconde (ns) avec une oscillation proche de zéro (Figure 3). À titre de comparaison, les vitesses de balayage typiques des MOSFET de puissance silicium conventionnels sont de 3 à 10 V/ns.

Figure 3 : Comme démontré par l'étage de puissance eGaN intégré LMG3411R070 de TI, les transistors de puissance eGaN peuvent gérer des vitesses de balayage bien supérieures à celles des MOSFET avec une oscillation minimale. (Source de l'image : Texas Instruments)

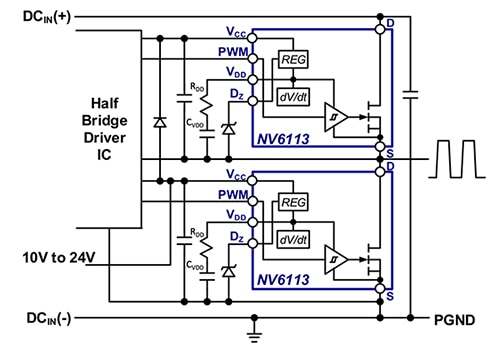

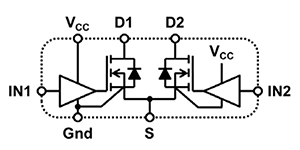

Navitas Semiconductor fabrique un produit de même catégorie, le NV6113. Le produit intègre un transistor HEMT eGaN de 300 mΩ et 650 V, un circuit d'attaque de grille et une logique associée dans un boîtier QFN de 5 mm x 6 mm. Le NV6113 peut supporter une vitesse de balayage de 200 V/ns et fonctionne jusqu'à 2 MHz.

Si des dispositifs comme les étages de puissance GaN de TI et de Navitas peuvent être déployés en parallèle pour une utilisation dans une topologie en demi-pont populaire (Figure 4), il existe d'autres produits intégrant deux transistors de puissance (et les circuits d'attaque de grille associés) sur la même puce.

Figure 4 : Le NV6113 de Navitas peut être déployé en parallèle pour des topologies en demi-pont comme illustré ici. (Source de l'image : Navitas Semiconductor)

EPC a récemment lancé l'EPC2115, un circuit d'attaque intégré qui inclut deux transistors de puissance eGaN monolithiques de 88 mΩ et 150 V, dotés chacun d'un circuit d'attaque de grille optimisé (Figure 5). L'EPC2115 est livré dans un boîtier BGA à faible inductance de 2,9 mm x 1,1 mm et peut fonctionner jusqu'à 7 MHz.

Figure 5 : Le circuit d'attaque intégré eGaN d'EPC inclut deux transistors de puissance, dotés chacun de son propre circuit d'attaque de grille optimisé. (Source de l'image : EPC)

La conception d'une alimentation à l'aide de transistors HEMT eGaN suit généralement les mêmes principes qu'une conception utilisant des MOSFET silicium, mais la fréquence de fonctionnement plus élevée a un impact sur la sélection des composants périphériques.

Sélection des composants périphériques

Pour illustrer l'impact de la fréquence sur la sélection des composants, pensez à un condensateur d'entrée pour une topologie d'alimentation à découpage CC/CC en mode abaisseur simple.

Les condensateurs d'entrée réduisent l'amplitude de la tension d'ondulation d'entrée, ce qui a pour effet d'atténuer le courant ondulé à un niveau pouvant être géré par des condensateurs de découplage abordables sans dissipation de puissance excessive. La réduction de l'amplitude d'ondulation de tension crête-à-crête en dessous de 75 mV est une bonne règle de base pour maintenir les courants au niveau des condensateurs de découplage dans des limites acceptables. Le condensateur d'entrée est généralement un dispositif en céramique, car il affiche la résistance série équivalente (ESR) extrêmement faible requise pour réduire efficacement l'ondulation de tension.

Pour déterminer la valeur du condensateur d'entrée en céramique nécessaire pour réduire l'amplitude de l'ondulation de tension crête-à-crête à une grandeur donnée, utilisez l'Équation 1 :

![]()

Où :

- CMIN est la capacité d'entrée céramique minimum requise en microfarads (μF)

- fSW est la fréquence de commutation en kHz

- VP(max) est la tension d'ondulation crête-à-crête maximum autorisée

- IOUT est le courant de charge de sortie en régime permanent

- dc est le rapport cyclique (tel que défini ci-dessus)

- (À partir de la Référence 1)

Voici les résultats du calcul avec quelques valeurs opérationnelles typiques pour un étage de puissance silicium haut de gamme :

- VIN = 12 V

- VOUT = 3,3 V

- IOUT = 10 A

- η = 93 %

- fSW = 300 kHz

- dc = 0,296

- VP(max) = 75 mV

CMIN calculée = 92 µF

Voici le résultat du même calcul pour un étage de puissance eGaN, comme le dispositif Navitas fonctionnant à 2 MHz, avec un rendement légèrement amélioré, mais avec les autres conditions de fonctionnement similaires :

- VIN = 12 V

- VOUT = 3,3 V

- IOUT = 10 A

- η = 95 %

- fSW = 2000 kHz

- dc = 0,289

- VP(max) = 75 mV

CMIN calculée = 13 µF

La réduction de CMIN permet l'utilisation d'un composant plus petit.

Si la commutation rapide des transistors HEMT eGaN est généralement avantageuse, elle introduit également quelques défis uniques en matière de conception. Le plus gros défi concerne les problèmes associés à la vitesse de balayage très élevée.

Contrôle de la vitesse de balayage

Une vitesse de balayage rapide (dV/dt) peut causer des problèmes tels que les suivants :

- Perte de commutation accrue

- Interférences électromagnétiques rayonnées et conduites

- Interférences ailleurs dans le circuit avec couplage depuis le nœud de commutation

- Dépassement et oscillation de tension au niveau du nœud de commutation en raison de l'inductance de boucle de puissance et d'autres parasites

Ces problèmes sont plus visibles lors du démarrage ou dans des conditions de commutation dure.

Lors de l'utilisation du produit de Navitas, une solution simple consiste à contrôler la vitesse de balayage au moment de l'activation en ajoutant une résistance entre le condensateur CVDD et la broche VDD (voir Figure 4). La résistance (RDD) définit le courant d'activation du circuit d'attaque de grille intégré et détermine la vitesse de balayage du front (de descente) d'activation du drain du FET de puissance (Figure 6).

Figure 6 : La résistance RDD définit le courant d'activation du NV6113 et détermine la vitesse de balayage du front (de descente) d'activation du drain du FET de puissance. (Source de l'image : Navitas Semiconductor)

Le LMG3411 prend également en charge l'ajustement de la vitesse de balayage en connectant une résistance (RDRV) à la source de transistor de puissance (voir Figure 2). Le choix de résistance définit la vitesse de balayage de la tension de drain entre 25 et 100 V/ns environ.

Le choix de la vitesse de balayage est, en définitive, un compromis. Des vitesses plus rapides réduisent la perte de puissance du fait que la durée pendant laquelle le commutateur conduit simultanément (et inefficacement) un courant élevé est réduite, mais d'autres caractéristiques de performances baissent. Une règle de base consiste à viser la vitesse la plus rapide permettant de maintenir les interférences électromagnétiques, le dépassement et l'oscillation dans les spécifications.

Un deuxième défi de conception est le risque d'événements de surintensité associés à un fonctionnement haute fréquence.

L'importance de la protection contre la surintensité

Le principal avantage de la conception d'une alimentation à découpage avec des fréquences de commutation plus élevées est de réduire la taille des composants passifs, ce qui permet d'augmenter la densité de puissance globale. Inconvénient : cette densité de puissance accrue multiplie les risques de dommages en cas d'événements de surintensité. Les événements de surintensité sont un risque omniprésent pour les alimentations à découpage. Parmi d'autres problèmes, les pics de surintensité peuvent provoquer un déclenchement accidentel en raison d'une inductance parasite externe provenant de la piste du circuit imprimé source.

Si une protection contre la surintensité (OCP) rapide est importante pour les alimentations à découpage utilisant des MOSFET traditionnels, elle est encore plus essentielle pour les transistors HEMT eGaN pour les raisons suivantes :

- Pour la même tension de blocage et la même résistance à l'état passant, la surface du transistor HEMT eGaN est beaucoup plus petite, ce qui fait qu'il est plus difficile de dissiper l'accumulation de chaleur pendant un événement de surintensité.

- Une surintensité doit être détectée pendant que le transistor HEMT eGaN fonctionne dans la région linéaire, sinon le dispositif entre rapidement en saturation, ce qui provoque une dissipation excessive de puissance et des dommages.

Une approche conventionnelle de la protection contre la surintensité consiste à utiliser un transformateur de mesure du courant, des résistances shunts ou des circuits de détection de désaturation (Tableau). Malheureusement, ces éléments peuvent avoir des effets négatifs sur les performances du système en augmentant les résistances et les inductances parasites dans la boucle d'alimentation, ce qui nécessite une réduction de la vitesse de balayage et une augmentation de la dissipation de puissance résultante. En outre, les dispositifs discrets comme les transformateurs de mesure du courant ou les résistances shunts augmentent le coût et l'espace carte utilisé.

Une approche alternative de la protection contre la surintensité consiste à détecter la tension drain-source (VDS) du FET GaN à l'aide d'un élément de détection du courant, d'un dispositif de décalage de niveau pour transmettre le signal au contrôleur et d'un circuit de détection. Cette méthode présente l'avantage de ne pas générer d'inductances et de résistances parasites qui affectent les performances du circuit, mais manque de précision essentiellement en raison de l'important coefficient de température du GaN.

Une troisième option consiste à sélectionner un étage de puissance eGaN intégré qui inclut une fonction de protection contre la surintensité (OCP). Cela élimine les inconvénients des deux approches décrites ci-dessus. Le LMG3411 de TI est un exemple de produit qui inclut cette fonctionnalité. Le circuit de protection du LMG3411 peut désactiver les transistors HEMT eGaN en moins de 100 ns en cas de détection de surintensité. Lorsque l'entrée PWM revient à l'état bas lors du cycle suivant, le signal d'erreur de sortie est supprimé. Cela permet au transistor HEMT eGaN de s'activer normalement lors du cycle suivant, ce qui réduit les perturbations au niveau de la sortie.

|

Tableau : Résumé des options de protection contre la surintensité pour les étages de puissance HEMT GaN. La sélection d'un étage de puissance avec une protection intégrée contre la surintensité est la solution la plus simple pour un concepteur qui commence à utiliser cette technologie. (Source de l'image : Texas Instruments)

Conclusion

Avec la demande croissante en matière d'alimentations à découpage à haute densité d'énergie pour les applications telles que les onduleurs solaires et les batteries de serveurs, combinée à la diminution du coût par dispositif, les transistors HEMT eGaN se présentent comme une option attractive pour un plus large éventail de conceptions d'alimentation. Si la conception avec des transistors HEMT eGaN peut s'avérer complexe, l'introduction d'étages de puissance HEMT eGaN intégrant les circuits d'attaque de grille avec les transistors de puissance a permis aux concepteurs d'alimentation à découpage d'incorporer beaucoup plus facilement la technologie dans leur nouvelle conception à haute densité de puissance.

Référence

- « Input and Output Capacitor Selection », Jason Arrigo, Texas Instruments, rapport d'application SLTA055, février 2006.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.