L'extension atomique RISC-V offre des capacités supérieures en termes de manipulation de bits

L'adoption de l'architecture RISC-V s'accélère, et pour de bonnes raisons, son influence au sein de l'industrie s'accroît.

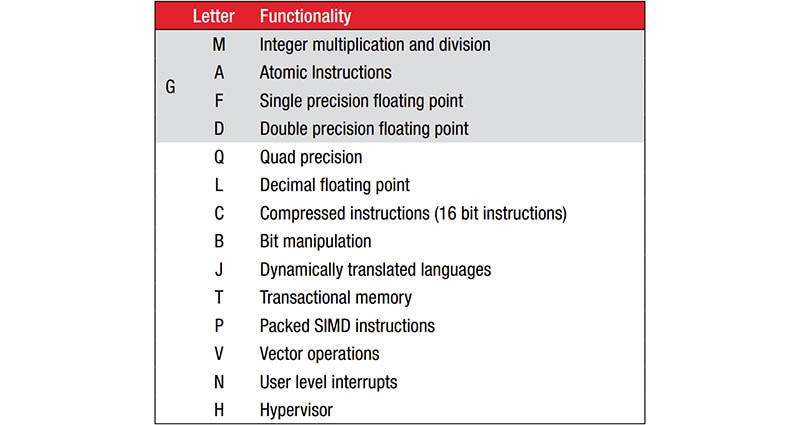

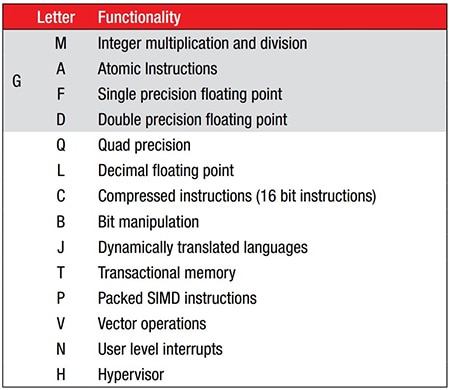

Outre l'architecture de base et son architecture de jeu d'instructions (ISA) vraiment réduite, elle est aussi enrichie par une série d'extensions normalisées (Figure 1). Par exemple, un cœur RISC-V 32 bits (RV32) qui prend en charge les instructions de virgule flottante simple précision ainsi que les instructions comprimées serait désigné RV32FC, conformément à la liste d'extensions ci-dessous.

Figure 1 : L'architecture de jeu d'instructions RISC-V est enrichie par une série d'extensions d'instructions normalisées, désignées par un suffixe sous forme de lettre après le nom du cœur. (Source de l'image : RISC-V.org)

Figure 1 : L'architecture de jeu d'instructions RISC-V est enrichie par une série d'extensions d'instructions normalisées, désignées par un suffixe sous forme de lettre après le nom du cœur. (Source de l'image : RISC-V.org)

Pour de nombreuses applications d'intelligence artificielle (IA) et d'apprentissage automatique (ML), ainsi que pour les systèmes embarqués avancés, les quatre extensions indispensables sont la multiplication et la division de nombres entiers (M), les instructions atomiques (A), la virgule flottante simple prévision (F) et la virgule flottante double précision (D). Cependant, au lieu de désigner un cœur sous le nom RV32MAFD, toutes ces extensions sont regroupées sous le suffixe G, comme dans RV32G.

Pour en savoir plus sur les différentes extensions et sur RISC-V en général, consultez le livre numérique sur RISC-V de DigiKey, disponible sur le site EDU.

Pour ma part, étant donné que ma première expérience avec les processeurs était liée aux systèmes embarqués profonds, j'ai tendance à regarder de près la capacité d'une architecture à manipuler les bits en lecture-modification-écriture dans la mémoire de données. Pour ces applications, la configuration et l'effacement de bits des sémaphores et des registres périphériques sont des opérations très courantes. Sans instructions natives de manipulation de bits, un cœur devrait copier le contenu des emplacements de mémoire de données vers un registre de base et configurer, effacer ou activer/désactiver les bits à l'aide, respectivement, des instructions OR, AND ou XOR, puis stocker le résultat à l'emplacement initial dans la mémoire de données. Non seulement cela prend plus de temps, mais, dans certains cas, j'ai également constaté un gonflement du code allant jusqu'à 20 % pour certaines applications de commande embarquées.

Pour certaines applications, le gonflement du code et la diminution des performances peuvent être acceptables. Cependant, lors du traitement de ces trois instructions, une interruption peut brutalement mettre fin à la commande par programme. Pire encore, dans un système à plusieurs processeurs, un autre cœur peut lire les données à ce même emplacement mémoire. La désactivation des interruptions ou le verrouillage de la mémoire pour éviter que ces événements ne viennent corrompre la mémoire de données nécessite des instructions supplémentaires et entraîne des complications qui peuvent générer des problèmes de performances.

Arm a essayé de résoudre ces problèmes en implémentant le bit-banding, qui fonctionne pour les opérations de bits simples. Toutefois, selon moi, RISC-V a implémenté une solution plus élégante et plus souple.

Qu'est-ce qui rend l'extension atomique aussi élégante ?

L'extension RISC-V A (atomique) prend en charge deux opérations : une instruction Load-Reserved/Store-Conditional, qui ne sera pas abordée ici, et une instruction binaire/au niveau du bit, qui permet une manipulation de bit simple dans la mémoire de données. Tandis que l'extension de manipulation de bits RISC-V B prend en charge une série d'instructions complexes de commande par bit, l'extension atomique ne cible pas uniquement les systèmes à plusieurs processeurs. Elle est également utile dans les systèmes embarqués plus petits où les besoins en matière de manipulation de bits sont plus simples. Le module RISC-V 64 bits double cœur 114991684 de Seeed Technology fait partie de ces systèmes. Il possède deux cœurs RV64GC qui doivent travailler ensemble et collaborer avec leur mémoire SRAM partagée de données.

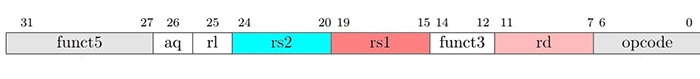

Le format de l'opération de mémoire atomique de l'extension RISC-V A est illustré à la Figure 2.

Figure 2 : Le format d'instruction de l'opération de mémoire atomique de RISC-V prend en charge les opérations binaires atomiques dans la mémoire de données avec une seule instruction. (Source de l'image : RISC-V.org, améliorée par Bill Giovino)

Figure 2 : Le format d'instruction de l'opération de mémoire atomique de RISC-V prend en charge les opérations binaires atomiques dans la mémoire de données avec une seule instruction. (Source de l'image : RISC-V.org, améliorée par Bill Giovino)

L'opération de mémoire atomique est une puissante instruction de lecture/modification/écriture qui prend en charge diverses opérations binaires directement dans la mémoire de données indiquée dans rs1 avec une seule instruction. En référence à la Figure 2, cette opération charge le contenu de l'emplacement de l'adresse mémoire de données dans rs1 et stocke la valeur dans le registre rd. Elle effectue ensuite une opération binaire sur la valeur de rd avec la valeur dans rs2, puis stocke ce résultat dans le registre initial rd et à l'emplacement initial de l'adresse mémoire de données dans rs1.

Les opérations au niveau du bit prises en charge sont les suivantes : OR (configuration de bit), AND (effacement de bit) et XOR (activation/désactivation de bit). Cela permet la manipulation atomique d'un ou de plusieurs bits directement dans la mémoire de données. Cela permet également d'éviter les conflits de mémoire lorsque les deux cœurs RV64GC utilisent la même adresse mémoire au même moment. C'est extrêmement utile pour les petites applications embarquées lors de la configuration des registres périphériques en mémoire et pour simplifier les opérations de sémaphore.

D'autres opérations sont prises en charge par l'opération de mémoire atomique RISC-V : valeurs maximale et minimale de nombre entier, et permutation. L'instruction binaire ADD est également prise en charge et permet une addition binaire directe, notamment l'incrémentation directe d'un compteur dans la mémoire de données.

Le cœur RV64 prend en charge à la fois les opérations 32 bits et 64 bits. Pour la manipulation de bits avec le RV64, il est important que celui-ci n'opère que sur les données 64 bits, car l'opération entraîne une extension du signe des données 32 bits placées dans rd.

Conclusion

L'architecture de jeu d'instructions RISC-V est la première concurrente sérieuse à venir défier l'architecture de jeu d'instructions Arm. Ses extensions d'architecture de jeu d'instructions offrent une méthode normalisée permettant d'améliorer le cœur avec des instructions qui peuvent accroître les performances d'une application de manière rentable. Je suis particulièrement conquis par l'extension atomique en option.

Utile et presque indispensable pour les systèmes à plusieurs processeurs, l'extension atomique est également un moyen efficace de permettre un contrôle de la manipulation de bits directement dans la mémoire de données. Cela offre un avantage considérable par rapport à de nombreuses architectures existantes en réduisant la taille du code et en améliorant les performances.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum