L'extension de multiplication RISC-V ajoute une multiplication 32 bits efficace à l'architecture RV32I

L'architecture de jeu d'instructions (ISA) RISC-V a vu le jour à Berkeley en 2010. Même si RISC signifie Reduced Instruction Set Computer/Core (ordinateur/cœur à jeu d'instructions réduit), les fabricants ne peuvent pas résister à l'envie de prendre une architecture ISA RISC et d'y ajouter une instruction par-ci et un nouveau mode d'adressage par-là, remplissant ainsi la carte de code opération jusqu'à ce que le jeu d'instructions soit complexe (CISC) plutôt que réduit (RISC). Mais les développeurs de RISC-V de Berkeley ont tenu à ce que leur cœur reste un véritable cœur à jeu d'instructions réduit. L'architecture ISA RISC-V RV32I a été conçue pour ne comporter que 47 instructions de base (un nombre particulièrement cher au cœur des fans inconditionnels de Star Trek), et 11 ans plus tard, ce nombre n'a pas changé.

La philosophie originale qui se cache derrière cette volonté de conserver un faible nombre d'instructions de base est la suivante : une instruction CISC complexe peut être reproduite en tant que série d'instructions RISC simples. D'après mon expérience, c'est l'application qui détermine si cela augmente ou non l'efficacité du code et réduit ou non sa taille. Par le passé, c'était sans doute le cas. À tel point qu'Arm a ajouté des instructions complexes à la carte de code opération.

Les instructions supplémentaires peuvent aider à améliorer les performances, mais les choses se compliquent lorsque vous avez un cœur 32 bits avec des instructions 32 bits : vous voulez en effet ajouter la possibilité de compresser quelques instructions 32 bits en instructions 16 bits pour gagner de la place. Cependant, pour ajouter des instructions 16 bits, le cœur doit disposer d'un espace supplémentaire sur la carte de code opération pour accueillir ces instructions compressées, et l'ajout d'instructions CISC réduit le nombre de codes opérations disponibles.

C'est là que l'avantage de RISC-V devient flagrant. Arm a ajouté le format d'instructions compressées Thumb2 plus tard et a intégré ces instructions 16 bits dans l'architecture ISA existante en ajoutant une architecture ISA 16 bits distincte. À l'inverse, l'architecture ISA RISC-V a été conçue dès le départ avec une option pour les instructions compressées et ne présente donc qu'une seule architecture ISA. Cela permet de conserver un cœur simple et efficace, et de simplifier la conception et les tests de semi-conducteurs.

Améliorer l'architecture ISA RISC-V RV32I avec une instruction de multiplication

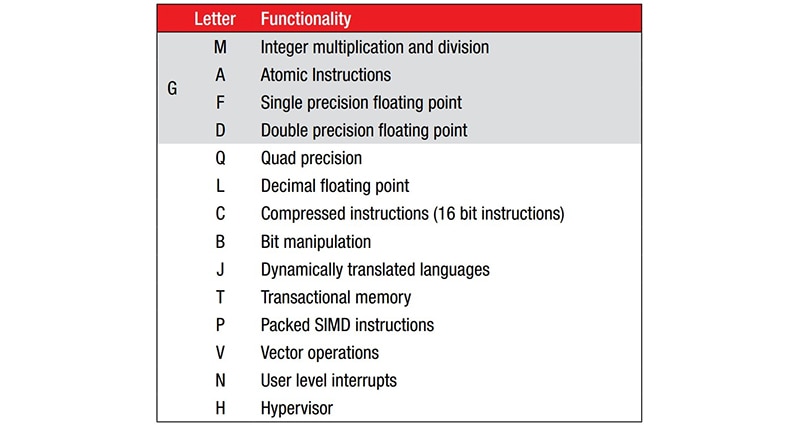

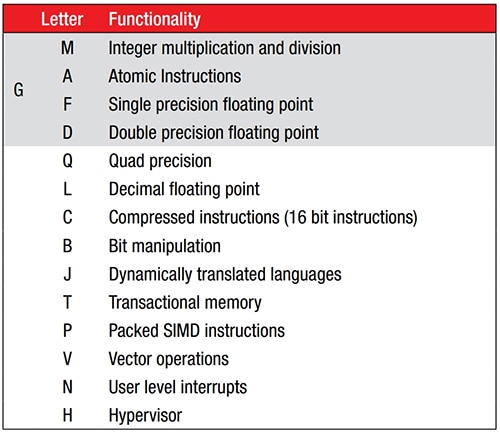

Les fabricants peuvent développer l'architecture ISA à 47 instructions en ajoutant des extensions d'instructions standardisées (Figure 1). Étant donné que l'architecture ISA de base n'a pas d'instructions de multiplication ou de division, l'extension M fournit cette fonctionnalité. Par exemple, une architecture RV32I avec l'extension M serait désignée RV32IM.

Figure 1 : L'architecture ISA RISC-V de base à 47 instructions peut être développée en ajoutant des extensions d'instructions standardisées, indiquées par un suffixe sous forme de lettre après le nom du cœur. (Source de l'image : RISC-V.org)

Figure 1 : L'architecture ISA RISC-V de base à 47 instructions peut être développée en ajoutant des extensions d'instructions standardisées, indiquées par un suffixe sous forme de lettre après le nom du cœur. (Source de l'image : RISC-V.org)

Le RED-V Thing Plus de SparkFun Electronics, avec un microcontrôleur RISC-V 32 bits open-source 150 mégahertz (MHz) Freedom E310 (FE310), est un exemple de cœur avec l'extension M. Le cœur FE310 est désigné comme étant un RV32IMAC. Outre sa capacité de calcul de base avec des nombres entiers (I), les extensions de la Figure 1 montrent qu'il prend en charge la multiplication de nombres entiers (M), les instructions atomiques (A) et les instructions compressées (C).

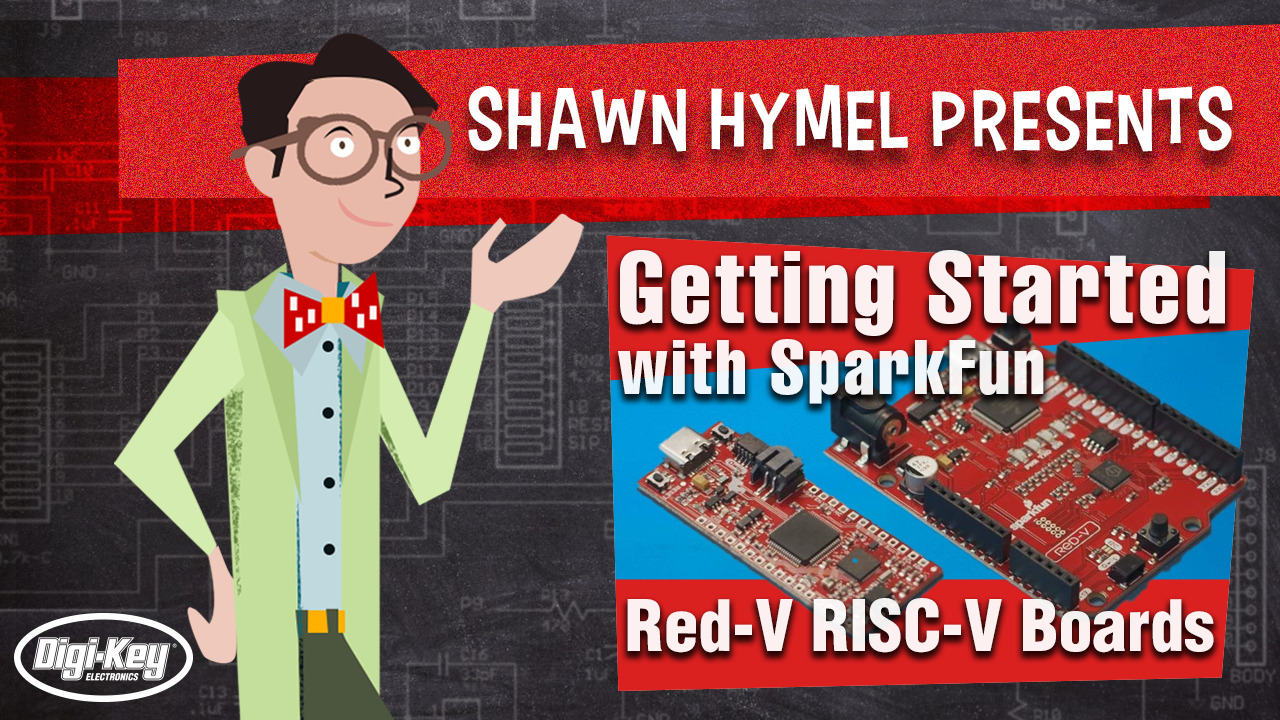

La carte d'évaluation RISC-V RED-V DEV-15799 de SparkFun (Figure 2) est dotée de 32 méga-octets (Mo) de mémoire programme Flash QSPI et d'un connecteur USB-C qui permet de communiquer avec un ordinateur hôte pour l'alimentation, la programmation et le débogage. Il y a aussi un connecteur supplémentaire qui peut être utilisé pour relier une batterie pour l'alimentation.

Figure 2 : La carte DEV-15799 de SparkFun est utilisée pour évaluer le cœur RISC-V FE310 RV32IMAC open-source 150 MHz. Elle communique avec un ordinateur hôte via une interface USB-C. (Source de l'image : SparkFun Electronics)

Figure 2 : La carte DEV-15799 de SparkFun est utilisée pour évaluer le cœur RISC-V FE310 RV32IMAC open-source 150 MHz. Elle communique avec un ordinateur hôte via une interface USB-C. (Source de l'image : SparkFun Electronics)

L'extension M ajoute des instructions de division 32/32 signées et non signées (DIV et DIVU), ainsi que des instructions de reste signées et non signées (REM et REMU). Elle ajoute également quatre instructions de multiplication :

- MUL effectue une multiplication de registre 32 x 32 et stocke les 32 bits inférieurs du résultat 64 bits dans un registre.

- MULH et MULHU effectuent une multiplication de registre signée et non signée, respectivement, et stockent les 32 bits supérieurs du résultat 64 bits dans un registre.

- MULSHU effectue une multiplication de registre signée x non signée et stocke les 32 bits supérieurs du résultat 64 bits dans un registre.

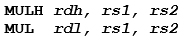

Pour une multiplication non signée 32 x 32 = 64, la séquence de code recommandée est donc la suivante :

Où les registres rs1 et rs2 sont le multiplicande et le multiplicateur, et où les registres rdh et rdl sont les résultats 32 bits supérieurs et inférieurs, respectivement.

En divisant le résultat de la multiplication 64 bits en deux opérations 32 bits, l'architecture ISA n'a pas besoin d'ajouter d'instruction CISC complexe 32 x 32 = 64. Cela est cohérent avec la philosophie RISC qui consiste à utiliser des instructions simples pour effectuer des opérations CISC.

Alors que la plupart des instructions de l'architecture ISA RV32I de base s'exécutent en un seul cycle d'horloge d'instruction, ces instructions de multiplication dans le RED-V FE310 nécessitent cinq cycles. En suivant ce raisonnement, la séquence de code recommandée ci-dessus nécessite dix cycles d'horloge. Même si cela peut être acceptable à 150 MHz, j'ai déjà vu des applications de microcontrôleur très basse consommation et à faible fréquence d'horloge où les interruptions sont si critiques qu'une multiplication sur dix cycles à 5 MHz est trop longue pour attendre une interruption cruciale. Dans ces cas, il arrive que les développeurs de micrologiciel effectuent la multiplication à l'aide d'une sous-routine d'assemblage complexe qui peut être interrompue.

Toutefois, le cœur FE310 est capable de prendre des instructions consécutives et de les fusionner en interne en une seule instruction plus rapide via la fusion de macro-opérations. La micro-architecture du cœur peut fusionner les deux instructions en une seule instruction interne qui s'exécute plus vite qu'en dix cycles. La micro-architecture RISC-V le fait automatiquement pour certaines séquences de code comme les charges indexées ou les instructions de charge de paire et de stockage de paire, ce qui améliore considérablement la vitesse d'exécution. Encore mieux, comme le FE310 prend en charge l'extension C lorsque deux instructions compressées 16 bits compatibles peuvent être fusionnées, il peut offrir des avantages à la fois en termes de code et de vitesse d'exécution.

Alors qu'Arm a ajouté la fusion de macro-opérations plus tard dans ses architectures, comme les instructions compressées, l'architecture RISC-V a été conçue dès le départ avec la fusion de macro-opérations. La meilleure manière de bien comprendre les avantages de la compression du code et de la fusion de macro-opérations est d'observer ces comportements avec une carte d'évaluation comme la carte DEV-15799 de SparkFun. Le code peut être examiné dans le débogueur pour voir comment la micro-architecture FE310 récupère et exécute chaque instruction. Cela permet de mieux comprendre le comportement du langage d'assemblage, ce qui peut aider à écrire du code efficace avec un compilateur C prenant en charge la compression du code et la fusion de macro-opérations.

Conclusion

L'architecture ISA RISC-V s'élève fièrement au rang de jeu d'instructions vraiment réduit, avec seulement 47 instructions de base. Elle peut être améliorée avec des extensions standardisées comme l'extension de multiplication M qui ajoute des instructions de multiplication et de division. La fusion de macro-opérations, qui est inhérente à l'architecture RISC-V, peut accélérer l'exécution du code pour les instructions compatibles comme des instructions de multiplication consécutives, tandis que l'extension compressée C réduit la taille du code. Les instructions compressées et la fusion de macro-opérations offrent des avantages considérables en termes de performances par rapport aux autres architectures.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum