Exploiter le code de dénomination RISC-V

L'architecture de jeu d'instructions (ISA) RISC-V offre une opportunité unique. Sa structure permet aux développeurs d'utiliser des processeurs avec un large éventail de tailles et de performances offrant une compatibilité logicielle sans précédent. L'élément clé pour tirer parti de cette compatibilité est la compréhension du code de dénomination de cœur RISC-V.

Contrairement à la plupart des architectures de processeur, RISC-V est open-source et les développeurs peuvent l'utiliser sans frais de licence ou de droits. De plus, l'architecture de jeu d'instructions est conçue pour être flexible, ce qui permet aux développeurs de choisir les blocs d'instructions qu'ils souhaitent implémenter et d'ignorer ceux dont ils n'ont pas besoin, et même d'ajouter des instructions personnalisées si nécessaire. L'objectif est de stimuler le développement de plusieurs cœurs de processeur avec différents attributs de taille et de performances, mais qui partagent une base commune.

Cette base commune fournit un niveau élevé de compatibilité logicielle entre les processeurs, indépendamment de leurs ensembles de fonctionnalités. Le code pour un processeur RISC-V minimal implémentant uniquement le jeu d'instructions d'entiers, par exemple, s'exécutera sans être modifié sur un processeur plus puissant doté de capacités de nombres entiers et de virgule flottante. Le code qui utilise les instructions en virgule flottante ne s'exécutera évidemment pas sur une machine d'entiers uniquement, mais ne provoquera pas non plus de plantage du processeur. Les instructions non implémentées généreront simplement une interruption d'instruction illégale.

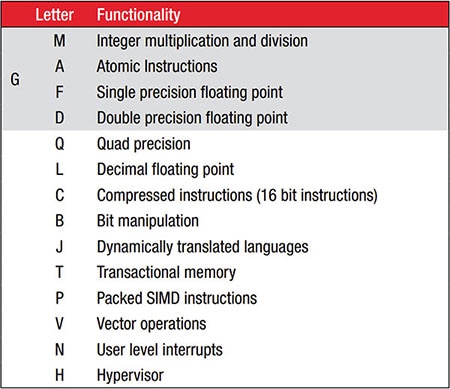

L'architecture de jeu d'instructions RISC-V atteint cette flexibilité en partitionnant ses instructions en groupes essentiellement indépendants ayant des codes machines qui ne se chevauchent pas. Ces groupes d'instructions sont appelés « extensions standard », et l'architecture de jeu d'instructions a défini de nombreuses extensions standard de ce type qui fournissent la plupart des fonctionnalités dont les développeurs peuvent avoir besoin. Chaque extension standard est identifiée par un code lettre. L'extension standard « M », par exemple, fournit des instructions pour la multiplication ou la division de deux nombres entiers contenus dans des registres. De même, l'extension standard « F » fournit des instructions pour des opérations en virgule flottante à simple précision.

Étant donné que les développeurs de processeur peuvent combiner des extensions standard lors de l'implémentation d'un cœur RISC-V, les utilisateurs devront lire attentivement les spécifications et autres manuels de programmation pour déterminer ce que le processeur sélectionné peut réellement faire. Mais il y a une solution plus simple. RISC-V utilise une convention de numérotation de cœur qui indique immédiatement aux utilisateurs les capacités du cœur.

La convention de numérotation commence par la spécification de base. RISC-V a défini quatre spécifications de base :

- RV32I inclut un jeu d'instructions d'entiers 32 bits et offre 32 registres à usage général

- RV32E utilise un jeu d'instructions 32 bits ciblant les applications embarquées avec 16 registres

- RV64I inclut un jeu d'instructions d'entiers 64 bits avec 32 registres

- RV128I inclut un jeu d'instructions d'entiers 128 bits avec 32 registres

Ces spécifications de base définissent un processeur rudimentaire, mais entièrement opérationnel. Cependant, la plupart des développeurs choisiront d'ajouter une ou plusieurs extensions de jeu d'instructions standard à leur conception. Ces extensions standard et les lettres qui les identifient sont répertoriées à la Figure 1.

Figure 1 : Les extensions de jeu d'instructions standard pour les processeurs RISC-V utilisent des codes lettres pour indiquer leur présence dans la convention de numérotation d'un cœur. (Source de l'image : DigiKey Electronics)

Figure 1 : Les extensions de jeu d'instructions standard pour les processeurs RISC-V utilisent des codes lettres pour indiquer leur présence dans la convention de numérotation d'un cœur. (Source de l'image : DigiKey Electronics)

Une désignation de cœur RISC-V complète indique la spécification de base avec les lettres des extensions standard qu'elle implémente, dans l'ordre indiqué à la Figure 1. Un petit système sur puce (SoC) utilisant des ressources minimales peut par exemple présenter la désignation RV32EMAB. Cela signifie que le cœur implémente le jeu d'instructions d'entiers 32 bits pour les dispositifs embarqués, possède 16 registres et exécute la multiplication et la division de nombres entiers, ainsi que des instructions atomiques. Il n'inclut aucun calcul en virgule flottante, mais prend en charge la manipulation de bits.

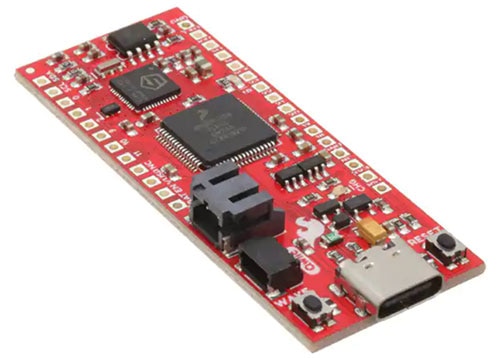

Ainsi, lorsqu'ils choisissent une puce RISC-V pour leur conception, les utilisateurs n'ont qu'à regarder la désignation du cœur pour comprendre les fonctionnalités qu'il fournit. Par exemple, le processeur de la carte d'évaluation DEV-15799 FE310 Thing Plus RISC-V de SparkFun Electronics est répertorié en tant que cœur RV32IMAC (Figure 2).

Figure 2 : Le processeur RISC-V de la carte DEV-15799 porte la dénomination RV32IMAC, ce qui signifie, entre autres fonctionnalités, qu'il est doté d'un jeu d'instructions d'entiers 32 bits et de 32 registres, et qu'il offre des instructions atomiques. (Source de l'image : SparkFun Electronics)

Figure 2 : Le processeur RISC-V de la carte DEV-15799 porte la dénomination RV32IMAC, ce qui signifie, entre autres fonctionnalités, qu'il est doté d'un jeu d'instructions d'entiers 32 bits et de 32 registres, et qu'il offre des instructions atomiques. (Source de l'image : SparkFun Electronics)

Cela signifie qu'il dispose d'un jeu d'instructions d'entiers 32 bits et de 32 registres, qu'il implémente la multiplication et la division de nombres entiers, qu'il offre des instructions atomiques et qu'il prend en charge les instructions compressées (16 bits) pour réduire l'espace dédié au code. Tout code développé sur cette carte pourra être exécuté sur n'importe quel autre cœur RV32I avec les extensions standard de multiplication et d'accumulation (MAC) également.

Autre exemple : le module SoC 114991684 Sipeed MAXIX-I RISC-V de Seeed Technology présente son cœur RISC-V en tant que RV64IMAFDC. Il inclut un jeu d'instructions 64 bits avec multiplication et division de nombres entiers, instructions atomiques, virgule flottante à simple et double précision, et instructions compressées. Le code développé pour ce processeur devrait pouvoir s'exécuter sur n'importe quel processeur RISC-V avec les mêmes désignations de cœur, mais le mappage mémoire des périphériques et autres devra peut-être être ajusté.

Conclusion

Avec le code de dénomination RISC-V en main, les utilisateurs peuvent commencer à tester en toute confiance cette architecture puissante. En faisant correspondre les codes de cœur, les utilisateurs peuvent être sûrs que leurs efforts de programmation pour un processeur donné seront clairement utilisables sur d'autres processeurs RISC-V.

Le guide RISC-V, qui présente la configuration initiale et l'utilisation de plusieurs cartes d'évaluation RISC-V différentes, constitue un excellent point de départ.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum