Analog-Grundlagen - Teil 1: SAR-Analog-Digital-Wandler

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-04-15

Anmerkung der Redaktion: Analog-Digital-Wandler (ADCs) verbinden die analoge mit der digitalen Welt und sind somit eine grundlegende Komponente jedes elektronischen Systems, das eine Verbindung zur realen Welt herstellt. Sie sind auch ein entscheidender Bestimmungsfaktor für die Leistung eines Systems. In dieser Reihe werden die Grundlagen der ADCs, ihre verschiedenen Arten und ihre Anwendung untersucht. Hier, in Teil 1 dieser Serie über analoge Grundlagen, werden sukzessive Approximationsregister (SAR) ADCs diskutiert. In Teil 2 werden delta-sigma (ΔƩ) Konverter diskutiert.

Es ist immer noch eine analoge Welt, also muss eine Art Konvertierung stattfinden, um die erfassten Informationen in die digitale Domäne zu bekommen. Diese schwere Arbeit ist in erster Linie dem Analog-Digital-Wandler (ADC) vorbehalten. Die drei ADC-Topologien, die im Laufe der Jahre erfolgreich in den Vordergrund gerückt sind, sind der SAR- (Sukzessives Approximationsregister), der Sigma-Delta- (S-D) und der Pipeline-ADC. Alle drei ADC-Topologien unterscheiden sich grundlegend voneinander, um in unterschiedlichen Frequenzbereichen zu arbeiten und alles von Niederfrequenz-Sensoranwendungen bis hin zu höherfrequenter LiDAR- oder Satellitenkommunikation und darüber hinaus zu bedienen.

Der SAR ADC war der erste Konverter, der sich als Mainstream durchsetzte. Im Laufe der Zeit tauchte diese Wandlertopologie in einer Vielzahl von Anwendungen auf, darunter Prozesssteuerung, medizinische und frühe digitale Audiosysteme. Diese Anwendungen profitieren von den Ausgangswandlungsbereichen des SAR ADC von 8 bis 20 Bit. Der Ruhm des SAR ADC besteht jedoch darin, dass es eine Momentaufnahme des analogen Eingangssignals aufnimmt und mehrere Signalmomentaufnahmen verwendet, um ein Bild über die Zeit zu zeichnen.

Dieser Artikel beschreibt kurz die Signalkette, die den SAR ADC umgibt. Von dort aus vertieft sie diese ADC-Topologie mit einer Analyse der grundlegenden Eingangsstufe, die für die Momentaufnahmeaktion des ADC verantwortlich ist. Der Artikel stellt dann beispielhafte SAR-ADC-Lösungen vor - die AD7625BCPZ und AD4020BCPZ-RL7 von Analog Devices - und konzentriert sich dabei auf die interne Analog-Digital-Wandlermechanik des ADC4020BCPZ-RL7. Außerdem werden Schlüsselspezifikationen für ein geeignetes Datenerfassungssystem bereitgestellt.

Die analoge Signalkette des SAR ADC

Das SAR ADC erscheint in Systemen wie automatischen Testgeräten, Maschinenautomatisierung, medizinischen Geräten und Präzisionsdatenerfassung. Bei allen SAR ADC-Anwendungen gibt es ein analoges Signal, das eine digitale Darstellung mit einer bescheidenen Auflösung von 8 bis 20 Bit erfordert, mit einer Abtastung von nahezu DC bis 15 Megasamples pro Sekunde (MSPS) (zum Zeitpunkt der Erstellung dieses Artikels).

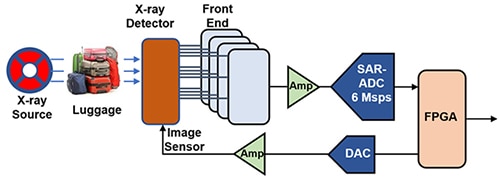

Der SAR ADC ist sehr gut in der Lage, ohne eine analoge Front-End-Signalkette (AFE) zu arbeiten. Wenn die Aufgabe des Konstrukteurs jedoch auch darin besteht, ein Signal am Front-End des SAR ADC erfolgreich zu präsentieren, ist eher ein gewisses Maß an Signalkonditionierung erforderlich (Abbildung 1).

Abbildung 1: Diese Beispiel-SAR-ADC-Signalkette enthält einen Röntgendetektor, AFE, einen Verstärkertreiber, den MSPS-Konverter AD7625BCPZ 6 von Analog Device und eine digitale Buchse für die Konvertierungsergebnisse (den FPGA). (Bildquelle: DigiKey)

Abbildung 1: Diese Beispiel-SAR-ADC-Signalkette enthält einen Röntgendetektor, AFE, einen Verstärkertreiber, den MSPS-Konverter AD7625BCPZ 6 von Analog Device und eine digitale Buchse für die Konvertierungsergebnisse (den FPGA). (Bildquelle: DigiKey)

In der Abbildung sendet eine Röntgenquelle ein Signal durch das Gepäckstück zum Röntgendetektor. Die Aufgabe des Röntgengeräts besteht darin, in kurzer Zeit ein vollständiges Bild des Gepäcks zu erstellen, um die Frustration der Reisenden zu verringern.

Das Front-End nimmt das Detektorsignal auf und führt Signalkonditionierungsfunktionen wie analoge Verstärkung und Pegelverschiebung aus. Das Signal wird dann an den SAR-ADC weitergeleitet, in diesem Fall an den AD7625BCPZ von Analog Devices.

Der Verstärker vor dem SAR-ADC bietet eine angemessene Stabilität, normalerweise mit einem Tiefpassfilter erster Ordnung zwischen dem Verstärker und dem SAR-ADC. Der SAR ADC ist in der Lage, mit bis zu 6 MSPS - eine Probe alle 167 Nanosekunden (ns) - abzutasten, um mehrere Momentaufnahmen in kurzer Zeit zu ermöglichen.

Kern der SAR-ADC-Eingangsstufe vereinfacht

Der SAR-ADC hat im Laufe der Zeit zahlreiche Erweiterungen und Verbesserungen erfahren, aber in allen Fällen besteht die Hauptaktivität während der Umstellungsperiode in der Ladungsumverteilung - eine der häufigsten Umsetzungen des ADCs mit sukzessiver Annäherung. Außerdem gibt es beim SAR ADC im Gegensatz zum S-D- und Pipeline-Konverter den zusätzlichen Bonus einer Null-Latenzzeit.

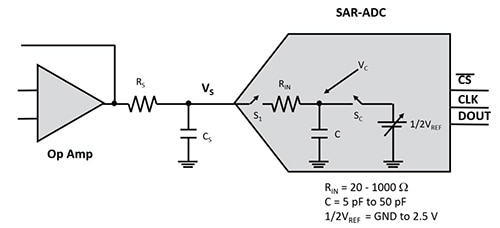

Auf der einfachsten Ebene ist leicht zu erkennen, wo die Signalmomentaufnahme entsteht. Der SAR-ADC-Eingangskern enthält einen Eingangssignalerfassungsschalter (S1), ein kapazitives Array, einen Umwandlungsschalter (SC) und eine interne Referenzspannung (½ VREF) (Abbildung 2).

Abbildung 2: Ein Operationsverstärker (Operationsverstärker) mit einem Ausgangs-Stabilisierungsfilter, der einen SAR-ADC ansteuert. (Bildquelle: DigiKey)

Abbildung 2: Ein Operationsverstärker (Operationsverstärker) mit einem Ausgangs-Stabilisierungsfilter, der einen SAR-ADC ansteuert. (Bildquelle: DigiKey)

Die Funktionsweise des SAR ADC-Kerns ist wie folgt:

- S1 öffnet, SC schließt: Dadurch wird die Eingangsstufe von der analogen Signalquelle getrennt.

- Die Ladung von C wird neu auf ½ VREF kalibriert. Diese Rekalibrierung bringt den SAR ADC wieder auf den Nullpunkt.

- Dann schließt S1, SC öffnet: Jetzt ist das Gerät an das analoge Eingangssignal angeschlossen.

- Der SAR ADC erfasst das Eingangssignal, VS, über eine vorbestimmte Erfassungszeit. Diese Erfassungszeit berücksichtigt das Schaltrauschen von S1 und SC sowie die plötzliche Belastung des Verstärkers durch Kondensatorladung und Schaltrauschen.

- Dann öffnet sich S1: Dies ist genau der Zeitpunkt, an dem der Signal-Schnappschuss auftritt.

- Der SAR ADC wandelt das Signal bei VC in seine digitale Darstellung um. Die dafür benötigte Zeit ist die "Umstellungszeit".

Kerndetails der SAR ADC-Eingangsstufe

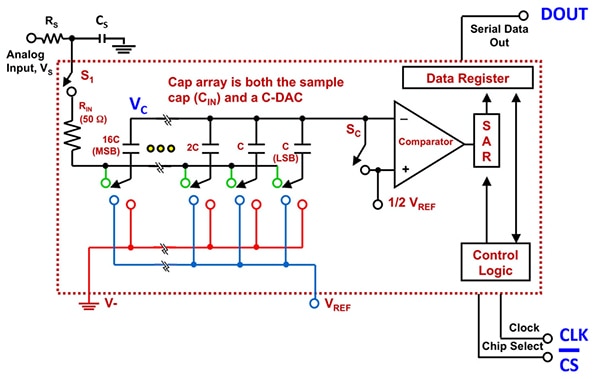

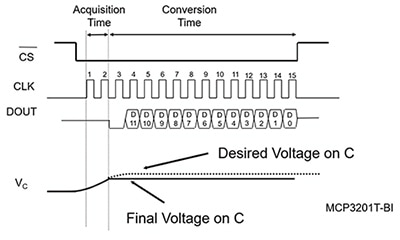

Der Konvertierungskern sorgt für die Ladungsumverteilung des erfassten Signals bei VC. Die Orchestrierung der Ladungsumverteilung des Wandlers findet im Kern statt, der von der Uhr gesteuert wird. Von diesem Prozess gelangt jeder getaktete digitale Ausgangscode an den DOUT-Ausgang des SAR ADC (Abbildung 3).

Abbildung 3: Ein 4-Bit-SAR-ADC-Vorhang verfügt über eine vollständige Reihe digital gewichteter Kondensatoren: 16C, 8C, 4C, 2C und zwei Cs. (Bildquelle: DigiKey)

Abbildung 3: Ein 4-Bit-SAR-ADC-Vorhang verfügt über eine vollständige Reihe digital gewichteter Kondensatoren: 16C, 8C, 4C, 2C und zwei Cs. (Bildquelle: DigiKey)

Als erster Schritt bei der Konvertierung bestimmt der SAR-ADC-Algorithmus das höchstwertige Bit (MSB). Der SAR-ADC beginnt mit dem Testen der Signalstärke im Vergleich zu ½ VREF, indem er die Unterseite des 16C-Kondensators zwischen den V- und VREF-Komparatoreingängen umschaltet. Der nächste Vergleich in der SAR-ADC-Konvertierungslinie ist der Test von 8C (nicht gezeigt) gegen ½ VREF, gefolgt vom Test von 4C usw.

SAR-ADC-Ausgangskonvertierungsdetails

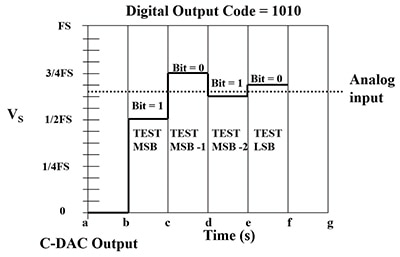

Die MSB-Entscheidung wird sofort über den DOUT-Pin übertragen, und der MSB-Schalter bleibt eingefroren, während die Entscheidung MSB 1 getroffen wird. Der SAR ADC führt diesen Algorithmus bis zur endgültigen Auswahl des niedrigstwertigen Bits (LSB) durch (Abbildung 4).

Abbildung 4: Der 4-Bit-SAR-ADC taktet den Umwandlungsalgorithmus durch Bit-Entscheidungen und überträgt diese Entscheidungen über den DOUT-Pin (in Abbildung 3 dargestellt). (Bildquelle: DigiKey)

Abbildung 4: Der 4-Bit-SAR-ADC taktet den Umwandlungsalgorithmus durch Bit-Entscheidungen und überträgt diese Entscheidungen über den DOUT-Pin (in Abbildung 3 dargestellt). (Bildquelle: DigiKey)

In Abbildung 4 werden die Entscheidungen über die getakteten Bits des SAR ADC vom MSB bis hinunter zum LSB getroffen. Alle Konvertierungsdaten werden weiterhin sofort durch DOUT oben rechts in Abbildung 3 ausgetaktet. Eine volle Durchsatzzeit erfordert in der Regel ausreichend Zeit für die Signalerfassung und einen Taktzyklus für jedes Bit.

SAR ADC-Konversionsherausforderungen

Der Konstrukteur muss sich der Signaleinregelzeit bewusst sein, die erforderlich ist, um sicherzustellen, dass der korrekte Analogwert aus der Umwandlung erfasst wird (Abbildung 5).

Abbildung 5: Das Umsetzungszeitdiagramm eines 12-Bit-SAR-DACs. Jede vollständige Konvertierung erfordert 16 Taktzyklen. (Bildquelle: DigiKey)

Abbildung 5: Das Umsetzungszeitdiagramm eines 12-Bit-SAR-DACs. Jede vollständige Konvertierung erfordert 16 Taktzyklen. (Bildquelle: DigiKey)

In Abbildung 5 hat das Eingangssignal, VC, seine gewünschte Endspannung nicht erreicht, bevor sich der Eingangsschalter des Wandlers öffnet. In diesem Fall hat sich der Schaltungsentwickler bei der Berechnung der Einschwingzeit des Verstärkereingangssignals verkalkuliert.

Der AD4020BCPZ-RL7 20-Bit, 1,8 MSPS SAR ADC vereinfacht die Komplexität der Signalerfassung, indem er eine verlängerte Erfassungsphase bietet und gleichzeitig die Durchsatzrate beibehält. Es hat einen niedrigen Signal-Rausch-Abstand (SNR) von 100,5 dB.

SAR ADC-Übertragungsfunktion

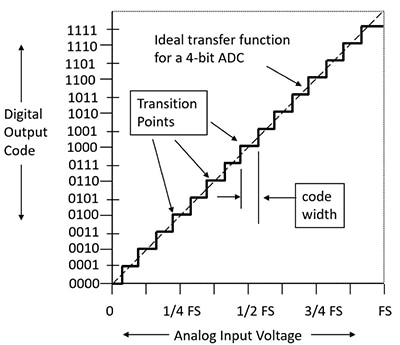

Die Anzahl der möglichen Codes für ADCs ist gleich 2N, wobei N die Anzahl der Bits ist. Beispielsweise stehen bei einem 4-Bit-Konverter 24 oder 16 separate Codes zur Verfügung (Abbildung 6).

Abbildung 6: Die Übertragungsfunktion oder der Graph des digitalen Ausgangscodes im Vergleich zur analogen Eingangsspannung eines idealen 4-Bit-SAR-ADCs sollte eine gerade Linie sein. (Bildquelle: DigiKey)

Abbildung 6: Die Übertragungsfunktion oder der Graph des digitalen Ausgangscodes im Vergleich zur analogen Eingangsspannung eines idealen 4-Bit-SAR-ADCs sollte eine gerade Linie sein. (Bildquelle: DigiKey)

Das Bild malen

Die Durchsatzrate des SAR-ADC umfasst die Erfassungs- und Konvertierungszeit, um Durchsatzraten von bis zu 1,8 MSPS bei einer Auflösung von 20 Bit vom AD4020BCPZ-RL7 von Analog Devices zu erreichen. Mit der Durchsatzgeschwindigkeit des AD4020BCPZ-RL7 ist es möglich, mehrere Schnappschüsse zu erfassen und eine digitale Bildwiedergabe-Lösung für Maschinenautomatisierung und medizinische Geräte zu erstellen.

Fazit

Der SAR ADC wird in Anwendungen von der Prozesssteuerung bis hin zu medizinischen und Verbraucheranwendungen eingesetzt und erweist sich aufgrund seiner Fähigkeit, Momentaufnahmen von Signalen zu erstellen und die Auflösung und Geschwindigkeit ständig zu verbessern, weiterhin als wertvoll. Der SAR ADC verfügt derzeit über Auflösungen von acht bis 20 Bit, mit Durchsatzraten von bis zu 15 MSPS. Ein Beispiel, der AD4020BCPZ-RL von Analog Devices, bietet geringes Rauschen, hohe Geschwindigkeit und 20 Bit, 1,8 MSPS Präzision. Die Architektur des SAR-ADC-Wandlers ist jedoch noch nicht ausgereizt. Es wird noch mehr kommen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.