Implementierung von High-Power-PoE mit gebrauchsfertigen Lösungen für IEEE 802.3bt

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-05-09

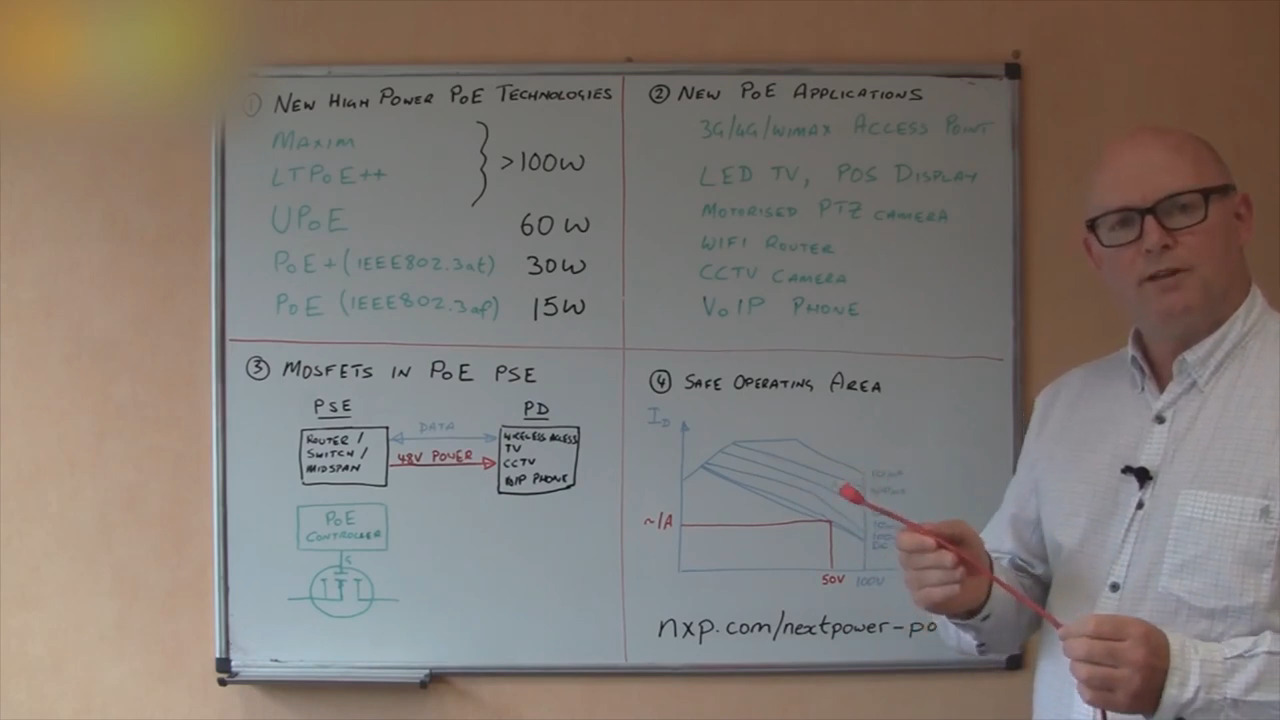

Seit der Einführung von Power over Ethernet (PoE) im Jahr 2003 hat sich dessen Fähigkeit zur Stromversorgung von ursprünglich 15,4 Watt auf bis zu 30 Watt erheblich gesteigert. Doch Entwickler benötigen für ihre Anwendungen noch mehr Leistung. Eine neue Ergänzung zur PoE-Spezifikation, IEEE 802.3bt, wird dieser Nachfrage gerecht und ermöglicht bis zu 60 Watt (und in einigen Anwendungen bis zu 90 Watt) an der Stromquelle.

Diese Ergänzung wurde erst Ende 2018 ratifiziert. Jetzt sind die ersten Bausteine mit integrierten PSE-Controllern (Power Sourcing Equipment) und PD-Schnittstellen (Powered Device) kommerziell erhältlich und ermöglichen Entwicklern die Nutzung der neuen Technik, die den Namen „High-Power-PoE“ trägt.

Dieser Artikel beschreibt, inwieweit sich IEEE 802.3bt von den bisherigen Versionen von PoE unterscheidet. Dann stellen wir neue Bausteine mit integrierten PSE-Controllern und PD-Schnittstellen von Microsemi, Texas Instruments (TI), Linear Technology und Nexperia vor. Und schließlich erläutert der Artikel, wie sich mithilfe dieser Bausteine ein System aufbauen lässt, bei dem wichtige Aspekte wie Schaltkreisschutz sowie Design- und Layout-Anforderungen berücksichtigt werden.

Was ist IEEE 802.3bt?

Beim ursprünglichen Standard (IEEE 802.3af) waren maximal 15,4 Watt an der Stromquelle spezifiziert. Das war völlig ausreichend für Anwendungen wie IP-Telefone und WLAN-Zugangspunkte – aber nicht für nachfolgende Anwendungen wie IP-Videotelefone oder PTZ-Kameras (Pan/Tilt/Zoom). Die Ergänzung des Standards im Jahr 2009 (IEEE 802.3at) löste das Problem, indem jetzt 30 Watt an der Stromquelle spezifiziert waren. Doch in den letzten Jahren stieg die Nachfrage nach noch mehr Leistung deutlich an, um per Ethernet vernetzte Anwendungen wie etwa POS-Terminals (Point-of-Sale), Zugangspunkte für IEEE 802.11ac und vernetzte LED-Beleuchtung zu ermöglichen.

Um dieser Nachfrage nach mehr Leistung gerecht zu werden, wurden bei der neuerlichen Ergänzung IEEE 802.3bt (High-Power-PoE) der bisherigen PoE- und PoE+-Standards die PSE-Mindestausgangsleistung sowie die PD-Mindesteingangsleistung erhöht. Die wichtigste Änderung ist, dass jetzt über alle vier verdrillten Leitungspaare in einem Cat5e-Ethernet-Kabel Strom übertragen werden kann. Bei PoE und PoE+ wurden nur zwei der verdrillten Leitungspaare verwendet: entweder die Datenleitungen (in Anwendungen laut „Alternative A“) oder die Ersatzleitungen (in Anwendungen laut „Alternative B“). (Siehe den Artikel „Eine Einführung in Power-over-Ethernet“ in der DigiKey-Bibliothek.)

Mit der neuen Spezifikation wurde auch die Einführung von „Typ 3“- und „Typ 4“-PSEs und -PDs möglich (die für 60 Watt bzw. 90 Watt ausgelegt sind) sowie zusätzliche Klassen (5-8) für die Ausgangs- und Eingangsleistung (Tabelle 1). Für den Entwickler sollte klar sein, dass diese Ergänzung so konzipiert ist, dass sie die Anforderungen der Norm ISO/IEC 60950 hinsichtlich der Begrenzung von Stromquelle und SELV (Safety Extra-Low Voltage) erfüllt. Diese Norm ISO/IEC 60950 schränkt die Leistung auf maximal 100 Watt pro Anschluss ein.

|

Tabelle 1: Vergleich von High-Power-PoE (IEEE 802.3bt) mit PoE (IEEE 802.3af) und PoE+ (IEEE 802.3at). Mit IEEE 802.3bt wurde die Leistung erhöht, und es wurden neue Arten von PSEs und PDs sowie neue Klassen eingeführt. (Quelle der Tabelle: Microsemi)

Verbesserungen durch IEEE 802.3bt

Neben der höheren Leistung, die mit High-Power PoE verfügbar wird, brachte die Spezifikation noch weitere neue Funktionen. Die wichtigsten Verbesserungen sind:

- Autoclass-Funktion

- Unterstützung von geringem Standby-Verbrauch

- Erweiterte Leistungskapazität, wenn die Kanal- bzw. Kabellänge bekannt ist

Die Autoclass-Funktion (kurz für „Automatic Classification“) ist ein neuer (optionaler) Klassifizierungsmechanismus, den es nur bei High-Power-PoE gibt. Diese Funktion ermöglicht einem PD, dem PSE seine effektive maximale Leistungsaufnahme zu kommunizieren. Dadurch kann das PSE das Leistungsbudget präzise an diesen Wert anpassen (plus eine gewisse Reserve für Kanalverluste und ein „Sicherheitsspielraum“) und so den Wirkungsgrad des Systems optimieren.

Zur Stromversorgung von Anwendungen mit strengen Anforderungen beim Standby-Stromverbrauch bietet High-Power-PoE eine wesentliche Änderung bei der minimalen Impulsstromdauer, mit der gewährleistet wird, dass das PSE weiterhin versorgt wird. Bisher verwendeten Typ-1- und Typ-2-PDs eine MPS (Maintain Power Signature), bestehend aus einem Impulsstrom von 10 Milliampere (mA) für mindestens 75 Millisekunden (ms) alle 325 ms und einer AC-Impedanz von unter 26,3 Kiloohm (kΩ) parallel zu 0,05 Mikrofarad (μF). Die Änderung im Rahmen der IEEE 802.3bt-Spezifikation (gültig für Typ-3- und Typ-4-PSEs) führt zu einer Impulsdauer von rund 10 Prozent gegenüber der für Typ-1- und Typ-2-PSEs.

Eine weitere wichtige Änderung ist die erweiterte Leistungskapazität. Das PD misst den Leitungswiderstand und berechnet den Leistungsverlust und damit die Leistungsreserve, die erforderlich ist, um das PD mit der Mindesteingangsleistung zu versorgen, die von der Spezifikation festgelegt ist. Im schlimmsten Fall entspricht diese der Leistungsreserve, die durch die vorherigen Ergänzungen spezifiziert wurde, doch in der Praxis ist sie wahrscheinlich geringer, sodass Energie gespart wird.

Der Einschaltprozess bei High-Power-PoE

Durch die Einführung von zusätzlichen vier Klassen von PSE-Ausgangsleistung (Klassen 5 bis 8) und der entsprechenden PD-Eingangsleistung zusammen mit zwei neuen Typen (Typ 3 und 4) bei PSEs und PDs wurde die Einschaltsequenz der Technologie noch komplexer. Dies muss von Entwicklern berücksichtigt werden, die High-Power-PoE-Systeme konzipieren, weil es Einfluss auf die Wahl der PSE-Controller haben kann.

Im Allgemeinen gilt ein Gerät, das mit IEEE 802.3af oder IEEE 802.3at konform ist, als ein Typ-1-Gerät (Klasse 0-3) oder Typ-2-Gerät (Klasse 4). Mit IEEE 802.3bt konforme Geräte gelten als Typ-3-Geräte (Klasse 5 und 6) oder Typ-4-Geräte (Klasse 7 und 8). High-Power-PoE-definiert eine Methode zur sicheren Versorgung eines PD über ein Kabel durch ein PSE, wobei die Stromversorgung ausgeschaltet wird, wenn ein PD vom Kabel getrennt wird.

IEEE 802.3bt gibt auch eine Einschaltstrom- und Zeitbegrenzung vor, um die Kompatibilität zwischen PSEs und PDs beliebiger Arten oder Klassen zu gewährleisten. Die Einschaltstromgrenze liegt für Klasse 0 bis 4 bei 400 mA bis 450 mA, für Klasse 5 bis 6 bei 400 mA bis 900 mA und für Klasse 7 bis 8 bei 800 mA bis 900 mA . Die PSE-Einschaltstromgrenze gilt für bis zu 75 ms nach dem Einschalten; danach unterstützen die PSEs von Typ 2, 3 oder 4 einen höheren Ausgangsstrom entsprechend der Klassifizierung.

Der High-Power-PoE-Einschaltprozess beginnt damit, dass das PSE die Stromversorgung abschaltet, während es überprüft, ob etwas an das Kabel angeschlossen ist. Dann klassifiziert das PSE das PD, bevor es den vom PD angeforderten Strom liefert – oder den maximalen Strom des PSE, wenn dieses nicht über die ausreichende Kapazität zur vollständigen Versorgung des PD verfügt. Es gibt noch einen vierten Betriebszustand, der von Typ-3- und Typ-4-PSEs verwendet wird, um zu prüfen, ob das PD die gleiche Klassifizierungssignatur auf jedem verdrillten Leitungspaar aufweist.

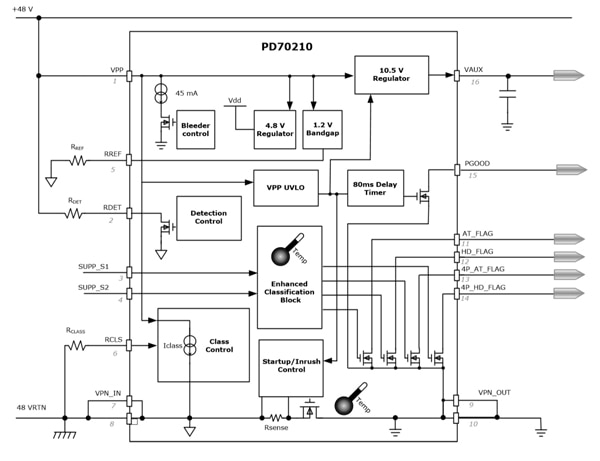

Weil es sich dabei um eine optionale Funktion handelt, unterstützen nicht alle High-Power-PoE-kompatiblen PSEs und PDs die Autoclass-Funktion. Daher muss das Datenblatt überprüft werden, wenn diese Funktion zur Spezifikation des vom Entwickler konzipierten Systems gehört. Der Frontend-PD-Schnittstellen-Controller PD70210ILD-TR von Microsemi ist ein Produkt, das mit seinem „Enhanced Classification Block“ diese Funktion bietet. Der PD70210ILD-TR erkennt auch, welche der vier Paare des Kabels tatsächlich Strom erhalten, und erzeugt entsprechende Flags (Abbildung 1).

Abbildung 1: Der Frontend-PD-Schnittstellen-Controller PD70210ILD-TR von Microsemi enthält einen Enhanced Classification Block, der die Klassifizierung der neuen Klassen und PD-Typen erleichtert, die mit High-Power-PoE eingeführt wurden. Der Chip kann über seine SUPP_S1- und SUPP_S2-Pins auch feststellen, welche der vier verdrillten Paare des Kabels tatsächlich Strom erhalten. (Bildquelle: Microsemi)

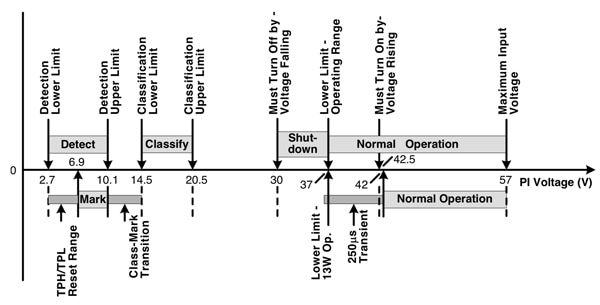

Ein PSE mit Autoclass-Unterstützung überprüft zunächst, ob das PD die Funktion unterstützt, indem es prüft, ob der Strom der Klasse nach einer kurzen Verzögerung auf den Stromwert von Klasse 0 abfällt. Wenn die Unterstützung erkannt wird, kann das PSE sofort nach dem Einschalten mit der Autoclass-Messung fortfahren, wobei das PD in den folgenden 1,35 bis 3,65 Sekunden seine höchste Leistung abrufen muss. Nach dem Start muss das PD eine MPS präsentieren, um gegenüber dem PSE zu versichern, dass es weiterhin verbunden ist. Der Verlust der MPS bewirkt, dass das PSE den Strom abschaltet (Abbildung 2).

Abbildung 2: Der High-Power-PoE-Einschaltprozess ist komplexer als bei den früheren Versionen, da neue PSE- und PD-Klassen und -Typen eingeführt wurden. Hier sind die drei Hauptphasen des Prozesses (Erkennung, Klassifizierung und Betrieb) und die Eingangsspannungen, bei denen diese auftreten, dargestellt. (Bildquelle: Texas Instruments)

Neue Controller erfüllen die High-Power-PoE-Spezifikation

Seit der PoE-Ratifizierung standen Entwicklern immer schnell zahlreiche integrierte PSE-Controller und PD-Schnittstellen zur Verfügung, mit denen sie ihre Designs umsetzen konnten. Dieser Trend setzt sich auch bei IEEE 802.3bt fort. Dank Herstellern, die Produkte entwickelten, welche schon mit der Entwurfsfassung der Spezifikation kompatibel waren, gibt es bereits jetzt mehrere PSE-Controller- und PD-Schnittstellen auf dem Markt, zusätzlich zu dem oben beschriebenen Microsemi-Produkt.

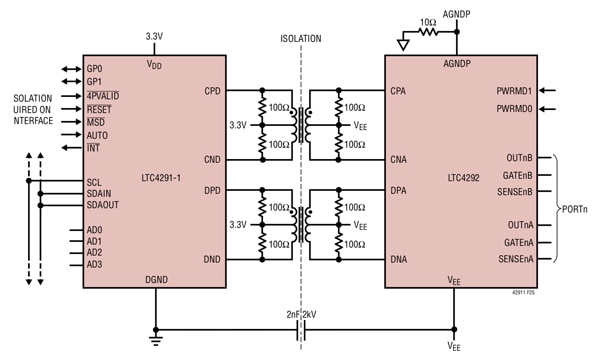

Zum Beispiel bietet Linear Technology den Chipsatz LTC4291-1/LTC4292 an. Die Komponenten sind so konzipiert ist, dass sie zusammenwirken und PSE-Controller des Typs 3 oder 4 bilden. Zu seinen Energieverwaltungsfunktionen gehören die 14-Bit-Stromüberwachung pro Port, eine programmierbare Strombegrenzung und eine flexible, schnelle Abschaltung vorgewählter Ports. Die PD-Erkennung nutzt einen proprietären Mehrpunkt-Detektionsmechanismus, der eine falsche PD-Identifizierung verhindert. Autoclass wird unterstützt, und der Chipsatz kann per Pin oder I2C programmiert werden, um bis zu 71,3 Watt am PD auszuhandeln.

Besonders bemerkenswert beim LTC4291-1/LTC4292-Chipsatz ist sein hoher Integrationsgrad: Er enthält fast alle zur Implementierung eines IEEE 802.3bt-kompatiblen PSE-Designs erforderlichen Schaltungen; nur einige wenige zusätzliche Peripheriekomponenten sind erforderlich. Zur Vereinfachung der PSE-Isolation ist der Baustein in zwei Chips aufgeteilt (Prozessor plus Stromversorgung), wobei sich der LTC4291-1 auf der nicht isolierten Seite befindet. Dort kann er den Strom von der Logikversorgung des Netzes erhalten und sich direkt mit dem I2C/SMBus-Bus verbinden. Der Chipsatz nutzt ein proprietäres Isolationsschema für die Interchip-Kommunikation; es ersetzt Optoisolatoren und isolierte Netzteile durch preisgünstige Transformatoren. Bei den Transformatoren handelt es sich um 10BASE-T- oder 10/100BASE-T-Einheiten mit 1:1-Wicklungsverhältnis und stromkompensierten Netzdrosseln (Abbildung 3).

Abbildung 3: Der 4-Port-IEEE 802.3bt-PoE-PSE-Controller LTC4291-1/LTC4292 von Linear Technology nutzt ein proprietäres Isolationssystem, welches das Design vereinfacht, indem es Optokoppler und isolierte Netzteile durch preisgünstige Transformatoren ersetzt. (Bildquelle: Linear Technology)

Um die Vorteile von High-Power-PoE vollumfänglich nutzen zu können, benötigt ein PD eine Typ-3- oder Typ-4-Schnittstelle, andernfalls liefert das PSE nur die maximale Leistung, die durch IEEE 802.3af vorgegeben ist, also 15,4 Watt (12,95 Watt am PD). Eine Option für diese Schnittstelle ist die TPS2372-4RGWT von TI. Sie enthält alle Funktionen, die zur Implementierung einer IEEE 802.3bt-PD-Schnittstelle von Typ 1 bis Typ 4 benötigt werden.

Dank eines geringen internen Schaltwiderstands können TP2372-3 und TPS2372-4 High-Power-PoE-Anwendungen bis zu 60 Watt bzw. 90 Watt unterstützen, und ihre automatische MPS-Funktion ermöglicht Anwendungen, bei denen Standby-Modi mit sehr geringer Leistungsaufnahme gefordert sind. Beachten Sie, dass die IEEE 802.3bt-MPS-Anforderung für das PD auf das PSE-Ende des Kabels anwendbar ist. Das bedeutet, dass je nach Kabellänge und anderen Parametern, einschließlich der Bulk-Kapazität, zur Verifizierung eine längere MPS-Dauer nötig sein kann. Zu diesem Zweck bietet die TPS2372 drei verschiedene Optionen für die MPS-Impulsdauer und den Betriebszyklus, deren Auswahl über den MPS_DUTY-Eingangspin erfolgt.

Die TPS2372 implementiert Einschaltstromhöhen, die mit allen PSE-Typen kompatibel sind. Der Chip implementiert auch eine Verzögerungsfunktion, die es dem PSE ermöglicht, seine Einschaltstromphase abzuschließen, bevor der PG-Ausgang (Power Good) freigegeben wird. Damit ist gewährleistet, dass die Einschaltanforderungen von IEEE 802.3bt erfüllt sind. Der Autoclass-Aktivierungseingang des Chips bietet Zugriff auf alle Modi zur erweiterten Systemleistungsoptimierung, die im IEEE 802.3bt-Standard spezifiziert sind.

Erste Schritte mit High-Power-PoE

Bei Verwendung eines hochintegrierten Chipsatzes wie dem LTC4291-1/LTC4292 wurde ein Großteil der anspruchsvollen Designarbeit bereits durch den Chip-Hersteller geleistet. Aber es gilt trotzdem, einige Richtlinien bei der Auswahl externer Komponenten und des Platinen-Layouts zu berücksichtigen. Ein Großteil dieser Richtlinien gelten allgemein für die Entwicklung von PoE-Systemen, aber einige auch für die Auswahl geeigneter Komponenten für die höheren Spannungs- und Stromwerte, die mit High-Power-PoE eingeführt wurden.

Zum Beispiel sind für die in Abbildung 3 dargestellten VDD- und VEE-Leitungen ein digitales Netzteil und ein PoE-Netzstromteil erforderlich. VDD erfordert 3,3 V und VEE erfordert eine negative Spannung zwischen -51 und -57 Volt für Typ-3-PSEs und -53 bis -57 Volt für Typ-4-PSEs. Eine keramische Entkopplungskappe mit mindestens 0,1 μF sollte zwischen VDD und DGND platziert werden, und zwar so nahe wie möglich zu jedem LTC4291-1. Zur Aufrechterhaltung der erforderlichen Isolation dürfen LTC4292 AGNDP und LTC4291-1 DGND nicht verbunden sein.

VEE ist die netzisolierte PoE-Versorgung, die den Strom für die PDs liefert. Da sie eine relativ große Energiemenge liefert und erheblichen Stromtransienten ausgesetzt ist, erfordert ihr Design mehr Sorgfalt als bei einer einfachen Logikversorgung. Um eine optimale Systemeffizienz zu erzielen, sollte VEE nahe zur maximalen Amplitude (57 Volt) eingestellt werden, um gerade noch genug Spielraum zu lassen, um Über- oder Unterschießen der Transienten, Temperaturdrift und Leitungsregelung zu berücksichtigen. Ein elektrolytischer Bulk-Kondensator von mindestens 47 μF ist zwischen AGNDP und VEE erforderlich, um störende Resets im Fall von elektrischen Transienten zu minimieren.

Die Auswahl eines externen MOSFET ist eine weitere wichtige Entscheidung des Entwicklers. Dieser MOSFET bildet den Stromumschaltbaustein, der die PSE-Ausgabe steuert. Die Auswahl der Komponente hat erheblichen Einfluss auf die Zuverlässigkeit des Systems und setzt voraus, dass der Entwickler den sicheren Betriebsbereich (SOA) des MOSFET vor dem Hintergrund der verschiedenen PSE-Stromgrenzenbedingungen analysiert und testet. Linear Technology empfiehlt den PSMN075-100MSEX von Nexperia für PSEs, die zur Abgabe von bis zu 51 Watt an das PD konfiguriert werden, oder den PSMN040-100MSEX für 71,3 Watt am PD, weil diese MOSFETs ihre Zuverlässigkeit in PoE-Anwendungen bereits unter Beweis gestellt haben.

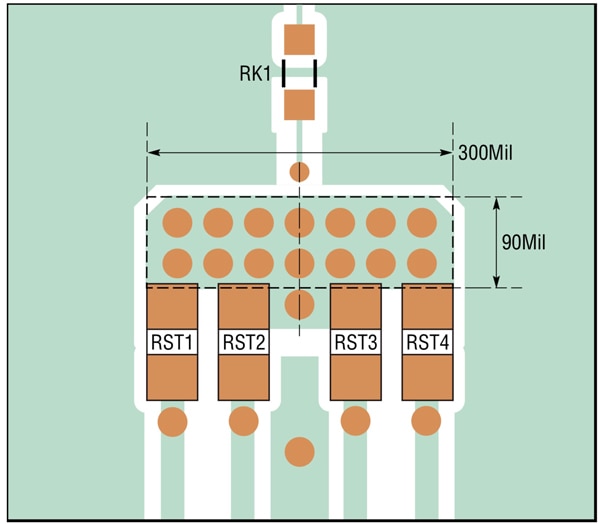

Der LTC4291-1/LTC4292-Chipsatz ist für einen Strommesswiderstand von 0,15 Ω pro Kanal ausgelegt. Der Entwickler muss zwei parallele 0,3Ω-Widerstände hinzufügen, die wie in Abbildung 4 gezeigt positioniert werden. Die Messwiderstände müssen eine Toleranz von ±1 Prozent oder besser aufweisen und einen Temperaturkoeffizienten von nicht mehr als ±200 ppm/°C, um die High-Power-PoE-Spezifikation zu erfüllen.

Abbildung 4: Dargestellt ist das Anschlussdiagramm des Widerstandsblocks für die erforderliche Messung der Stromober- und -untergrenze beim LTC4292. Auswahl und Platzierung des Messwiderstands (RSTx) sind entscheidend, um die High-Power-PoE-Spezifikation zu erfüllen. (Bildquelle: Linear Technology)

Für jeden Port ist ein 0,22μF-Kondensator über OUTnA und OUTnB bis AGNDP erforderlich (siehe erneut Abbildung 3), um den LTC4292 stabil zu halten, wenn er sich beim Einschalten oder bei Überlast im Strombegrenzungsmodus befindet. X7R-Keramikkondensatoren, die für mindestens 100 Volt ausgelegt sind, werden empfohlen und müssen nahe zum LTC4292 positioniert werden.

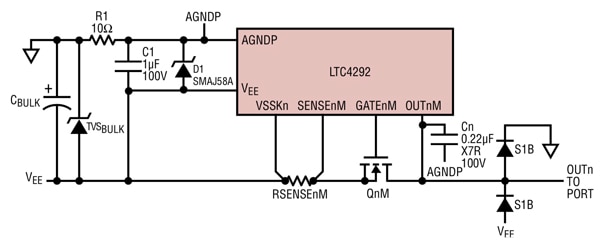

Ethernet-Ports können erheblichen elektrischen Transienten ausgesetzt sein. Umfassender Überspannungsschutz für PoE-Systeme ist ein weiteres Thema, das einen eigenen Artikel erfordert. Doch eine Mindestanforderung ist ein Bulk-Spannungsbegrenzer wie eine TVS-Diode (Transient-Voltage Suppression) (TVSBULK) und ein Bulk-Kondensator (CBULK) zur Eindämmung von Spitzenströmen und -spannungen auf sichere Werte für jeden Port (Abbildung 5). Außerdem ist zwischen dem AGND-Pin der Versorgung und dem AGNDP-Pin des LTC4292 ein 10-Ω-Vorwiderstand (R1) erforderlich. Zwischen dem AGNDP-Pin des LTC4292 und dem VEE-Pin sollte sich eine 58-Volt-TVS-Diode (D1) befinden, und ein 1-μF-, 100-Volt-Bypass-Kondensator (C1) sollte in der Nähe der LTC4292-Pins platziert werden. Schließlich erfordert jeder Port ein Paar von S1B-Klemmdioden: eine zwischen OUTnM und AGND der Versorgung und eine zwischen OUTnM und VEE der Versorgung. Diese leiten alle elektrischen Transienten in die Versorgungsschienen ab, wo sie von den Überspannungsableitern absorbiert werden.

Abbildung 5: PSE-Controller müssen vor elektrischen Transienten geschützt werden. Hier dargestellt ist der LTC4292 von Linear Technology mit den erforderlichen Spannungs-/Strombegrenzern, damit Transienten von den empfindlichen Chips weggeleitet werden können. (Bildquelle: Linear Technology)

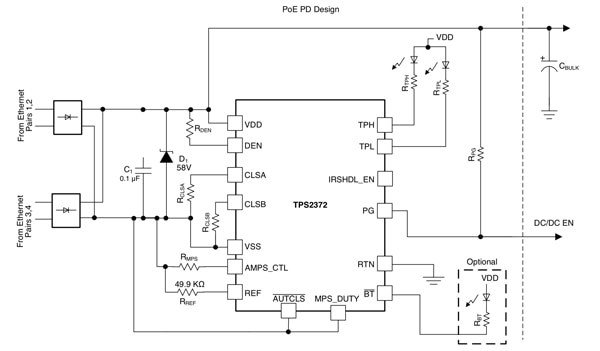

Auch bei der PD-Schnittstelle erleichtert der hohe Integrationsgrad von Chips wie dem TPS2327 von TI das Leben des Entwicklers ein wenig, doch auch hier sind einige externe Komponenten erforderlich (Abbildung 6).

Zum Beispiel sind Dioden am Kabeleingang in die PD-Schnittstelle erforderlich. Für den TPS2327 empfiehlt TI für High-Power-PoE-Anwendungen anstatt herkömmlicher Dioden für 3 A bis 5 A und 100 Volt ausgelegte diskrete oder Brücken-Schottky-Dioden, da die Verlustleistung bei diesen Dioden um 30 Prozent niedriger ist. Eine Sache, die der Entwickler beachten muss: Schottky-Dioden haben oft einen höheren Rückwärtsleckstrom als normale Dioden mit pn-Übergang, wodurch es schwierig ist, die von der Spezifikation festgelegte maximale Rückspeisespannung von 2,8 Volt einzuhalten. Um das zu kompensieren, sollten für diese Implementierung Dioden mit konservativen Betriebstemperaturgrenzen und Bausteine mit geringem Leckstrom verwendet werden. Schottky-Dioden sind auch anfälliger für elektrische Transienten als konventionelle Dioden, weshalb ein Spannungs-/Stromschutz in Form von Ferritperlen und Kondensatoren empfohlen wird.

Die IEEE 802.3bt-Spezifikation sieht einen Eingangs-Bypass-Kondensator von 0,05 bis 0,12 µF (in der Regel ein 0,1-µF-Keramikkondensator, 100 V, ±10 %) zwischen VDD und VSS vor. Die Spezifikation erfordert auch einen Detektionswiderstand RDEN, Klassifizierungswiderstände RCLSA und RCLSB sowie einen MPS-Widerstand RMPS. Für RDEN wird ein Widerstand von 24,9 kΩ ±1 % empfohlen. Die Klassifizierungswiderstände sind zwischen CLSA und CLSB zu VSS positioniert, um den Klassifizierungsstrom entsprechend dem IEEE802.3bt-Standard zu programmieren. Der Wert dieser Widerstände und die zugewiesene Klassenleistung richten sich nach der maximalen durchschnittlichen Leistungsaufnahme des PD während des Betriebs. RMPS legt den MPS-Betriebszyklus fest; zum Beispiel legt ein 1,3-kΩ-Widerstand den Betriebszyklus auf 26,4 % fest. Wird MPS_DUTY zu RSS kurzgeschlossen, bedeutet das eine Festlegung des Betriebszyklus auf 12,5 %.

Die PD-Schnittstelle von High-Power-PoE-erfordert auch die TVS-Diode und den Bulk-Kondensator (D1, CBULK) zur Spannungsbegrenzung über die Stromleitungen, um elektrische Transienten an diesem Ende des Kabels zu absorbieren.

Abbildung 6: Das Anwendungsdiagramm der High-Power-PoE-PD-Schnittstelle TPS2372 von TI zeigt, welche peripheren Komponenten erforderlich sind, um das Design umzusetzen – in erster Linie Eingangsdioden, Begrenzungskomponenten sowie Detektions-, Klassifizierungs- und MPS-Widerstände. (Bildquelle: Texas Instruments)

Es gibt zahlreiche Design-Richtlinien, die gewährleisten sollen, dass Platinen-Layout, Platzierung der Komponenten und Leitungsführung die Anforderungen der IEEE 802.3bt-Spezifikation in Bezug auf parametrische Messgenauigkeit, Robustheit und Wärmeableitung erfüllen. Sowohl Linear Technology als auch TI bieten Referenzdesigns für Ihre PSE/PD-Schnittstellen an, die genau der Spezifikation entsprechen und dem Entwickler eine praktische Hilfestellung bieten.

Fazit

High-Power-PoE erweitert PoE-Anwendungen und steigert ihre Effizienz. Der neue Standard hat jedoch auch die Komplexität der Implementierung erhöht: durch Einführung weiterer Typen und Klassen der PSE-Controller und PD-Schnittstellen, aber auch durch zusätzliche Betriebs- und Sicherheitsfunktionen.

Für den Entwickler gibt es jedoch Hilfe in Form von integrierten PSE-Controller- und PD-Schnittstellen-Lösungen, die diese Funktionen bereits standardmäßig enthalten. Diese Lösungen vereinfachen und beschleunigen den Entwicklungsprozess erheblich, indem sie die Anzahl der peripheren Komponenten verringern, die zur Realisierung des Systems erforderlich sind.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.