Einsatz von FPGAs in ressourcenbeschränkten Anwendungen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2025-05-07

Der Bedarf an konfigurierbarer Logik wächst in ressourcenbeschränkten eingebetteten Systemen. Anwendungen wie Künstliche Intelligenz, maschinelles Sehen und industrielle Automatisierung erfordern eine flexible, anwendungsspezifische Logik, die den wachsenden Leistungsanforderungen gerecht wird und gleichzeitig strenge Energie-, Größen- und Kostengrenzen einhält. Moderne feldprogrammierbare Gate-Arrays (FPGAs) können diese konkurrierenden Anforderungen erfüllen.

Dieser Artikel gibt einen Überblick über die wichtigsten Designkriterien, die bei der Auswahl eines FPGAs für ressourcenbeschränkte Anwendungen zu berücksichtigen sind. Anschließend wird anhand von Beispielen aus Alteras Portfolio an energie- und kostenoptimierten FPGAs beschrieben, wie die verschiedenen Produktlinien auf bestimmte Szenarien abgestimmt sind. Abschließend werden Entwicklungskits und Evaluierungsboards vorgestellt, die zur Erstellung von Prototypen und zur Validierung von Designkonzepten verwendet werden können.

Überlegungen zur Auswahl eines FPGAs

Die Auswahl eines FPGAs für ein ressourcenbeschränktes System erfordert die Berücksichtigung mehrerer Designanforderungen und deren Abstimmung auf die richtige Lösung. Es gibt mehrere wichtige FPGA-Merkmale zu berücksichtigen:

Anzahl der Logikelemente (LE): Als grundlegender Baustein eines FPGAs bestimmt die Anzahl der LEs, wie viel kundenspezifische Logik implementiert werden kann. Je höher die Anzahl desto komplexer können die Entwürfe werden: Der Kompromiss ist eine Erhöhung der Leistung, der Kosten und der Gehäusegröße.

I/O und Speicher: FPGAs werden häufig zur Verbindung verschiedener Komponenten innerhalb eines Systems verwendet, weshalb die Anzahl der I/O-Pins eine wichtige Rolle spielt. Um die I/O-Performance zu steigern, enthalten viele FPGAs gehärtete, feste Logikblöcke für Schnittstellen wie PCI Express (PCIe), Hochgeschwindigkeitsspeicher und Multi-Gigabit-Transceiver.

Darüber hinaus sind in einigen FPGAs Funktionen wie Analog/Digital-Wandler (ADCs) und Flash-Speicher integriert. Diese Verbesserungen können den Bedarf an Zusatzchips verringern, wodurch Platz auf der Leiterplatte gespart und die Energieeffizienz verbessert wird.

Integration eines Prozessors: Anstelle eines externen Prozessors kann eine „Soft“-Mikroprozessoreinheit (MPU) innerhalb des FPGAs implementiert werden. Dieser Ansatz kann den Platzbedarf eines Systems verringern, eignet sich aber am besten für Anwendungen mit weniger anspruchsvollen MPU-Arbeitslasten.

Für Anwendungen, die schnellere, effizientere MPUs benötigen, können Designer ein FPGA mit einem Hard-Processor-System (HPS) in Betracht ziehen, das eine MPU als festen Logikblock innerhalb des FPGAs implementiert.

Hardware-Beschleuniger: FPGAs enthalten in der Regel spezielle digitale Signalverarbeitungsblöcke (DSP), die rechenintensive Aufgaben wie die Motorsteuerung effizient erledigen. Höherwertige Geräte können spezielle Tensor-Blöcke für KI-Workloads enthalten. Die Fähigkeiten dieser Beschleunigerblöcke variieren erheblich zwischen den FPGA-Familien und können die Gesamtperformance des Systems erheblich beeinflussen.

Optimierung von Gehäuse und Stromverbrauch: Einige FPGAs sind speziell darauf ausgelegt, ihren physischen und elektrischen Footprint zu minimieren. Sie können zum Beispiel einen stromsparenden Ruhemodus anbieten.

Tools: Die Erstellung einer benutzerdefinierten Logik kann eine große Herausforderung sein, insbesondere für Entwickler, die neu in diesem Prozess sind. Tools wie die Design-Software Quartus Prime von Altera wurden entwickelt, um diesen Prozess zu optimieren.

Quartus Prime wurde entwickelt, um den Zugang zum FPGA-Design zu erleichtern. Es bietet eine entwicklerfreundliche Oberfläche, einen umfangreichen Katalog vorgefertigter Logikblöcke und die Möglichkeit, diese Logikblöcke automatisch miteinander zu verbinden. Das Tool lässt sich in gängige KI- und ML-Workflows integrieren und ermöglicht es Entwicklern, gängige Betriebssysteme wie Linux und Zephyr auf einem FPGA einzusetzen.

Fähigkeiten wie diese können das FPGA-Design erheblich beschleunigen, so dass Tool-Funktionen bei der Auswahl eines Bausteins eine entscheidende Rolle spielen.

Hochleistungscomputer für fortschrittliche eingebettete Workloads

Um zu veranschaulichen, wie die Designanforderungen die FPGA-Auswahl beeinflussen, ist es hilfreich, mit High-End-Anwendungen zu beginnen, die eine außergewöhnliche Rechendichte, Bandbreite und Integration erfordern. Beispiele hierfür sind moderne Edge-KI-Anwendungen und leistungsstarke Industrie-Gateways.

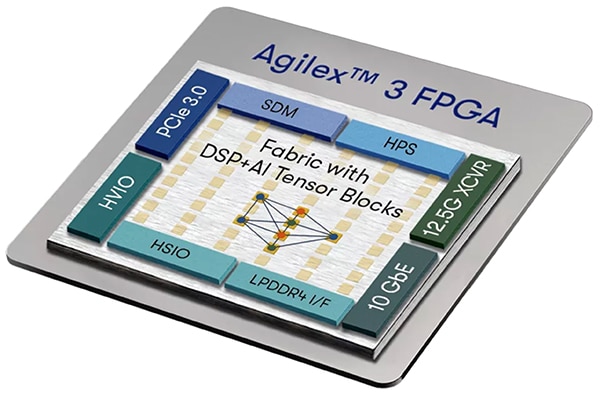

Die FPGAs der Serie Agilex 3 (Abbildung 1) wurden entwickelt, um diese Anwendungsanforderungen zu erfüllen, und bieten bis zu 135K LEs. Die Chips sind sowohl als reine FPGA- als auch als SoC-Varianten (System-on-Chip) erhältlich. Die SoC-Bausteine enthalten einen Dual-Core-Arm®-Cortex®-A55 für 800 Megahertz (MHz), der es dem FPGA ermöglicht, komplexe Software-Stacks wie Mensch-Maschine-Schnittstellen (HMIs) oder Netzwerk-Stacks zu übernehmen.

Die programmierbare Struktur verfügt über AI-Tensor-Blöcke, die bis zu 2,8 INT8 Tera-Operationen pro Sekunde (TOPS) liefern können. Diese Blöcke unterstützen verschiedene Berechnungsformate, darunter FP16, FP19, FP32 und BFLOAT16, und sind für die effiziente Ausführung von KI-Workloads optimiert. Außerdem sind DSP-Blöcke mit variabler Genauigkeit enthalten, die eine Leistung von bis zu 180 Giga-Gleitkomma-Operationen pro Sekunde (GFLOPS) für die Allzweck-Signalverarbeitung bieten.

Abbildung 1: Der Agilex 3 zeichnet sich durch seine leistungsstarken DSP- und AI-Tensor-Blöcke aus. (Bildquelle: Altera)

Abbildung 1: Der Agilex 3 zeichnet sich durch seine leistungsstarken DSP- und AI-Tensor-Blöcke aus. (Bildquelle: Altera)

Die Highspeed-Vernetzung ist eine weitere Stärke der Agilex-3-Architektur. Die Transceiver unterstützen Datenraten von bis zu 12,5 Gigabit pro Sekunde (Gbit/s) und verfügen über gehärtete I/O-Blöcke für PCIe 3.0, 10 Gigabit Ethernet (GbE) und LPDDR4-Speicherschnittstellen. Durch die Unterstützung der präzisen IEEE1588-Zeitsynchronisation wird die Eignung für industrielle Echtzeitnetzwerke weiter erhöht.

Der Baustein A3CZ135BB18AE7S veranschaulicht die Möglichkeiten dieser Familie. Er umfasst 135K LEs, 184 DSP-Blöcke und liefert 2,54 TOPS.

Erweiterte Integration für komplexe Systeme

Für Anwendungen wie industrielle Automatisierung und Bildverarbeitungssysteme mittlerer Größe ist die reine Rechenleistung oft weniger wichtig als die Fähigkeit, komplexe Konfigurationen mit einer großen Menge an kundenspezifischer Logik und I/O zu unterstützen. Die FPGAs Cyclone V sind für diese Szenarien gut geeignet, da sie bis zu 300K LEs und umfangreiche Highspeed-Schnittstellen bieten. Wie der Agilex 3 sind auch diese Chips in reinen FPGA- und SoC-Varianten erhältlich. In diesem Fall enthalten die SoC-Komponenten einen Dual-Core-Arm-Cortex-A9.

Die programmierbare Struktur dieser Chips umfasst DSP-Blöcke mit variabler Genauigkeit, die eine dreifache 9×9- und zweifache 18×18-Festkommamultiplikation sowie eine 27×27-Festkomma- oder -Gleitkommamultiplikation unterstützen. Diese Blöcke können für fortgeschrittene Signalverarbeitung und KI verwendet werden.

Eine breite Mischung von I/O unterstützt mehrere Spannungsebenen und Schnittstellentypen. Gehärtete Logikblöcke ermöglichen fortschrittliche Highspeed-Vernetzung, einschließlich PCIe 2.0, DDR3-Controller und Transceiver, die mit bis zu 6,144 Gbit/s arbeiten.

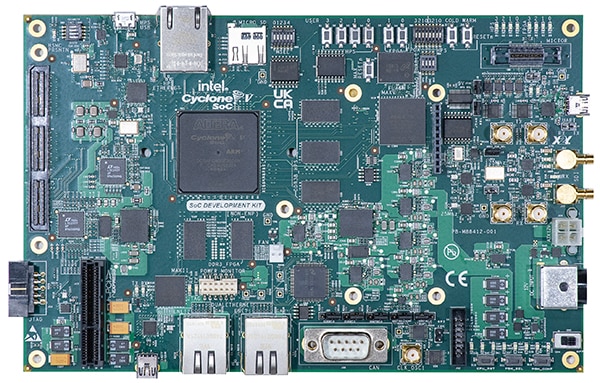

Entwickler können die SoC-Familie Cyclone V mit dem Entwicklungskit DK-DEV-5CSXC6N-B evaluieren (Abbildung 2). Dieses Kit ist für das Rapid Prototyping von komplexen Systemen mit hohem Durchsatz konzipiert.

Abbildung 2: Das Cyclone-V-Entwicklungskit DK-DEV-5CSXC6N-B unterstützt das Hochleistungs-Prototyping. (Bildquelle: Altera)

Abbildung 2: Das Cyclone-V-Entwicklungskit DK-DEV-5CSXC6N-B unterstützt das Hochleistungs-Prototyping. (Bildquelle: Altera)

Das Kit enthält mehrere bemerkenswerte Merkmale:

- Zwei Ethernet-Anschlüsse, ein PCIe-x4-Anschluss und eine Highspeed-Mezzanine-Karte (HSMC) mit 16 LVDS-Kanälen in jeder Richtung

- USB 2.0 OTG, CAN, UART und eine zweizeilige Text-LCD-Schnittstelle

- Je 1 Gigabyte DDR3-SDRAM für die FPGA- und die HPS-Seite, 128 Megabyte Quad-SPI-Flash und eine 4 GByte microSD-Karte

Das Board enthält den Baustein 5CSXFC5D6F31C8N, der einen Dual-Core-Arm-Cortex-A9-Prozessor für 600 MHz, 85K LEs, 87 DSP-Blöcke und 288 I/O-Pins in einem 31 mm × 31 mm großen 896-FBGA-Gehäuse umfasst.

Leistungseffiziente konfigurierbare Logik in einem kompakten Gehäuse

Viele Anwendungen sind durch enge Platz- und Stromverbrauchsvorgaben gekennzeichnet. Beispiele hierfür sind Sensorschnittstellen, Stromversorgungssequenzen und die Steuerung von Peripheriegeräten. FPGAs wie die Familie MAX 10 bieten für diese Fälle eine effektive Lösung. MAX-10-Bausteine sind in Konfigurationen von 2K bis 50K LEs und in Gehäusen von nur 3 mm × 3 mm erhältlich.

Zu den wichtigsten Merkmalen gehören bis zu zwei integrierte 12-Bit-ADCs, eine DDR3-Speicherschnittstelle und Multiplikatorblöcke, die 18 × 18 und zwei 9 × 9 Festkomma-Modi unterstützen. On-Chip-Flash mit Unterstützung für Dual-Image-Speicher ermöglicht es dem FPGA, sich selbst zu konfigurieren, ohne einen externen Speicherbaustein.

Stromsparfunktionen sind eines der herausragenden Merkmale der Familie MAX 10. Ein integrierter Ruhemodus kann den dynamischen Stromverbrauch um bis zu 95% reduzieren. Dank des On-Chip-Flashs können die Geräte auch vollständig heruntergefahren werden und dann in weniger als 10 Millisekunden (ms) wieder in Betrieb genommen werden.

Eine Einzelversorgungsoption vereinfacht die Stromversorgung weiter. Dadurch eignen sich MAX-10-Komponenten besonders gut für Überwachungsaufgaben, bei denen Stromversorgungsdomänen möglicherweise vor dem Rest des Systems online gehen müssen.

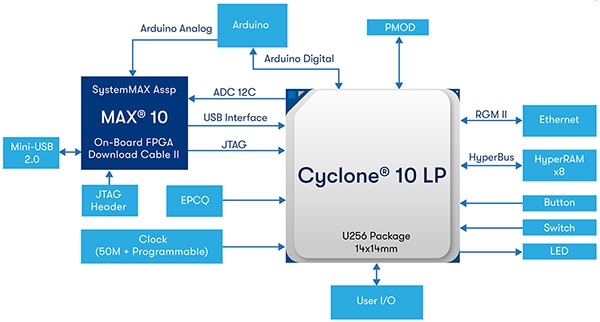

Entwickler, die sich für den MAX 10 interessieren, können die Familie mit dem MAX-10-FPGA-Evaluierungsboard EK-10M08E144 evaluieren (Abbildung 3). Dieses Board bietet Zugang zu externen Signalen über Arduino-UNO-R3-Anschlüsse und Testpunkte, wobei das Layout so gestaltet ist, dass es die Messung der ADC-Leistung und des allgemeinen Leistungsverhaltens unterstützt.

Abbildung 3: Das MAX-10-FPGA-Evaluierungsboard EK-10M08E144 bietet einfachen Zugang zu den wichtigsten I/Os. (Bildquelle: Altera)

Abbildung 3: Das MAX-10-FPGA-Evaluierungsboard EK-10M08E144 bietet einfachen Zugang zu den wichtigsten I/Os. (Bildquelle: Altera)

Das Board enthält den Baustein 10M08SAE144C8G, der 8K LEs und einen einzelnen ADC in einem 144-Pin-LQFP-Gehäuse enthält. Zusätzlich zu den eingebauten Hardwareressourcen unterstützt dieses FPGA den RISC-V-basierten Nios-V-Softprozessor, der es Entwicklern ermöglicht, leichtgewichtige Steuerungsfunktionen zu implementieren, ohne eine externe Mikrocontrollereinheit (MCU) zu benötigen.

Ausgewogene Leistung für Anwendungen im mittleren Leistungsbereich

Einige Anwendungen erfordern mehr Logik- und I/O-Kapazität als FPGAs der Einstiegsklasse bieten können. Beispiele hierfür sind Sensorfusion, Bewegungssteuerung und Chip-to-Chip-Bridging. Die FPGAs Cyclone 10 LP erfüllen diese Anforderungen, indem sie bis zu 120K LEs und 525 I/O-Pins in Bausteinen bieten, die für ausgewogene Leistung und Bandbreite in kostensensitiven Anwendungen optimiert sind.

Wie der MAX 10 umfasst die Familie DSP-Blöcke, die sich für Aufgaben wie Filterung, Regelschleifen und grundlegende KI-Inferenzfunktionen eignen. Im Gegensatz zum MAX 10 sind die Bausteine Cyclone 10 LP mit echten LVDS-Transceivern und On-Chip-Terminierung (OCT) ausgestattet, um digitale Highspeed-Schnittstellen zu unterstützen.

Entwickler, die sich für den Cyclone 10 LP interessieren, können die Familie mit dem Cyclone-10-Evaluierungskit EK-10CL025U256 evaluieren (Abbildung 4). Dieses Board bietet Arduino-UNO-R3- und Digilent-Pmod-Anschlüsse für eine einfache Erweiterung. Weitere Merkmale sind GbE, USB 2.0, 128 Megabit (Mbits) SDRAM und 64 Mbit Flash-Speicher.

Abbildung 4: Das Cyclone-10-Evaluierungskit EK-10CL025U256 unterstützt die einfache Erweiterung der Peripherie. (Bildquelle: Altera)

Abbildung 4: Das Cyclone-10-Evaluierungskit EK-10CL025U256 unterstützt die einfache Erweiterung der Peripherie. (Bildquelle: Altera)

Das Board enthält den Baustein 10CL025YU256C8G, der 25K LEs, 66 DSP-Blöcke und 150 I/O-Pins in einem 14 mm × 14 mm großen Gehäuse umfasst. Wie der MAX 10 unterstützt die Familie Cyclone 10 LP den Softprozessor Nios V.

Fazit

Bei der Implementierung von kundenspezifischer Logik in eingebettete Systeme haben Entwickler jetzt mehr Flexibilität denn je. Leistungsstarke Anwendungen können von FPGAs mit integrierten KI-Beschleunigern profitieren. Stromsparende Designs können die Vorteile von Komponenten mit Ruhemodus nutzen. I/O-intensive Systeme können Chips mit hoher Pinzahl und Highspeed-Schnittstellen nutzen. Wichtig ist, dass all diese Fähigkeiten innerhalb der engen Grenzen von ressourcenbeschränkten eingebetteten Systemen mit einfach zu verwendenden Kits realisiert werden können.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.