Welcher ADC passt zur jeweiligen Anwendung?

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2018-04-03

Wir leben in einer analogen Welt, die von digitalen Computern gesteuert wird. Daher müssen Entwickler von Geräten für das Internet der Dinge analoge Werte effizient in digitalisierte Abbildungen dieser Werte umwandeln. Die Lösung könnte schlicht darin bestehen, einen Analog/Digital-Wandler (ADC) davor zu setzen. Aber nicht alle ADCs sind gleich. Entwickler müssen also die verschiedenen Topologien kennen und wissen, welche zu welcher Anwendung passt.

ADCs wurden zum Beispiel in Bezug auf Kenngrößen wie Abtastrate, Stromverbrauch und Genauigkeit optimiert. In diesem Artikel werden die Designanforderungen im Kontext einiger gängiger ADC-Architekturen erörtert. Anschließend stellt der Autor Anwendungen vor, bei denen diese Architekturen zum Einsatz kommen, und zeigt, wie sie implementiert werden.

Die Aufgabe eines ADC

Ein ADC ist ein häufig eingesetzter elektronischer Schaltkreis oder ein modulares Gerät, das ein analoges Signal – in der Regel eine Spannung – in eine Reihe diskreter abgetasteter Abbildungen bzw. Zahlen umwandelt. ADCs führen drei unterschiedliche Operationen durch: Abtastung, Quantisierung und Codierung. Sie stehen im Zentrum vieler digitaler Instrumente wie Voltmetern, Oszilloskopen und Spektrumanalysatoren. Präsent sind sie auch im Frontend digitaler Schaltkreise zur Verarbeitung analoger Signale von Geräten wie Mikrofonen, Beschleunigungsmessern, Fotosensoren und anderen Transducern, deren Ausgang in eine digitale Form gebracht werden muss, damit ein Mikroprozessor mit den Daten arbeiten kann.

Viele verschiedene ADC-Architekturen oder -Topologien wurden entwickelt, um analoge Signale abzutasten und zu digitalisieren. Jede einzelne ADC-Form hat ihre eigenen Merkmale, Vorteile und Schwächen. Welches der passende ADC-Typ für eine bestimmte Anwendung ist, wird in der Regel durch die Anforderungen an Geschwindigkeit, Auflösung, Genauigkeit, Stromverbrauch und Größe definiert.

Wichtige Kenngrößen von ADCs

Die erste Operation eines ADC ist das Abtasten des Analogsignals. Dazu wird eine Sample-and-Hold- oder eine Track-and-Hold-Schaltung eingesetzt. Das Abtast- oder Nyquist-Theorem besagt, dass die Abtastrate mehr als das Doppelte der Bandbreite des Signals betragen muss, damit das analoge Signal aus den digitalisierten Abtastungen rekonstruiert werden kann. Die erste signifikante Kenngröße eines ADC ist daher die Abtastrate, die die maximale Signalfrequenzkomponente bestimmt, die vom ADC digitalisiert werden kann.

Der ADC muss jede Abtastung quantisieren, wozu die abgetastete Spannung in eine endliche Anzahl diskreter Amplitudenpegel aufgeteilt wird. Diese Kenngröße wird in der Regel als die Anzahl der Auflösungsbits bezeichnet. Wird ein Signal zum Beispiel in 8 Bits aufgeteilt, bedeutet dies, dass es 28 oder 256 diskrete Pegel gibt. Ein 16-Bit-ADC teilt den Spannungsbereich in 65.536 Quantisierungsstufen auf.

Sowohl die Auflösung als auch die Abtastrate wird von der ADC-Hardware bestimmt. Je höher die Auflösung des ADC, desto begrenzter ist in der Regel die maximale Abtastrate.

Die Genauigkeit eines ADC ist von der Auflösung und der Abtastrate abhängig. Die Auflösung beeinflusst die Amplitudengenauigkeit. Andere Faktoren, die die Amplitudengenauigkeit beeinflussen, sind die Linearität des Quantisierungsprozesses und die Auswirkungen des vertikalen Rauschens. Die Abtastrate bestimmt die Zeitgenauigkeit.

Größe, Stromverbrauch und andere Eigenschaften sind von der Schaltungstopologie abhängig. Für Anwendungen, die bezüglich der Größe oder der verfügbaren Energie beschränkt sind, wie IoT-Geräte oder batteriebetriebene, tragbare Instrumente, sind diese Eigenschaften von großer Bedeutung. Größe und Stromverbrauch sind stark von der ADC-Topologie abhängig.

Flash-, Direkt- oder Parallel-ADC?

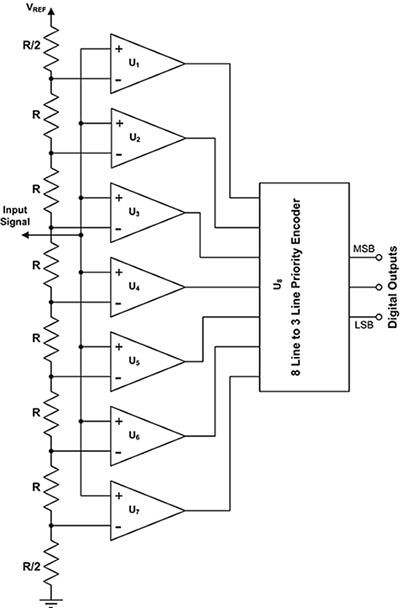

Vom Aufbau her der einfachste Digitalisierer ist der Flash-ADC, der auch als Direkt- oder Parallel-ADC bezeichnet werden kann (Abbildung 1).

Abbildung 1: Ein Flash-ADC nutzt mehrere Komparatoren mit gleichförmig inkrementierten Schwellenspannungen, um eine analoge Spannung in eine digitale Zahl umzuwandeln. Dieses Beispiel zeigt einen 3-Bit ADC mit einer Auflösung von 8 Stufen. (Bildquelle: DigiKey)

Der Eingang eines Flash-ADC kommt in der Regel aus einer Sample-and-Hold- oder einer Track-and-Hold-Schaltung, wobei der analoge Eingang abgetastet und während der Dauer der Umwandlung konstant gehalten wird. Das abgetastete Signal wird auf ein Array analoger Komparatoren angewandt, deren Schwellenspannungen mit einem Abstandswert, der einem niederwertigsten Bit (LSB) entspricht, gleichmäßig über den Eingangsspannungsbereich des ADC verteilt sind. Der Ausgang eines jeden Komparators ändert seinen Status, wenn die Eingangsspannung den für diesen Komparator vom Spannungsteiler festgelegten Schwellenwert übersteigt. Das Beispiel in der Abbildung zeigt einen 3-Bit-ADC, der 7 Komparatoren benötigt, um 8 mögliche Zustände zu erzeugen.

In der Regel benötigt ein N-Bit-Flash-Wandler (2N-1) Komparatoren. Die Komparatoren erzeugen einen sogenannten Thermometercode. Je höher die Eingangsspannung, desto größer die Anzahl der Komparatoren von unten nach oben, die den Status „1“ erreichen. Dieser Code wird auf einen Prioritätscodierer angewandt, der ihn in einen Binärcode umwandelt.

Der Hauptvorteil eines Flash-Wandlers ist die Geschwindigkeit. Die Umwandlungsdauer ist nur so groß wie die Verzögerung des Komparators und des Decoders. Im Handel sind Flash-Wandler mit maximalen Abtastraten von bis zu 5 Gigasamples pro Sekunde (GS/s) erhältlich. Der begrenzende Faktor für Flash-Wandler-Auflösungen ist die erforderliche Anzahl Komparatoren. Für einen 8-Bit-Flash-ADC wären 255 Komparatoren erforderlich.

Diese Zahl erhöht sich um den Faktor zwei für jedes zusätzlich Bit an Auflösung. Somit wächst die Größe des ADC exponentiell mit der Auflösung. Dies führt zu einer weiteren Einschränkung – dem Strombedarf des Flash-Wandlers. Dieser beschränkt den Einsatz dieser Wandler auf netzbetriebene Anwendungen. In der Praxis liegt die Grenze für Flash-Wandler-Auflösungen bei ca. 8 Bit.

Binäre Codierung

Der binäre Ausgang des ADC kann auf verschiedene Weise codiert werden. Ist das umzuwandelnde Signal unipolar, wird es in der Regel als unipolarer reiner Binärcode codiert. Dieser Code stellt einen Nullwert als lauter Nullen (0000…) und den maximalen Eingangswert als lauter Einsen (1111…) dar.

Ist das Signal bipolar, wird es in der Regel entweder in Exzesscode- oder Zweierkomplement-Binärschreibweise dargestellt, wie in Tabelle 1 anhand eines 4-Bit-Beispiels aufgeführt.

|

Tabelle 1: Gebräuchliche binäre Codierung für bipolare digitale Signale. Die Zweierkomplement-Binärschreibweise wird von Mikroprozessoren oder mathematischen Prozessoren am häufigsten verwendet. (Bildquelle: DigiKey)

Die Zweierkomplement-Binärcodierung wird von den meisten mikroprozessor- oder mathematikprozessorbasierten Systemen verwendet, da sie Rechenoperationen ermöglicht.

Pipeline-, Subranging- und zweistufige ADCs

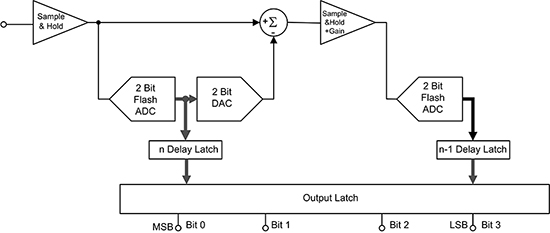

Die Anzahl der Komparatoren in einem Flash-Wandler kann verringert werden, indem die Wandlung in zwei oder mehr Stufen aufgeteilt wird, sodass weniger Bits pro Stufe umgesetzt werden. Ist der Flash-ADC in zwei Abschnitte aufgeteilt, spricht man von einem zweistufigen ADC oder Subranging-ADC. Ist er in mehr als zwei Abschnitte aufgeteilt, wird er als Pipeline-ADC bezeichnet. Ein zweistufiger ADC kann immer noch Hunderte von Megasamples pro Sekunde (MS/s) abtasten (Abbildung 2).

Abbildung 2: Das Funktionsblockdiagramm eines 4-Bit-Subranging-ADC oder zweistufigen ADC zeigt die Aufteilung des 4-Bit-Wandlers in zwei 2-Bit-Wandler, wodurch die Anzahl der Komparatoren verringert wird. (Bildquelle: DigiKey)

Dieser zweistufige Wandler teilt den 4-Bit-Wandler, für den 15 Komparatoren erforderlich wären, in zwei 2-Bit-Abschnitte auf. Für jeden Abschnitt sind drei Komparatoren, insgesamt also sechs Komparatoren erforderlich. Zuerst werden die beiden höchstwertigen Bits (MSB) umgesetzt. Der digitale Ausgang des ersten Abschnitts enthält einen Digital/Analog-Wandler (DAC), um das Signal in ein Analogsignal umzuwandeln und es vom Eingangssignal zu subtrahieren.

Die resultierende Differenz wird verstärkt und dazu verwendet, die beiden LSBs umzusetzen. Die kombinierten Ergebnisse werden in den Ausgangs-Latches erfasst. Der Wandlungsprozess wird zweimal wiederholt, sodass die maximale Abtastrate niedriger ist als die des Flash-Wandlers. Der von Analog Devices angebotene AD9203ARUZRL7 ist ein Beispiel für einen 10-Bit Pipeline-ADC mit 40 MS/s, der eine Analog/Digital-Wandlung mit hoher Geschwindigkeit ermöglicht.

SAR-ADCs (Wandler mit sukzessiver Approximation)

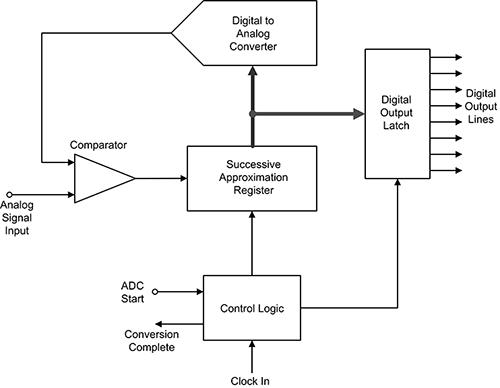

Erfordert die Anwendung eine höhere Auflösung und nicht zwangsläufig die Geschwindigkeit eines Flash- oder Pipeline-ADC, bietet sich ein SAR-Wandler an (Abbildung 3). SAR-ADCs arbeiten mit 12 bis 16 Bit, mit Abtastraten von bis zu 1 bis 2 MS/s.

Abbildung 3: Ein SAR-ADC bietet eine gute Auflösung bei kleinem bis mäßigem Stromverbrauch. (Bildquelle: DigiKey)

Wie Flash-ADCs wird auch SAR-ADCs eine Sample-and-Hold- oder eine Track-and-Hold-Schaltung vorgeschaltet, um den Abtastwert während der Dauer des Wandlungsprozesses konstant zu halten. Das Signal aus der Sample-and-Hold-Schaltung wird auf einen Komparator angewandt. Das Register mit schrittweiser Annäherung (Successive Approximation Register, SAR) beginnt in der Mitte des Bereichs und wandelt den Wert mit dem DAC in eine Analogspannung.

Diese „geratene“ Spannung wird mit dem Signaleingang am Komparator verglichen. Ist der Komparatorausgang weiterhin niedriger, wird der Registerwert um ein Viertel des Bereichs vergrößert. Im Wesentlichen wird der Registerwert schrittweise in Faktor-Zwei-Schritten verkleinert oder vergrößert, bis der Komparator anzeigt, dass der vom DAC gewandelte Registerinhalt der Spannung des Eingangssignals entspricht. Dann gibt der Wandler das Signal „Wandlung abgeschlossen“ aus und hält den digitalen Wert im Ausgangs-Latch.

Die Wandlungszeit ist proportional zur ADC-Auflösung und wird durch die Länge des Registers bestimmt. SAR-ADCs bieten eine gute Auflösung bei kleinem bis mäßigem Stromverbrauch. Ein Beispiel für einen kostengünstigen, energieeffizienten SAR ist der MAX11665AUT-T von Maxim Integrated. Als 12-Bit-SAR-ADC mit 500 Kilosamples pro Sekunde (kS/s) eignet er sich gut für die Digitalisierung von Sensorausgängen.

Integrierender Dual-Slope-ADC

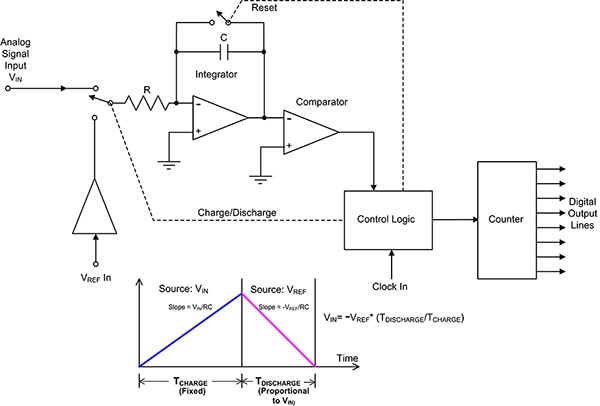

Integrierende ADCs bieten eine höhere Auflösung bei gleichzeitiger Minimierung der Auswirkungen des Rauschens. Dual-Slope-ADCs sind die häufigsten integrierenden ADCs (Abbildung 4).

Abbildung 4: Blockdiagramm eines integrierenden Dual-Slope-ADC und ein Diagramm, das zeigt, wie die Ladungs-/Entladungszeiten zur Ermittlung der unbekannten Eingangsspannung verwendet werden. (Bildquelle: DigiKey)

Zunächst wird der Eingang mit dem Integrator verbunden. Der Kondensator C wird vom Eingangssignal während einer festen Zeitdauer geladen. Ist diese Zeit abgelaufen, wird der Integrator mit der Referenzspannung verbunden. Dadurch wird der Kondensator bis auf null entladen, wie vom Komparator bestimmt. Ein Zähler misst die Zeit, die zur Entladung des Kondensators benötigt wird. Die Zeit ist proportional zur Eingangsspannung, die während des Ladezyklus auf den Kondensator einwirkt. Eine einfache Beziehung, basierend auf der bekannten Ladezeit und der gemessenen Entladezeit, ermöglicht die Berechnung der Eingangsspannung.

Weil die Signalspannung an einen Integrator angelegt wird, werden die Auswirkungen von Rauschsignalen durch den Mittelungseffekt des Integrators minimiert. Dual-Slope-Wandler sind ideal für Anwendungen mit hoher Auflösung, die eine hohe Genauigkeit erfordern. Üblich sind Auflösungen von 12 bis 16 Bit bei maximalen Abtastraten von bis zu 100 kS/s.

Die bekannteste Anwendung für Dual-Slope-ADCs sind digitale Voltmeter (DVM oder DMM). Der von Maxim Integrated angebotene 12-Bit-ADC ICL7109CPL+ mit dreistufigen Ausgängen ist ein Dual-Slope-Wandler zur Messung analoger Signale wie Druck, Drehzahl oder Durchfluss, mit Abtastraten von bis zu 30 Mal pro Sekunde.

Sigma-Delta-ADCs – hohe Auflösung bei niedrigen Frequenzen

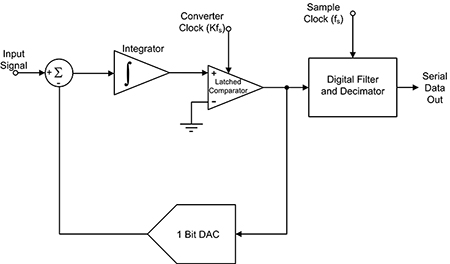

Sigma-Delta-ADCs bieten die höchste Auflösung (16 bis 24 Bit) für Signale mit niedriger Frequenz. Wie beim Dual-Slope-ADC handelt es sich auch hier um einen integrierenden Digitalisierer (Abbildung 5). Das Eingangssignal wird über einen Summierer an den Integrator angelegt. Der Ausgang des Integrators wird auf einen Komparator mit Latch angewandt, wo er mit einem Null-Volt-Signal (Masse) verglichen wird. Ist der integrierte Ausgang nicht null, wird der Komparatorausgang zurückgeleitet, um den Integratorausgang näher an null zu bringen. Dieser Prozess wird in der Wandlertaktfrequenz so oft wiederholt, bis der Integratorausgang null ergibt. Der Komparator bildet einen seriellen Datenstrom und damit den digitalen Ausgang des Wandlers.

Ein Sigma-Delta-ADC wird mit einer wesentlich höheren Rate abgetastet, als dies für die ausgelegte Abtastrate erforderlich ist.

In der Abbildung ist der Wandlertakt um den Faktor K schneller als der Ausgangsabtasttakt. Die „überflüssigen“ Abtastungen dienen der Bereitstellung einer digitalen Filterung des Wandlerausgangs. Ein Dezimator reduziert die Ausgangsabtastrate wieder auf die spezifizierte Abtasttaktrate.

Der von Analog Devices angebotene 24-Bit-ADC AD7734BRUZ ist ein 4-Kanal-Sigma-Delta-Digitalisierer für Anwendungen in der Prozesssteuerung und industriellen Steuerung.

Abbildung 5: Sigma-Delta-ADCs werden vielfach für eine hochauflösende Digitalisierung von Niederfrequenzsignalen für Anwendungen im Audio-Bereich, in der Prozesssteuerung und in industriellen Steuerungen eingesetzt. (Bildquelle: DigiKey)

Einen Überblick über die Auflösung und maximale Abtastrate der fünf besprochenen ADC-Typen finden Sie in Tabelle 2.

|

Tabelle 2: ADC-Betriebseigenschaften der fünf in diesem Artikel behandelten ADC-Typen. (Bildquelle: DigiKey)

Beispiel zur Topologie-Auswahl

Betrachten wir eine Anwendung zur Digitalisierung der Signale eines tragbaren Ultraschall-Entfernungsmessers mit einem 40-kHz-Transducer. Zielreflexionen sind -40 dB (1/100) von der Amplitude des übertragenen Pulses.

Das Signal muss mit einer Frequenz abgetastet werden, die mindestens das Doppelte der Signalfrequenz von 40 kHz beträgt. Besser ist eine Abtastung mit dem Vierfachen von 40 kHz oder mehr, sodass der erwünschte Abtastratenbereich 160 kHz oder mehr beträgt. Es ist anzuraten, eine Auflösung zu wählen, die mindestens das Zehnfache der erwarteten 40 dBm beträgt, also 60 dB. Die Faustregel lautet, dass für jede 6 dB 1 Bit Auflösung erforderlich ist, das heißt, es wird ein ADC mit 10-Bit-Auflösung oder mehr benötigt. Außerdem ist hier der Stromverbrauch zu beachten, da es sich um ein tragbares Instrument handelt. Mit Blick auf Tabelle 2 ergibt sich, dass der ADC der Wahl ein SAR-Wandler (Sukzessive Approximation) ist. Der bereits als Beispiel für einen SAR-ADC erwähnte MAX11665AUT-T von Maxim Integrated wäre gut für diese Anwendung geeignet.

Fazit

Da nicht beides gleichzeitig erreicht werden kann, ist die Auswahl eines ADC in erster Linie ein Kompromiss zwischen Abtastrate und Auflösung. Andere Aspekte wie Größe und Stromverbrauch spielen je nach Anwendung ebenfalls eine Rolle und sollten im Auswahlprozess entsprechend Beachtung finden.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.