Maximale Leistungsdichte und Performance in Schaltwandler-Anwendungen mit Dual-MOSFETs

2024-02-27

Wandler und Treiber in der Industrie- und Automobiltechnik benötigen Metalloxid-Silizium-Feldeffekttransistoren (MOSFETs), die klein und effizient sind und ein minimales elektrisches Rauschen erzeugen. Ein Dual-MOSFET-Ansatz hilft, diese Anforderungen zu erfüllen.

Durch die Unterbringung von zwei MOSFETs in einem einzigen Gehäuse benötigen gut konzipierte Dual-MOSFETs weniger Platz auf der Leiterplatte (PCB), verringern die parasitäre Induktivität und machen sperrige und teure Kühlkörper überflüssig, da sie die thermische Performance verbessern. Solche Bauelemente können bei mehreren hundert Kilohertz (kHz) störungsfrei schalten, über einen weiten Temperaturbereich stabil arbeiten und weisen einen geringen Leckstrom auf. Um die Vorteile dieser Komponenten voll ausschöpfen zu können, müssen jedoch ihre Betriebseigenschaften bekannt sein.

Dieser Artikel stellt Beispiele für Dual-MOSFETs von Nexperia vor und zeigt, wie sie eingesetzt werden können, um die Herausforderungen robuster, hocheffizienter und platzbeschränkter Designs zu meistern. Er erörtert Möglichkeiten zur Optimierung des Schaltungs- und Leiterplattendesigns und gibt Tipps zur elektrothermischen Simulation und Verlustanalyse.

Mehr Effizienz bei hoher Schaltgeschwindigkeit

Dual-MOSFETs eignen sich für viele Automobil- (AEC-Q101) und Industrieanwendungen, einschließlich DC/DC-Schaltwandler, Motorinverter und Magnetventilsteuerungen. Diese Anwendungen können unter anderem Dual-MOSFETs in Schalterpaaren und Halbbrückentopologien verwenden.

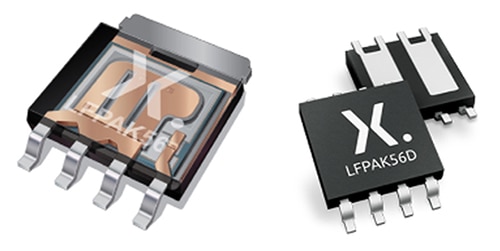

Die Serie LFPAK56D von Nexperia ist ein bemerkenswertes Beispiel für Dual-MOSFET-Bausteine. Sie verfügen über die Kupfer-Clip-Technologie von Nexperia, die eine außergewöhnliche Strombelastbarkeit, eine niedrige Gehäuseimpedanz und eine hohe Zuverlässigkeit ermöglicht (Abbildung 1, rechts). Diese massiven Kupferclips verbessern die Wärmeableitung vom Halbleitersubstrat durch die Lötstellen zur Leiterplatte, so dass etwa 30 % der gesamten abgeführten Wärme durch die Source-Pins fließen kann. Die großen Kupferquerschnitte verringern auch die ohmsche Verlustleistung und dämpfen das Klingeln durch Reduzierung der parasitären Leitungsinduktivität.

Abbildung 1: Der LFPAK56D (rechts) integriert zwei unabhängige MOSFETs und verwendet ähnliche Kupfer-Clip-Strukturen wie der LFPAK56 mit einem einzelnen MOSFET (links). (Bildquelle: Nexperia)

Abbildung 1: Der LFPAK56D (rechts) integriert zwei unabhängige MOSFETs und verwendet ähnliche Kupfer-Clip-Strukturen wie der LFPAK56 mit einem einzelnen MOSFET (links). (Bildquelle: Nexperia)

Wie die meisten Bauteile, die für Hochspannungs-Schaltwandler bestimmt sind, verwendet der LFPAK56D die Superjunction-Technologie. Dieses Design reduziert den Drain-Source-Durchlasswiderstand (RDS(on)) und die Gate-Drain-Ladung (QGD) und minimiert so die Leistungsverluste. Der Betrieb von zwei MOSFETs auf demselben Substrat reduziert den Drain-Source-Widerstand weiter.

Als Superjunction-MOSFETs ist die LFPAK56D-Serie robust gegen Avalanche-Ereignisse und hat einen großen sicheren Betriebsbereich (SOA). So hat beispielsweise jeder der 100-Volt-MOSFETs im TrenchMOS-Baustein PSMN029-100HLX einen RDS(on) von 29 Milliohm (mΩ), ist für 68 Watt ausgelegt und kann bis zu 30 Ampere (A) durchlassen.

Die Serie LFPAK56D verwendet außerdem die SchottkyPlus-Technologie von NXP, um Spiking-Verhalten und Leckstrom zu reduzieren. So beträgt der typische RDS(on) für den PSMN014-40HLDX typischerweise 11,4 mΩ, und der Drain-Source-Leckstrom liegt bei extrem niedrigen 10 nA (Nanoamperes).

Um die hohen Ströme der MOSFETs voll ausnutzen zu können, muss die Platine so konstruiert sein, dass sie viel Wärme ableiten kann und stabile elektrische Verbindungen gewährleistet. Mehrlagige Platinen mit ausreichenden Durchkontaktierungen und großen, dicken Kupferleiterbahnen gewährleisten eine hohe thermische Performance.

Thermisches Durchgehen vermeiden

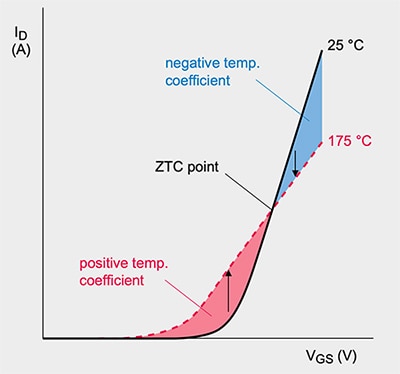

Während voll eingeschaltete Leistungs-MOSFETs thermisch stabil sind, besteht bei niedrigem Drainstrom (ID) die Gefahr eines thermischen Durchgehens.In diesem Betriebszustand neigt die lokale Erwärmung dazu, die Schwellenspannung zwischen Gate und Source (VGS(th)) zu senken, was bedeutet, dass das Bauelement leichter eingeschaltet werden kann. Dies führt zu einer positiven Rückkopplung, bei der der zusätzliche Strom eine stärkere Erwärmung und eine noch niedrigere VGS(th) verursacht.

Abbildung 2 zeigt diesen Effekt für eine konstante Drain-Source-Spannung (VDS). Mit steigender VGS gibt es einen kritischen ID, der als Nulltemperaturkoeffizient (ZTC) bekannt ist. Oberhalb dieses Stroms gibt es eine negative Rückkopplung und thermische Stabilität (blauer Bereich); unterhalb dominiert der Schwellenspannungsabfall, was zu thermisch instabilen Betriebspunkten führt, die zu thermischem Durchgehen führen können (roter Bereich).

Abbildung 2: Unterhalb des ZTC-Punktes kann der MOSFET aufgrund eines thermisch induzierten VGS (roter Bereich) in den thermischen Durchbruch geraten. (Bildquelle: Nexperia)

Abbildung 2: Unterhalb des ZTC-Punktes kann der MOSFET aufgrund eines thermisch induzierten VGS (roter Bereich) in den thermischen Durchbruch geraten. (Bildquelle: Nexperia)

Dieser Effekt reduziert den sicheren Betriebsbereich (SOA) bei niedrigen Strömen und hohen Drain-Source-Spannungen. Bei schnellen Schaltvorgängen mit steilem dV/dt-Anstieg ist dies kein großes Problem. Mit zunehmender Schaltdauer, z. B. zur Verringerung elektromagnetischer Störungen, wird die thermische Instabilität jedoch wahrscheinlicher und potenziell gefährlich.

Geringere Schaltverluste bei hohen Frequenzen

Bei der Auswahl eines Superjunction-MOSFET für schnell schaltende Anwendungen ist eine niedrige QGD von entscheidender Bedeutung, da dadurch die Schaltverluste erheblich reduziert werden.

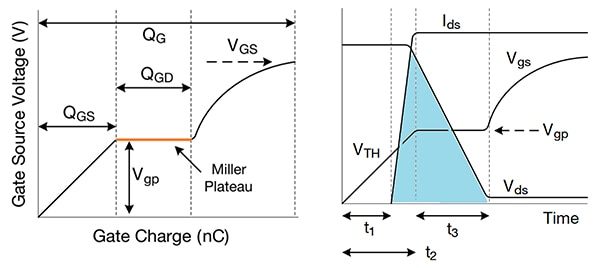

Eine hohe Verlustleistung tritt beim Schalten auf, wenn gleichzeitig erhebliche Spannungs- und Stromänderungen zwischen Drain, Gate und Source auftreten. Eine niedrige QGD führt zu einem kurzen Miller-Plateau (Abbildung 3, links), was zu einer steilen Schaltflanke (dVds/dt) und letztlich zu einem geringeren dynamischen Energieverlust beim Einschalten führt (Abbildung 3, blauer Bereich rechts).

Abbildung 3: Ein kurzes Miller-Plateau (links) bedeutet eine steile Schaltflanke, was zu geringen dynamischen Verlusten führt (blauer Bereich rechts). Vgp ist die Gate-Source-Spannung des Miller-Plateaus; VTH ist die Gate-Schwellenspannung; IDS ist der Drain-Source-Strom. (Bildquelle: Vishay)

Abbildung 3: Ein kurzes Miller-Plateau (links) bedeutet eine steile Schaltflanke, was zu geringen dynamischen Verlusten führt (blauer Bereich rechts). Vgp ist die Gate-Source-Spannung des Miller-Plateaus; VTH ist die Gate-Schwellenspannung; IDS ist der Drain-Source-Strom. (Bildquelle: Vishay)

Begrenzung der Avalanche-Energie und Schutz des MOSFET

Im Abschaltmoment einer Statorspule in einer Motorantriebsanwendung hält das kollabierende Magnetfeld den Stromfluss aufrecht und erzeugt eine hohe Induktionsspannung über dem MOSFET, die sich mit der Versorgungsspannung (VDD) überlagert. Die Durchbruchsspannung in Sperrrichtung (VBR) der MOSFET-Substratdiode begrenzt jedoch diese hohe Spannung. Durch den so genannten Avalanche-Effekt wandelt der MOSFET die abfließende magnetische Energie in Avalanche-Energie (EDS) um, bis der Spulenstrom auf Null sinkt. Dadurch kann der Halbleiterkristall schnell überhitzen.

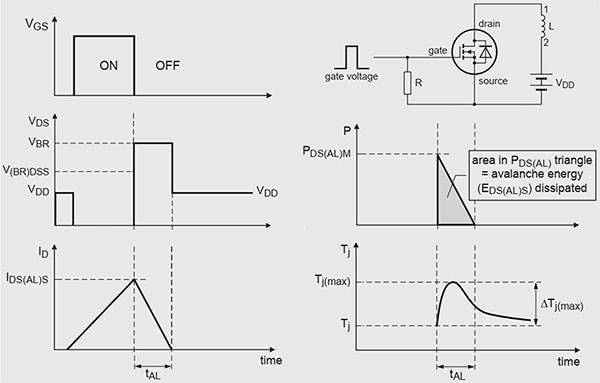

Abbildung 4 zeigt eine einfache Spulensteuerung mit einem MOSFET-Schalter und die Zeitsignale vor, während (Zeitfenster tAL) und nach einem einzelnen Lawinenereignis. Wenn die abgeleitete Avalanche-Energie (EDS(AL)S) zu hoch ist, wird die Halbleiterstruktur durch die entstehende Wärme beschädigt.

Abbildung 4: Zeitsignale eines MOSFET vor, während (tAL) und nach einem einzelnen Avalanche-Ereignis. (Bildquelle: Nexperia)

Abbildung 4: Zeitsignale eines MOSFET vor, während (tAL) und nach einem einzelnen Avalanche-Ereignis. (Bildquelle: Nexperia)

Die MOSFETs LFPAK56D sind sehr robust und können laut Nexperias Labortests mehrere Milliarden Lawinenereignisse unbeschadet überstehen. Unter Berücksichtigung der maximalen Avalanche-Energie können Spulentreiberstufen auf zusätzliche Freilauf- oder Klemmdioden verzichten und nur den Avalanche-Betrieb dieser MOSFETs nutzen.

Elektro-thermische Online-Simulation

Um die Systemeffizienz zu verbessern, reicht es nicht aus, sich auf eine einfache Leistungskennzahl (Gütefaktor, FOM) wie das Produkt RDS x QGD zu verlassen. Stattdessen muss eine genauere Verlustanalyse durchgeführt werden, bei der die MOSFET-Verluste berücksichtigt werden:

- Leitfähigkeit beim Einschalten

- Einschalt- und Ausschaltverluste

- Aufladen und Entladen der Ausgangskapazität

- Durchgangs- und Schaltverluste der Substratdiode

- Aufladen und Entladen der Gate-Kapazität

Um die Gesamtverluste zu minimieren, muss die Beziehung zwischen den MOSFET-Parametern und der Betriebsumgebung verstanden werden. Zu diesem Zweck bietet Nexperia elektrothermische Präzisionsmodelle für MOSFETs an, die elektrische und thermische Performance kombinieren und alle wichtigen MOSFET-Verhaltensweisen darstellen. Entwicklungsteams können den Online-Simulator PartQuest Explore verwenden oder die Modelle im SPICE- und VHDL-AMS-Format in die Simulationsplattform ihrer Wahl importieren.

Zum Zeitpunkt der Erstellung dieses Dokuments waren nur die elektrischen Modelle für die MOSFETs LFPAK56D verfügbar. Daher befasst sich das folgende Beispiel für eine thermische Simulation mit einem anderen MOSFET-Typ, dem BUK7S1R0-40H.

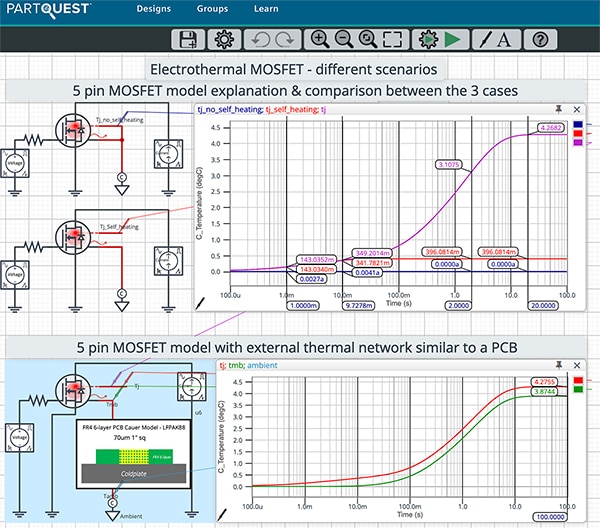

Das interaktive Experiment IAN50012 Electrothermal models for Power MOSFET simuliert drei Erwärmungsszenarien für den MOSFET BUK7S1R0-40H, nachdem ein Laststrom von 36,25 A eingeschaltet wurde. Abbildung 5 zeigt die drei Simulationsaufbauten auf der linken Seite.

Abbildung 5: Gezeigt wird eine elektrothermische Simulation eines MOSFET mit dem Online-Simulator PartQuest Explore. (Bildquelle: Nexperia)

Abbildung 5: Gezeigt wird eine elektrothermische Simulation eines MOSFET mit dem Online-Simulator PartQuest Explore. (Bildquelle: Nexperia)

Im oberen Fall „tj_no_self_heating“ sind die Anschlussstelle und der Montagesockel direkt an die Umgebungstemperatur (Tamb) von 0°C ohne Wärmewiderstand (Rth) gekoppelt. Im mittleren Fall, „tj_self_heating“, ist der Chip über Rth-j gekoppelt, und Tj steigt um etwa 0,4 °C. Der untere Fall zeigt einen über den Rth_mb an die Umgebungstemperatur gekoppelten Montagesockel (mb) einer sechslagigen FR4-Platine mit Kühlkörper. Tmb (grün) steigt auf 3,9°C und Tj (rot) steigt auf 4,3°C.

Fazit

Die extrem verlustarmen MOSFETs LFPAK56D bieten einen hervorragenden Wirkungsgrad und eine hohe Leistungsdichte in schnell schaltenden Umrichtern oder Motortreibern. Die hier besprochenen Überlegungen zum Schaltungs- und thermischen Platinendesign sowie die elektrothermische Simulation zeigen, wie die Herausforderungen robuster, hocheffizienter und platzbeschränkter Designs gemeistert werden können.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.