Unterschiedliche Funktions- und Sicherheitsanforderungen mit Multicore-Prozessoren erfüllen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-10-01

Es wird erwartet, dass Automobil-, Industrie-, Roboter-, Gebäudesteuerungs- und andere kritische eingebettete Systemanwendungen vielfältigere Arbeitslasten übernehmen werden, die von Echtzeit-Überwachung mit geringem Stromverbrauch bis hin zu Multimedia-Anwendungen auf hohem Niveau mit Mehrfachbildschirm-Grafikdisplays für Mensch-Maschine-Schnittstellen (HMIs) reichen. Neben der Erfüllung dieser breit gefächerten funktionalen Anforderungen müssen sie auch in der Lage sein, strenge Sicherheitsstandards zu unterstützen, die Kosten und den Platzbedarf zu senken und das Verhältnis zwischen Energieverbrauch und Performance zu optimieren.

Um diesen oft widersprüchlichen Anforderungen gerecht zu werden, waren die Entwickler bisher gezwungen, entweder funktionale Fähigkeiten zu opfern oder Design und Fertigung durch zusätzliche Komponenten zu komplizieren, die zur Unterstützung spezifischer Anforderungen u. a. an Grafik, Sicherheit und Schutz erforderlich sind. Was Entwickler wirklich brauchen, ist eine einzige Lösung, die in der Lage ist, eine breite Palette von Produkten zu unterstützen, die diese Anforderungen für eine Vielzahl kritischer eingebetteter Systemanwendungen erfüllen.

Dieser Artikel beschreibt kurz die Entwicklung des Designs kritischer eingebetteter Systeme. Anschließend wird gezeigt, wie Multicore-Anwendungsprozessoren, die speziell von NXP Semiconductors zur Unterstützung einer schnell wachsenden Liste von Anforderungen sowohl für breite Funktionalität als auch für zertifizierbare Sicherheitsfunktionen entwickelt wurden, zur Bewältigung der Herausforderungen von Entwicklern eingesetzt werden können.

Die Evolution der Überlegungen zum Entwurf eingebetteter Systeme

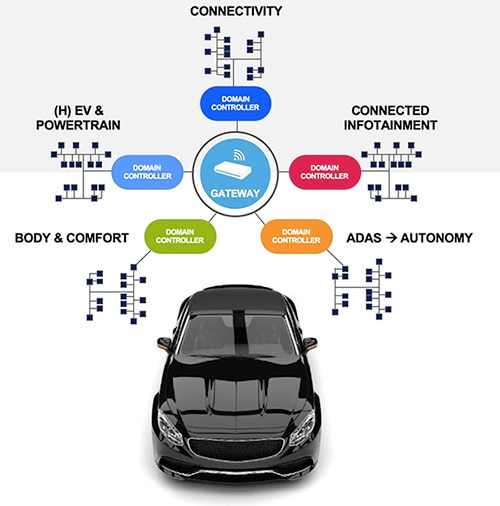

Die traditionelle Rolle eingebetteter Komponenten bei der Unterstützung eines begrenzten Satzes von Systemfunktionen ist weitgehend durch die Nachfrage nach Komponenten ersetzt worden, die umfassende Fähigkeiten bieten. Bei industriellen Anwendungen beispielsweise erfordert der Bedarf an erweiterten HMI-Funktionen in intelligenten Werkzeugen und Geräten Prozessoren, die optimierte Grafiken liefern und gleichzeitig die traditionelleren industriellen Echtzeitanforderungen erfüllen. In ähnlicher Weise führt der Trend in Automobilanwendungen zu hierarchischen Architekturen mit funktionalen Domänen-Clustern und Gateways zu einem Bedarf an Prozessoren, die diese Anforderungen voll erfüllen können (Abbildung 1).

Abbildung 1: Der Trend zu hierarchischeren automobilen Systemarchitekturen hat einen Bedarf an stärker integrierten, skalierbaren Prozessorlösungen geschaffen. (Bildquelle: NXP Semiconductors)

Abbildung 1: Der Trend zu hierarchischeren automobilen Systemarchitekturen hat einen Bedarf an stärker integrierten, skalierbaren Prozessorlösungen geschaffen. (Bildquelle: NXP Semiconductors)

Innerhalb jedes Funktionsbereichs erhöht die Nachfrage nach anspruchsvolleren Fähigkeiten weiterhin die Schwelle für Leistung und integrierte Fähigkeiten. Beispielsweise erfordert das Aufkommen von Heads-up-Displays Lösungen, die in der Lage sind, die kontinuierliche Bereitstellung wichtiger grafischer Informationen für die Fahrer zu gewährleisten. Neben diesen Displays der nächsten Generation stellt der wachsende Bedarf an verbesserter Fahrersensibilität zusätzliche Anforderungen an Kameraschnittstellen und die leistungsstarke Ausführung einer fortschrittlichen Erkennungssoftware, die in der Lage ist, Schläfrigkeit zu erkennen.

Mit der Weiterentwicklung von Anwendungen wird der Bedarf an hochintegrierten, skalierbaren Lösungen immer dringender, um den immer vielfältigeren Anforderungen gerecht zu werden und gleichzeitig den Design-Footprint, die Kosten und die Komplexität zu minimieren. Mit den Anwendungsprozessoren der Familie i.MX 8 von NXP können Entwickler eine kompatible Plattform von Prozessoren mit der Bandbreite an Fähigkeiten und Leistung nutzen, die zur Unterstützung eines breiten Spektrums von Anwendungsanforderungen erforderlich ist. Innerhalb der Familie i.MX 8 adressiert die Serie i.MX 8X von NXP den aufkommenden Bedarf an sicherheitszertifizierbaren Prozessoren, die in Automobil- und Industrieanwendungen der mittleren Leistungsklasse benötigt werden.

Multicore-Architektur verwaltet unterschiedliche Arbeitslasten

Eine der Schwierigkeiten, auf die Entwickler bei der Implementierung von Komponenten für Automobil- und Industrieanwendungen stoßen, ist die schiere Breite der Anforderungen. Wo Entwickler damit rechnen konnten, dass sie entweder mit Echtzeit- oder mit High-Level-Anwendungsverarbeitungprozessen zurechtkommen müssen, hat die Nachfrage nach intelligenten Subsystemen diese signifikant unterschiedlichen Arten der Datenverarbeitung zusammengeführt. Entwickler benötigen in zunehmendem Maße Lösungen, die sowohl eine zuverlässige Reaktion in Echtzeit als auch eine hochleistungsfähige Anwendungsausführung ermöglichen und gleichzeitig die Anforderungen an die funktionale Sicherheit unterstützen.

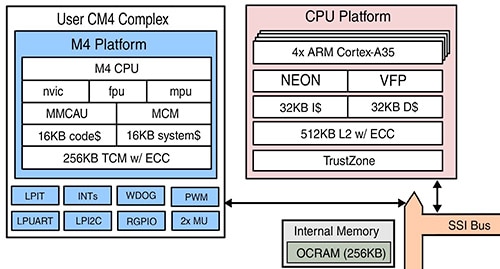

Die Prozessoren der Serie i.MX 8X von NXP, die für Echtzeitfähigkeiten, Hochleistungsprozesse und niedrigen Stromverbrauch ausgelegt sind, nutzen die Vorteile einer hochentwickelten Multicore-CPU-Architektur (Central Processing Unit) voll aus, um unterschiedliche Rechenlasten zu bewältigen (Abbildung 2).

Abbildung 2: Die Serie i.MX 8X von NXP verwendet eine Multicore-Architektur, die einen eingebetteten Arm-Cortex-M4-(CM4)-Prozessor und mehrere Arm-Cortex-A35-Anwendungsprozessoren umfasst, um gemischte Software-Prozesse zu unterstützen. (Bildquelle: NXP Semiconductors)

Abbildung 2: Die Serie i.MX 8X von NXP verwendet eine Multicore-Architektur, die einen eingebetteten Arm-Cortex-M4-(CM4)-Prozessor und mehrere Arm-Cortex-A35-Anwendungsprozessoren umfasst, um gemischte Software-Prozesse zu unterstützen. (Bildquelle: NXP Semiconductors)

Für allgemeine Echtzeitprozesse umfassen die Komponenten i.MX 8X einen Arm-Cortex-M4-(CM4)-Prozessor mit Gleitkommaeinheit (FPU), eine Speicherschutzeinheit (MPU), eine speicherbezogene kryptografische Beschleunigungseinheit (MMCAU) und ein vielseitiges Steuermodul (MCM). Zur Unterstützung externer Peripheriekomponenten wie Sensoren und Aktuatoren kombiniert dieser Anwender-CM4-Komplex einen verschachtelten Vektor-Interrupt-Controller (NVIC) mit einem umfassenden Satz von Schnittstellen und Modulen, einschließlich eines energieeffizienten LPIT (Low-power Periodic Interrupt Timer), Pulsweitenmodulation (PWM) und anderen Funktionen, die häufig in Automobil- und Industrieanwendungen benötigt werden. Ein Paar aus Cache-Speichern und eng gekoppeltem Speicher (TCM) mit ECC-Fähigkeit (Error Correction Code) hilft, den externen Speicherzugriff zu minimieren, die Ausführung zu beschleunigen und mit Speicherfehlern umzugehen.

Für die schnelle Ausführung von Anwendungsprozessen umfasst die CPU-Plattform mehrere energieeffiziente Arm-Cortex-A35-Anwendungsprozessoren (APs), zwei APs in 8DualXPlus-Prozessoren, wie z.B. den MIMX8UX6AVLFZAC, und vier APs in 8QuadXPlus-Prozessoren, wie z.B. den MIMX8QX6AVLFZAC. Neben einem dedizierten Befehls- (I$) und Daten-Cache (D$) umfasst die CPU-Plattform einen gemeinsam genutzten 512 Kilobyte (Kbyte) großen Level-2-Cache (L2) mit ECC.

Die Arm-Cortex-A35-Kerne der Architektur bieten sowohl Software-Kompatibilität als auch Leistungsskalierbarkeit und unterstützen sowohl 32-Bit-Abwärtskompatibilität als auch 64-Bit-Leistung. Um die Ausführung rechenintensiver Algorithmen wie Signalverarbeitung und maschinelles Lernen weiter zu beschleunigen, bieten die Arm-Cortex-A35-Prozessoren eine Vector-Floating-Point(VFP)-Verarbeitung und SIMD-Architekturerweiterungen (SIMD: Single Instruction Multiple Data) mit Arms Neon. Um die Ausführung von Software für Bildverarbeitung, Computer-Bilderfassung und maschinelles Lernen zu beschleunigen, bietet die Arm-Compute-Library Funktionen, die für Arm-Prozessor- und GPU-Architekturen (Graphics Processing Unit) optimiert sind, und die Open-Source-C-Bibliothek Ne10 bietet Arm-optimierte Funktionen für rechenintensive Operationen.

Dedizierte Engines entlasten primäre CPUs

Neben dem Benutzer-CM4-Komplex und der Arm-Cortex-A35-Mehrkern-CPU-Plattform bietet die Architektur zusätzliche dedizierte Engines für Multimedia-Anwendungen. Zusammen mit einem digitalen Signalprozessor (DSP) für die Verarbeitung von Audio- und Sprachcodecs integriert die Architektur sowohl eine GPU als auch eine Videoverarbeitungseinheit (VPU). Der Grafikprozessor des Geräts unterstützt Standardgrafikbibliotheken und beschleunigt Operationen unter Verwendung von vier separaten Vier-Komponenten-Gleitkomma-Vektoren (vec4) mit 16 Ausführungseinheiten und einer leistungsstarken, zweidimensionalen Bit-Blit-Engine. Die VPU verarbeitet gängige Videoformate und beschleunigt die Dekodierung auf bis zu 4Kp30 (progressiv, 30 Hz) und die Kodierung auf bis zu 1080p30. Im Gegenzug kann der dedizierte Display-Controller-Block des Chips die Grafikausgabe auf bis zu drei unabhängigen Displays steuern.

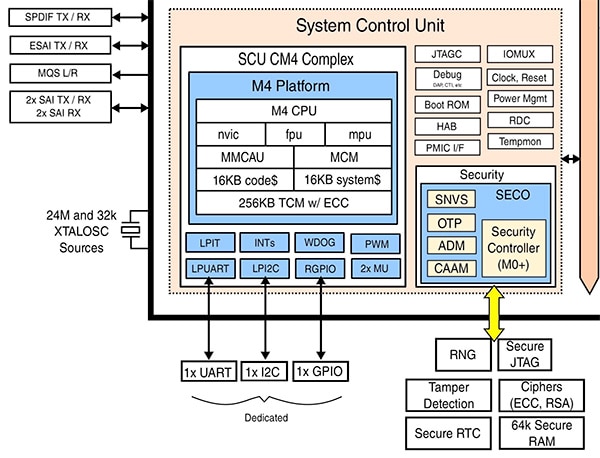

Um die Leistung weiter zu maximieren, integriert die i.MX-8X-Architektur auch zusätzliche Prozessorkerne, die die primären CPU-Plattformen von der zusätzlichen Verarbeitungslast befreien sollen, die typischerweise bei der Ausführung von Systemverwaltungs- und Sicherheitsdiensten anfällt. Für das Systemmanagement integriert die Systemsteuerungseinheit (SCU) der Architektur einen CM4-Komplex, der dem CM4-Komplex des Benutzers entspricht, jedoch vollständig für den SCU-Betrieb reserviert bleibt und für die Entwickler nicht zur Verfügung steht (Abbildung 3).

Abbildung 3: Die SCU ist tief in die i.MX-8X-Prozessoren von NXP integriert und für Entwickler nicht verfügbar. Sie verwendet ein dediziertes Arm-Cortex-M4(CM4)-Subsystem, um Systemverwaltungsaufgaben von den Hauptprozessoren des Geräts zu entlasten. (Bildquelle: NXP Semiconductors)

Abbildung 3: Die SCU ist tief in die i.MX-8X-Prozessoren von NXP integriert und für Entwickler nicht verfügbar. Sie verwendet ein dediziertes Arm-Cortex-M4(CM4)-Subsystem, um Systemverwaltungsaufgaben von den Hauptprozessoren des Geräts zu entlasten. (Bildquelle: NXP Semiconductors)

Neben der Verwaltung der Stromversorgung, der Taktung und anderer interner Funktionen steuert die SCU das Pin-Multiplexing und die Stärke der Ein-/Ausgabekanäle (I/O) im Normalbetrieb. Tatsächlich können der Benutzer-CM4-Komplex und die Arm-Cortex-A35-APs nicht direkt auf diese verschiedenen Low-Level-Hardware-Fähigkeiten zugreifen. Stattdessen dient die SCU dazu, diese Fähigkeiten zu abstrahieren, so dass Software, die auf dem Benutzer-CM4 oder APs läuft, lediglich Funktionen der SCU-Firmware-API (Application Programming Interface) aufrufen muss, um Funktionen wie das Ausschalten nicht benötigter Leistungsdomänen auszuführen. Wenn diese Leistungsdomäne z. B. mit einem anderen Prozessor gemeinsam genutzt wird, bestätigt die SCU einfach die Anforderung zum Herunterfahren, lässt die Domäne jedoch so lange eingeschaltet, bis der andere Prozessor ebenfalls eine Anforderung zum Herunterfahren sendet.

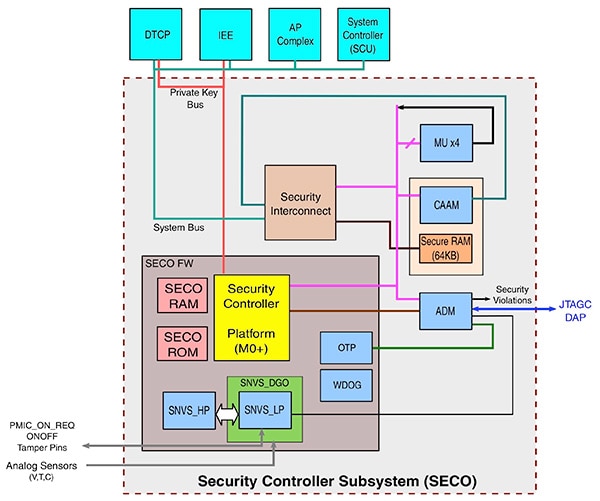

Um die umfangreiche Sicherheitsunterstützung der i.MX-8X-Komponente zu verwalten, kommt im SECO-Subsystem (Security Controller) des Geräts ein weiterer dedizierter Prozessor zum Einsatz. Innerhalb des SECO-Subsystems führt ein integrierter Low-Power-Arm-Cortex-M0+-Prozessor Firmware aus, die hardwarebasierte Sicherheitsfunktionen unterstützt, darunter einen privaten Buszugriff für sichere Schlüssel, einen einmalig programmierbaren (OTP) Speicher für die sichere Schlüsselspeicherung und einen sicheren nichtflüchtigen Speicher (SNVS) für zusätzliche private Daten oder flüchtige Schlüssel (Abbildung 4).

Abbildung 4: Innerhalb des i.MX-8X-SECO-Subsystems (Security Controller) von NXP verwaltet ein dedizierter Arm-Cortex-M0+-Prozessor mit niedrigem Stromverbrauch die Sicherheitsoperationen und greift dabei auf einen Private-Key-Bus und mehrere Hardware-Module für sichere Speicherung, Kryptographie-Beschleunigung und authentifizierten Debug-Zugriff zurück. (Bildquelle: NXP Semiconductors)

Abbildung 4: Innerhalb des i.MX-8X-SECO-Subsystems (Security Controller) von NXP verwaltet ein dedizierter Arm-Cortex-M0+-Prozessor mit niedrigem Stromverbrauch die Sicherheitsoperationen und greift dabei auf einen Private-Key-Bus und mehrere Hardware-Module für sichere Speicherung, Kryptographie-Beschleunigung und authentifizierten Debug-Zugriff zurück. (Bildquelle: NXP Semiconductors)

Über diese Kernsicherheitsmechanismen hinaus koordiniert das SECO-Subsystem über sein ADM (Authenticated Debug Module) vermittelte Sicherheitsoperationen zur Manipulationserkennung und sicheren Fehlersuche. Für eine sichere Ausführung unterstützt das integrierte Hardware-Sicherheitsmodul CAAM (Cryptographic Acceleration and Assurance Module) eine vollständige Suite von Sicherheitsalgorithmen einschließlich symmetrischer und asymmetrischer Kryptographie, Hash-Funktionen und einen Zufallszahlengenerator (RNG).

Im Normalbetrieb verwenden die Geräteverarbeitungseinheiten einschließlich der SCU, der APs und des DTCP-Beschleunigers (Digital Transport Content Protection) die SECO-Sicherheitsverbindung, um über den Systembus auf die CAAM-Funktionalität zuzugreifen. Anders als beim Zugriff über die CAAM-Funktionalität des direkten Speicherzugriffs (DMA) kann der dedizierte Cortex-M0+-Prozessor des SECO nicht auf den Systembus zugreifen. Stattdessen verwendet es geschützte interne Verbindungen für den Zugriff auf Peripheriegeräte, sicheren Arbeitsspeicher (RAM) und Nur-Lese-Speicher (ROM) sowie seinen speziellen Bus für private Schlüssel.

Zusammen mit der Verwendung des DTCP-Beschleunigers spielt dieser private Schlüsselbus eine zentrale Rolle bei der Unterstützung des i.MX-8X-Prozessors für die On-the-fly-Verschlüsselung und -Entschlüsselung. Hier nutzt der Sicherheitsprozessor seine Ressourcen, um private Schlüssel bereitzustellen, die vom IEE-Modul (Inline Encryption/Decryption Engine) der Komponente benötigt werden, während sie sicher von verschlüsseltem Speicher liest oder auf diesen schreibt, ohne Beteiligung des anfordernden Prozessors, DMA-Controllers oder I/O-Geräts.

Aufbauend auf der TrustZone-Technologie von Arm, die in die Cortex-A35-Prozessoren der Komponente integriert ist, arbeitet das SECO-Subsystem auch während des sicheren Bootvorgangs mit der SCU zusammen. In diesem Prozess interpretiert die SCU die Boot-Einstellungen, konfiguriert die Boot-Quellen und lädt Boot-Images in den internen oder externen Speicher. Das SECO-Subsystem wiederum verwendet seine Kryptographiefunktionen, um signierte Firmware-Images nach dem Laden, aber vor der Ausführung zu authentifizieren.

Sicherung kritischer Anzeigen und Steuerungsfunktionen

Während die Fähigkeit, unterschiedliche Arbeitslasten effizient und sicher zu verarbeiten, wichtig ist, ist für einsatzkritische Anwendungen, wie z.B. im Automobil- und Industriesektor, die Fähigkeit zur Sicherung von Schlüsselfähigkeiten ebenso wichtig. Die i.MX-8X-Familie von NXP kombiniert ihre Verarbeitungsfunktionen mit zertifizierbaren Sicherheitsfunktionen, die zur Erfüllung dieser kritischen Anforderungen erforderlich sind.

Die Sicherheitsunterstützung der Prozessorfamilie ist auf mehreren Ebenen eingebaut, beginnend mit der Herstellung in einer FD-SOI-Prozesstechnologie (Fully Depleted Silicon on Insulator), die die Systemzuverlässigkeit erhöht. Da die Systemsicherheit von einer robusten Sicherheitsgrundlage abhängt, kann die Kombination aus TrustZone-fähigen APs, dem SECO-Subsystem und sicheren Boot-Fähigkeiten die Art von vertrauenswürdiger Umgebung bieten, die zur Abwehr von Sicherheitsbedrohungen erforderlich ist.

Gleichzeitig trägt die Fähigkeit, zeitkritische Aufgaben mit dem Benutzer-CM4-Komplex selbstständig abzuwickeln und kritische Systemaufgaben auf die SCU- und SECO-Subsysteme zu verlagern, dazu bei, dass missionskritische Anwendungskapazitäten trotz unterschiedlicher Verarbeitungslast verfügbar bleiben. Tatsächlich erweitert NXP dieses Konzept auf die Unterstützung unternehmenskritischer Displays durch die SafeAssure-Technologie des Unternehmens, die einen ASIL-B-fähigen (Automotive Safety Integrity Level B) Hardware-Display-Failover-Pfad in i.MX-8X-Komponenten integriert. Mit SafeAssure wird den Benutzern automatisch ein Failover-Image zur Verfügung gestellt, wenn das Gerät einen Datenintegritäts- oder GPU-Fehler erkennt. Dieses Failover-Image läuft im Hintergrund und stellt sicher, dass kritische Informationen auch bei Ausfall der primären Anzeige verfügbar bleiben.

Die Unterstützung für Sicherheitsanwendungen erstreckt sich auch auf den Speicherzugriff in i.MX-8X-basierten Systemen. Neben den unterstützten Speicherschnittstellen bieten die i.MX-8X-Bausteine 8-Bit-ECC für DDR3L-Speicher (Double Data Rate 3 Low Voltage). Zusammen mit ECC im L2-Cache (siehe wieder Abbildung 2) unterstützt diese DDR3L-ECC-Fähigkeit den industriellen Sicherheits-Integritätsgrad 3 (SIL 3). Die i.MX-8X-Architektur erweitert die ECC-Unterstützung auch auf externe Flash-Speichergeräte. Hier bietet ein integriertes BCH-Kodier- und -Dekodiermodul (BCH: Bose, Ray-Chaudhuri, Hocquenghem) einen 62-Bit-ECC, der in der Lage ist, 2 bis 20 Einzelbitfehler innerhalb eines Datenblocks zu korrigieren, der von diesen Speichergeräten gelesen wird.

Entwicklung von i.MX-8X-basierten Anwendungen

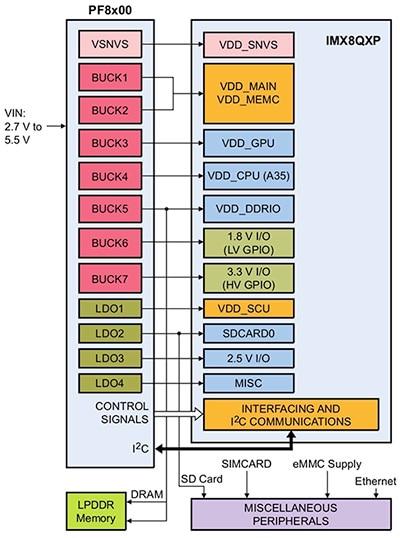

Wie bei jedem Prozessor dieser Klasse erfordert die Implementierung eines i.MX-8X-basierten Designs die sorgfältige Beachtung strenger Leistungsanforderungen, einschließlich kritischer Einschaltsequenzen. Das Einschalten von i.MX-8X-Bausteinen erfordert das sequentielle oder gleichzeitige Einschalten von vier verschiedenen Versorgungsgruppen, beginnend mit dem SVNS-Subsystem, über die SCU, die I/Os und Speicherschnittstellen bis hin zum Rest des Bausteins. Entwickler können diese Anforderung einfach mit den PMIC-Bausteinen (Power Management Integrated Circuit) PF8x00 von NXP erfüllen, die einen kompletten Satz von Spannungsschienen und Steuersignalen bereitstellen, die zur Unterstützung von i.MX-8X-Prozessoren sowie externen Speichern und typischen Systemperipheriegeräten benötigt werden (Abbildung 5).

Abbildung 5: Die PMICs PF8x00 von NXP bieten einen vollständigen Satz von Spannungsschienen und Steuersignalen, die zur Versorgung von i.MX-8X-Prozessoren benötigt werden. (Bildquelle: NXP Semiconductors)

Abbildung 5: Die PMICs PF8x00 von NXP bieten einen vollständigen Satz von Spannungsschienen und Steuersignalen, die zur Versorgung von i.MX-8X-Prozessoren benötigt werden. (Bildquelle: NXP Semiconductors)

Bei der Implementierung ihrer eigenen i.MX-8X-basierten Designs können Entwickler den PMIC MC33PF8100CCES von NXP verwenden, der für die Verwendung mit 8QuadXPlus-Prozessoren wie dem MIMX8QX6AVLFZAC vorprogrammiert ist. Andere PF8x00-Varianten wie die MC33PF8100A0ES und MC33PF8200A0ES unterstützen i.MX-8X-Prozessoren, sind aber nicht vorprogrammiert.

Für Sicherheitsanwendungen bieten die Komponenten der PF8200-Serie wie der MC33PF8200A0ES Funktionen zur Unterstützung von ASIL-B-Systemen. Neben mehreren internen Monitoren, darunter ein Ausgangsspannungsmonitor mit einer dedizierten Bandlückenreferenz, verfügen die PMICs PF8200 über einen FSOB-Pin (Fail-Safe Output), der das System während des Einschaltens oder bei einem Stromausfall in einem sicheren Zustand hält. Darüber hinaus testet eine analoge eingebaute Selbsttestroutine (ABIST) alle Spannungsüberwachungsbausteine, während eine andere Selbsttestroutine die Funktionalität anderer Komponenten überprüft.

Obwohl PF8x00-PMICs das Hardware-Design von i.MX 8X-basierten Systemen vereinfachen können, müssen einige Entwickler möglicherweise sofort mit der Evaluierung von i.MX-8X-Komponenten beginnen und schnell Prototypen von i.MX-8X-basierten Anwendungen erstellen. Das i.MX-8X-MEK (Multisensory Enablement Kit) MCIMX8QXP-CPU von NXP bietet eine fertige Entwicklungsplattform, die einen i.MX-8QuadXPlus-Prozessor von NXP, den PMIC F8100 von NXP, 3 Gigabyte (Gbyte) RAM, 32 GByte eMMC-Speicher (embedded Multi-Media Controller) und 64 Megabyte (MByte) Flash-Speicher kombiniert. Neben Anzeige-, Kamera- und Audioschnittstellen enthält das MEK-Board eine Reihe von Sensoren, die typischerweise in Automobil- oder Industrieanwendungen eingesetzt werden. Das optionale MCIMX8-8X-BB-Basisboard enthält das IMX-AUD-IO-Board und kann für zusätzliche Vernetzungs-, Audio- und Erweiterungsoptionen verwendet werden.

Fazit

Für eine wachsende Zahl von Anwendungen in den Bereichen Automobilelektronik, Industrie, Gebäudesteuerung und HMI wurden die benötigten Rechenkapazitäten immer größer und umfassen nun sowohl die traditionelle Echtzeit-I/O-Verarbeitung als auch die aufkommende Verarbeitung auf Anwendungsebene mit Multimedia-Grafiken. Obwohl es für jede Art von Rechenlast Lösungen gibt, erfüllen nur wenige den wachsenden Bedarf an leistungsstarken und energieeffizienten Komponenten, die die Anforderungen an sicherheitszertifizierbare Designs in Automobil- und Industrieanwendungen erfüllen können.

Wie gezeigt, können Entwickler mit einer Familie von Multicore-Prozessoren von NXP Semiconductors Designs effektiver implementieren, die diesen unterschiedlichen Anforderungen gerecht werden, und sie können problemlos skaliert werden, um neuen Anforderungen an hohe Leistung gerecht zu werden.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.