Vorteile von I3C für eine schnellere, einfachere und flexiblere Kommunikation zwischen integrierten Schaltkreisen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2024-12-17

Als serielle Schnittstellen für die Kommunikation zwischen integrierten Schaltkreisen (ICs) in einem Geräte werden in den allermeisten Fällen die I²C-Schnittstelle (Inter-Integrated Circuit) und die SPI-Schnittstelle (Serial Peripheral Interface) genutzt, die seit den 1980er Jahren verfügbar sind. Diese Schnittstellen dienen häufig zur Verbindung von Sensoren und ICs mit geringerer Geschwindigkeit mit Mikrocontrollern (microcontroller units, MCUs) für die geräteinterne Kommunikation über kurze Strecken. Da digitale Systeme jedoch immer schneller werden, sind diese Schnittstellen, die auf typische Datenraten von 1 Megabit pro Sekunde (Mbit/s) bei I²C und 10 Mbits/s bei SPI beschränkt sind, zu einem begrenzenden Faktor geworden. Andere Beschränkungen, einschließlich dedizierter Interrupt- oder Chip-Freigabe-Leitungen, erfordern zusätzliche Signalverbindungen, was die Anzahl der Drähte und die Komplexität der Busverbindungen erhöht.

Der I3C-Bus (Improved Inter-Integrated Circuit) soll eine schnellere Kommunikation zwischen ICs realisieren. Er bietet höhere Datenraten, größere Flexibilität und eine echte Zwei-Draht-Schnittstelle mit In-Band-Interrupts (IBIs) anstelle von externen Interrupts.

In diesem Artikel werden die charakteristischen Eigenschaften der I3C-Schnittstelle erörtert sowie die Gründe, aus denen sich eine Umstellung von den seriellen Schnittstellen I²C und SPI lohnt. Anhand typischer MCUs sowie Schalt-ICs und Sensoren werden seine möglichen Einsatzfelder verdeutlicht.

Eingebettete Kommunikationsbusse

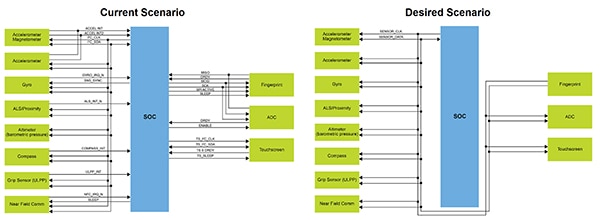

Eingebettete serielle Verbindungen wie I²C und SPI dienen seit vielen Jahren für die platineninterne Kommunikation. Sie werden in erster Linie als Kommunikationsbusse zwischen Sensoren und Benutzerschnittstellenkomponenten und deren Steuerprozessoren eingesetzt. Die Zahl der Sensoren in typischen Systemen ist auf zehn bis zwanzig in einem Telefon und deutlich mehr in Fahrzeugen angewachsen. Gleichzeitig sind die bei der Entwicklung zu berücksichtigenden Anforderungen an die Kommunikation anspruchsvoller geworden, da zunehmend höhere Geschwindigkeiten, eine niedrigere Leistungsaufnahme und weniger Leiter gefordert sind. Ein Design muss diesen zusätzlichen Anforderungen gerecht werden ohne Abstriche bei der Prozessorkontrolle über Interrupts und Freigabeleitungen (Abbildung 1).

Abbildung 1: Die eingebettete Kommunikation muss zunehmend höhere Geschwindigkeiten unterstützen und das bei einer niedrigeren Leistungsaufnahme und minimalen Drahtanzahl. (Bildquelle: NXP Semiconductors)

Abbildung 1: Die eingebettete Kommunikation muss zunehmend höhere Geschwindigkeiten unterstützen und das bei einer niedrigeren Leistungsaufnahme und minimalen Drahtanzahl. (Bildquelle: NXP Semiconductors)

Die aktuelle Technologie implementiert die Schnittstelle zwischen Sensoren und Komponenten zur Benutzersteuerung in Form von I²C- oder SPI-Schnittstellen mit zwei Drähten. Interrupt-, Freigabe- und andere Steuerleitungen sind von den Takt- und Datenleitungen getrennt, was zu mehr Leitungen pro Schnittstelle führt.

Moderne Designs bedürfen eines zukunftsweisenden Verbindungsansatzes, bei dem diese zusätzlichen Leiter nicht mehr benötigt werden und die entsprechenden Operationen nur noch „im Band“ über die Takt- und Datenleitungen ausgeführt werden. Außerdem sollte der Bus mit höheren Geschwindigkeiten und gesenkten Leistungsverlusten betrieben werden können.

I3C-Schnittstelle

I3C wurde von der Mobile Industry Processor Interface (MIPI) Alliance entwickelt, um diese Anforderungen zu erfüllen. Die Schnittstelle ist als MIPI I3C für MIPI-Mitglieder und als MIPI I3C Basic mit reduzierter Funktionalität für Nicht-Mitglieder verfügbar. Wie die Vorgängerschnittstellen I²C und SPI ist die verbesserte Variante seriell und nutzt zwei Drähte, um die Polzahl und die Anzahl der Signalwege zwischen Komponenten zu minimieren. Sie bietet eine Datenrate von bis zu 12,5 Mbit/s mit einem Takt von 12,5 Megahertz (MHz) im SDR-Modus (Single Data Rate - einfache Datenrate). Sie benötigt weniger Strom zum Betrieb und verwendet eine einfache, aber flexible Architektur.

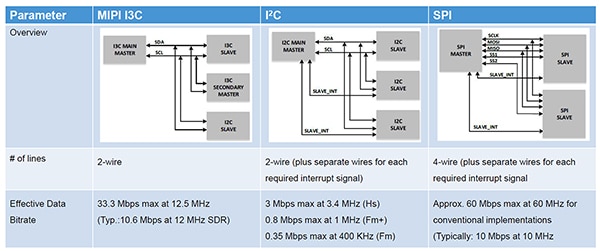

Der I3C-Standard behält eine begrenzte Rückwärtskompatibilität mit dem I²C-System bei, so dass vorhandene I²C-Komponenten an den I3C-Bus angeschlossen werden können, während der Bus weiterhin auf höhere Datenraten für die Kommunikation zwischen konformen I3C-Komponenten umschalten kann. Ein Vergleich der Systemkonfigurationen ist in Abbildung 2 dargestellt.

Abbildung 2: Der Vergleich der Grundkonfigurationen von I3C-, I²C- und SPI-Schnittstellen zeigt die höhere Geschwindigkeit und die einfachere Verdrahtung von I3C. (Bildquelle: NXP Semiconductors)

Abbildung 2: Der Vergleich der Grundkonfigurationen von I3C-, I²C- und SPI-Schnittstellen zeigt die höhere Geschwindigkeit und die einfachere Verdrahtung von I3C. (Bildquelle: NXP Semiconductors)

Die SPI-Schnittstelle mit vier Drähten unterstützt höhere Geschwindigkeiten und Vollduplex-Kommunikation. Die I²C-Kommunikation nutzt das Halbduplex-Verfahren über einen Zweidraht-Bus, der aus einer Takt- (SCL) und einer Datenleitung (SDA) besteht. Beide benötigen zusätzliche Leitungen, um Interrupts und andere Steuerfunktionen wie die Chipauswahl zu unterstützen. I3C reduziert die Anzahl der in der Schnittstelle verwendeten Drähte auf zwei, wodurch die in I²C und SPI erforderlichen separaten Interrupt-, Freigabe- und Chipauswahlleitungen entfallen. Diese gesenkte Drahtanzahl stellt einen bedeutenden Vorteil dar in einem System, das zehn bis zwanzig einzelne Sensoren benötigt, die mit dem Prozessor verbunden sind und jeweils mehrere sekundäre Drähte besitzen. Interrupts und andere Steuerleitungen werden durch IBIs ersetzt. Bei dieser Methode fügt ein Sensor oder eine Komponente seine Adresse in den Adress-Header des I3C-Busses ein, um den Prozessor über einen Interrupt zu informieren.

Der Unterschied in den Taktraten von I²C und I3C ist erheblich. I²C wird im Allgemeinen mit 100 Kilohertz (kHz), 400 kHz oder 1 MHz getaktet, während I3C einen Takt von 12,5 MHz unterstützt. Bisher wurde SPI für Taktraten von mehr als 1 MHz verwendet. Das entscheidende Kriterium bei der Entwicklung war entweder die Taktrate oder die Anzahl der Drähte. I3C hat das geändert, indem es höhere Takt- und Datenraten mit einer echten Zweidraht-Topologie bietet.

Push-Pull-Ausgänge, die schneller als Open-Drain- oder Kollektor-Treiber schalten können, tragen wesentlich zur erhöhten Taktrate von I3C bei. Um die Kompatibilität mit I²C-Komponenten zu wahren, kann I3C je nach Zustand des Busses zwischen Open-Drain- und Push-Pull-Treiber wechseln. Das Open-Drain- oder Kollektor-Design wird während der anfänglichen Adressierung oder der Arbitrierung verwendet, wenn eine simultane Kommunikation von I²C- oder I3C-Komponenten möglich ist. Push-Pull wird bei I3C genutzt, wenn die Kommunikation unidirektional verläuft und keine Möglichkeit besteht, dass eine I²C-Komponente gleichzeitig kommuniziert.

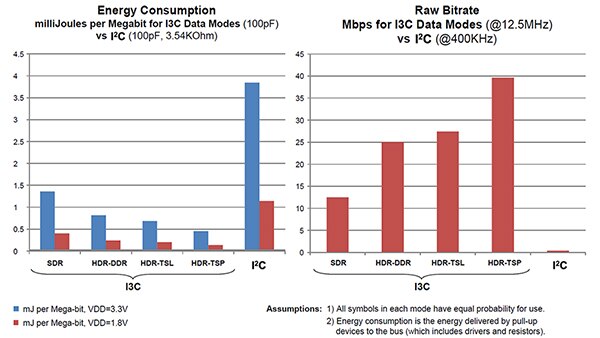

Neben dem standardmäßigen SDR-Modus unterstützt I3C mehrere optionale Modi mit hoher Datenrate (high data rate, HDR). Diese HDR-Modi nutzten dieselbe Taktrate, übertragen aber mit einer höheren Datendichte. Der erste HDR-Modi ist der HDR-DDR (HDR Double Data Rate), bei dem die Daten an beiden Flanken des Taktsignals getaktet werden, wodurch sich die Datenrate fast verdoppelt. Bei einem Takt von 12,5 MHz wird im DDR-Modus eine effektive Datenrate von 20 Mbits/s erreicht.

Es gibt zwei Arten von ternären HDR-Symbolen: HDR ternary symbol, pure (HDR-TSP), für Busse, die ausschließlich I3C-Komponenten umfassen, und HDR ternary symbol, legacy (HDR-TSL) für Busse, die sowohl I²C- als auch I3C-Komponenten enthalten. Die Modi mit ternären Symbolen unterstützen drei Datenbits pro Takt bei Dreibit-Symbolen (ternär), die auf den SCL- und SDA-Leitungen verschlüsselt werden.

Der HDR-BT-Modus (HDR bulk transport - HDR-Massendatenübertragung) bietet die höchste Datenrate, da er Kommunikation über vier, zwei oder eine SDA-Datenleitung unterstützt. Dadurch wird eine Veracht-, Vervier- bzw. Verzweifachung der einfachen Datenrate bei gleicher Taktrate erreicht.

Diese Erhöhung der Datenübertragungsgeschwindigkeit ermöglicht es, Komponenten für einen kürzeren Zeitraum einzuschalten und so den Arbeitszyklus des Busses zu reduzieren. Das reduziert den Stromverbrauch im Vergleich zu I²C (Abbildung 3). Durch den Wechsel von Open-Collector-Treibern mit externen Pull-up-Widerständen zu Push-Pull-Treibern wird der benötigte Strom weiter gesenkt, da die Pull-up-Widerstände einen erheblichen Strombedarf haben.

Abbildung 3: I3C bietet Verbesserungen bei Datenrate und Stromverbrauchs im Vergleich zu I²C. (Bildquelle: NXP Semiconductors)

Abbildung 3: I3C bietet Verbesserungen bei Datenrate und Stromverbrauchs im Vergleich zu I²C. (Bildquelle: NXP Semiconductors)

Adressierung

I²C nutzt statische Adressen mit einer Länge von 7 oder 10 Bit für jede Komponente des Busses. Das wurde bei I3C auf eine dynamische 7-Bit-Adressierung umgestellt, bei der die Haupteinheit eines Busses die Komponentenadresse während der dynamischen Adresszuweisung (dynamic address assignment, DAA) festlegt und in einem Komponentenregister speichert. Die statische Adressierung, wie bei einer I²C-Peripheriekomponente, kann bei I3C weiterhin verwendet werden.

Aufgrund der dynamischen Adressierung lassen sich die Adressen der Komponenten später ändern. Dadurch wird Hot Joining unterstützt, was heißt, dass eine neue Komponente im laufenden Betrieb mit dem Bus verbunden werden kann. Die neue Komponente signalisiert der I3C-Haupteinheit bei der Verbindung mit dem I3C-Bus ihre Anwesenheit, indem sie eine Hot-Join-Anfrage sendet. Die Haupteinheit bestätigt die Anfrage und weist eine Adresse zu, um die Komponente in den Bus aufzunehmen.

IBIs

I3C ist ein echter Zweidraht-Bus, der IBIs anstelle von dedizierten Interrupt-Leitungen wie bei I²C verwendet. IBIs liegen vor, wenn eine Komponente der Haupteinheit ihre Verfügbarkeit signalisiert, indem sie die SDA-Leitung auf „Low“ setzt (Pull-Down). Die Haupteinheit startet dann den Takt auf der SCL-Leitung, und die Zielkomponente überträgt ihre Adresse auf dem I3C-Bus, um der Haupteinheit einen Interrupt zu melden.

Einheitliche Befehlscodes

Einheitliche Befehlscodes (Common Command Codes, CCC) sind standardisierte Befehle, die die Haupteinheit als allgemeine Mitteilung an alle I3C-Komponenten gleichzeitig oder an eine bestimmte Zielkomponente senden kann. Diese Befehle beziehen sich auf das Busmanagement. Das Format des CCC-Protokolls beginnt mit der I3C-Broadcast-Adresse, die von allen I3C-Komponenten im Bus erkannt wird. Mögliche I²C-Komponenten im Bus bestätigen die Anfrage nicht, da diese reservierte I²C-Adressen besitzen.

Jeder Befehl enthält ein 8-Bit-Deskriptor-ID-Feld, dem der eigentliche Befehl folgen kann. Ein Befehl, der an eine bestimmte Komponente gesendet wird, übermittelt die Komponentenadresse im ersten Byte des eigentlichen Befehls. Es gibt über vierzig CCC-Befehle, darunter:

- Enter Dynamic Address Assignment (ENTDAA) (dynamische Adresszuweisung starten)

- Set New Dynamic Address (SETNEWDA) (neue dynamische Adresse zuweisen)

- Enable Events (ENEC)/Disable Events (DISEC) (Ereignisse (de-)aktivieren)

- Reset Dynamic Address Assignment (RSTDAA) (dynamische Adresszuweisung zurücksetzen)

- Enter High Data Rate Mode (ENTHDRx) (HDR-Modus starten)

- Get Device Characteristics Register (GETDCR) (Register mit Komponenteneigenschaften abrufen)

Herstellern wird ein bestimmter Bereich von CCC-IDs zugestanden, um eigene Befehle zu implementieren.

Fehlererkennung und Wiederherstellung

Im Gegensatz zu I²C bietet I3C Maßnahmen zur Fehlererkennung und anschließenden Wiederherstellung der Funktion. Sechs Verfahren zur Fehlererkennung und Wiederherstellung für Zielkomponenten sind vorgeschrieben, eine weitere ist optional. Zusätzliche Verfahren zur Fehlererkennung und Wiederherstellung sind auch speziell für Fehler seitens der Haupteinheit verfügbar.

Komponenten eines I3C-Busses

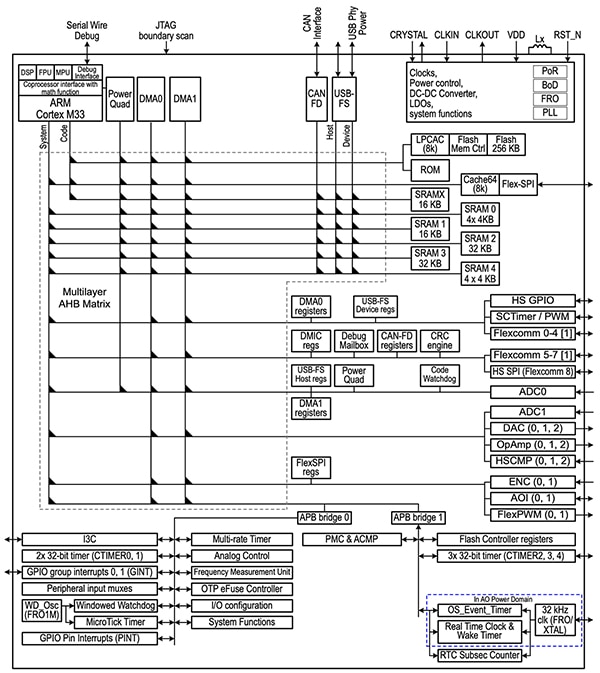

Wie in Abbildung 2 (links) dargestellt, umfasst ein einfaches I3C-Netzwerk mindestens eine Haupteinheit (Controller) und ein oder mehrere I3C-Zielkomponenten oder untergeordnete Einheiten. Die Haupteinheit kann ein Mikrocontroller sein, wie z. B. der LPC5534JHI48-00MP von NXP Semiconductors (Abbildung 4). Dabei handelt sich um einen 32-Bit Arm® Cortex®-M33 mit 128 Kilobytes (KByte) SRAM und 256 KBytes Flash. Seine Flexcomm-Schnittstelle unterstützt acht verschiedene serielle Schnittstellen, einschließlich I3C.

Abbildung 4: Der Mikrocontroller LPC5534JHI48/00MP verfügt über eine I3C-Schnittstelle sowie sieben weitere serielle Schnittstellen. (Bildquelle: NXP Semiconductor)

Abbildung 4: Der Mikrocontroller LPC5534JHI48/00MP verfügt über eine I3C-Schnittstelle sowie sieben weitere serielle Schnittstellen. (Bildquelle: NXP Semiconductor)

Der I3C-Bus erlaubt das Hinzufügen von sekundären Haupteinheiten, die als untergeordnete Einheiten mit dem Bus verbunden werden. I3C unterstützt mehrere Haupteinheiten, von denen jedoch nur eine der Controller sein kann. Nach der Registrierung kann die sekundäre Haupteinheit eine Anfrage zur Übertragung des Controller-Status stellen, und wenn der aktuelle Controller zustimmt, wird die Kontrolle an die anfragende sekundäre Haupteinheit übergeben.

Ein typischer I3C-Sensor ist der P3T2030CUKAZ von NXP. Dieser Temperatursensor wandelt Temperaturen von -40 °C bis +125 °C mit einer Genauigkeit von ±2 °C in einen digitalen 12-Bit-Wert um. Er verfügt sowohl über eine serielle I²C-Schnittstelle als auch eine I3C-SDR-Schnittstelle.

Etwas komplexerer ist der dreiachsige MEMS-Sensor (MEMS: mikroelektromechanisches System) ICM-42605 von TDK InvenSense aus Gyroskop und Beschleunigungsmesser. Als Wendekreisel misst er Drehraten von ±15,2 bis ±2000 Grad pro Sekunde (°/s). Sein Beschleunigungsmessbereich beträgt ±2 bis ±15 g. Er erfasst Bewegungen, Neigung, Antippen oder Schritte (Schrittzähler). Als I3C-Sensor erlaubt er den Betrieb mit 12,5 MHz im SDR-Modus und 25 MHz im DDR-Modus.

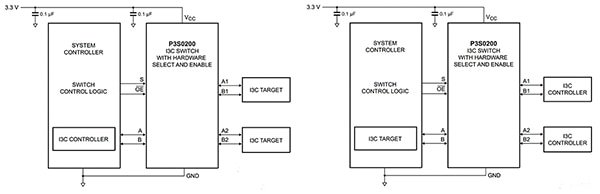

ICs wie der I3C-Switch P3S0200GMX von NXP können die Konfiguration eines I3C-Busses ändern, indem sie nach Vorgabe durch einen externen Mikrocontroller I3C-Bussignale zwischen einem I3C-Controller und mehreren Gruppen von Zielkomponenten oder zwischen einer einzelnen Zielkomponente und mehreren I3C-Controllern übermitteln (Abbildung 5).

Abbildung 5: Der I3C-Switch P3S0200GMX erlaubt die Neukonfiguration eines I3C-Busses, indem I3C-Bussignale zwischen einem I3C-Controller und mehreren Gruppen von Zielkomponenten oder zwischen einer einzelnen Zielkomponente und mehreren I3C-Controllern übermittelt werden. (Bildquelle: NXP Semiconductors)

Abbildung 5: Der I3C-Switch P3S0200GMX erlaubt die Neukonfiguration eines I3C-Busses, indem I3C-Bussignale zwischen einem I3C-Controller und mehreren Gruppen von Zielkomponenten oder zwischen einer einzelnen Zielkomponente und mehreren I3C-Controllern übermittelt werden. (Bildquelle: NXP Semiconductors)

Ein Wechsel zwischen zwei Zielkomponenten ist unter Umständen erforderlich, wenn beide die gleiche Adresse besitzen und nicht zum selben Bus gehören können. Alternativ müssen sich zwei Prozesse möglicherweise eine Zielkomponente teilen, was einen Wechsel zwischen den beiden I3C-Controllern erfordert.

Fazit

I3C ist eine serielle Schnittstelle, die den I²C-Bus weiter entwickelt, indem sie dessen Datenrate erhöht, die Anzahl der Drähte reduziert und die Bussteuerung flexibler macht. Es handelt sich um eine verbesserte Variante, die eine höhere Leistung als die älteren I²C- und SPI-Schnittstellen bietet.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.