Die Co-Prozessor-Architektur: Eine eingebettete Systemarchitektur für Rapid Prototyping

2021-07-06

Anmerkung der Redaktion - Obwohl die Co-Prozessor-Architektur haupsächlich für ihre digitale Verarbeitungsleistung und ihren Durchsatz bekannt ist, bietet sie dem Entwickler von Embedded-Systemen auch die Möglichkeit, Projektmanagement-Strategien zu implementieren, die sowohl die Entwicklungskosten als auch die Markteinführungszeit verbessern. Dieser Artikel konzentriert sich speziell auf die Kombination aus einem diskreten Mikrocontroller (MCU) und einem diskreten FPGA (Field Programmable Gate Array) und zeigt, wie sich diese Architektur für einen effizienten und iterativen Designprozess eignet. Anhand von recherchierten Quellen, empirischen Erkenntnissen und Fallstudien werden die Vorteile dieser Architektur aufgezeigt und beispielhafte Anwendungen vorgestellt. Am Ende dieses Artikels wird der Entwickler eingebetteter Systeme ein besseres Verständnis dafür haben, wann und wie diese vielseitige Hardware-Architektur implementiert werden sollte

Einführung

Der Entwickler von eingebetteten Systemen befindet sich in einem Dilemma aus Designeinschränkungen, Leistungserwartungen sowie Zeit- und Budgetvorgaben. In der Tat unterstreichen sogar die Widersprüche in modernen Projektmanagement-Schlagwörtern und Phrasen die prekäre Natur dieser Rolle: „zügig scheitern“, „flexibel sein“, „zukunftssicher machen“ und „umwälzend sein“. Die Akrobatik, die damit verbunden ist, überhaupt zu versuchen, diese Erwartungen zu erfüllen, kann erschütternd sein, und doch wurden und werden sie im Markt immer wieder bekräftigt. Benötigt wird ein Design-Ansatz, der einen evolutionären, iterativen Prozess ermöglicht, der wie bei den meisten Embedded-Systemen mit der Hardware-Architektur beginnt.

Die Co-Prozessor-Architektur, eine Hardware-Architektur, die dafür bekannt ist, dass sie die Stärken sowohl der Microcontroller (MCU) als auch der FPGAs (Field Programmable Gate Array) kombiniert, kann dem Embedded-Designer einen Prozess bieten, der selbst die anspruchsvollsten Anforderungen erfüllt und dennoch die notwendige Flexibilität bietet, um sowohl bekannte als auch unbekannte Herausforderungen zu meistern. Durch die Bereitstellung von Hardware, die in der Lage ist, sich iterativ anzupassen, kann der Entwickler Fortschritte demonstrieren, kritische Meilensteine erreichen und die Vorteile des Rapid-Prototyping-Prozesses voll ausschöpfen.

Innerhalb dieses Prozesses gibt es wichtige Projektmeilensteine, von denen jeder seinen eigenen, einzigartigen Wert für die Entwicklung hat. Im Verlauf dieses Artikels werden diese Meilensteine mit den folgenden Begriffen bezeichnet: „Digitale Signalverarbeitung mit dem Mikrocontroller“, „Systemmanagement mit dem Mikrocontroller“ und „Produktbereitstellung“.

Am Ende dieses Artikels soll gezeigt werden, dass eine flexible Hardware-Architektur für das Design moderner eingebetteter Systeme besser geeignet sein kann als ein starrer Ansatz. Darüber hinaus kann dieser Ansatz zu Verbesserungen sowohl bei den Projektkosten als auch bei der Markteinführungszeit führen. Zur Verteidigung dieser Position werden Argumente, angeführte Beispiele und Fallstudien verwendet. Betrachtet man den Wert der einzelnen Meilensteine innerhalb der Designflexibilität, die diese Architektur bietet, wird deutlich, dass eine adaptive Hardware-Architektur das Design von Embedded-Systemen stark vorantreibt.

Die Stärken der Co-Prozessor-Architektur ausloten: Design-Flexibilität und leistungsstarke Verarbeitung

Eine häufige Anwendung für FPGA-Designs ist die direkte Verbindung mit einem Highspeed-Analog/Digital-Wandler (ADC). Das Signal wird digitalisiert, in den FPGA eingelesen und dann werden einige Algorithmen des digitalen Signalprozessors (DSP) auf dieses Signal angewendet. Als letztes trifft der FPGA dann Entscheidungen auf Basis der Erkenntnisse.

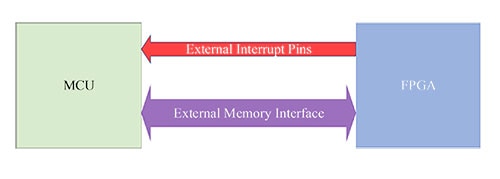

Eine solche Anwendung wird in diesem Artikel als Beispiel dienen. Darüber hinaus zeigt Abbildung 1 eine generische Co-Prozessor-Architektur, bei der die MCU und das FPGA über die externe Speicherschnittstelle der MCU verbunden sind. Das FPGA wird so behandelt, als wäre es ein Stück externer statischer Direktzugriffsspeicher (SRAM). Signale kommen vom FPGA zurück zur MCU und dienen als Hardware-Interruptleitungen und Statusanzeigen. Dies ermöglicht dem FPGA, der MCU kritische Zustände anzuzeigen, z. B. die Mitteilung, dass eine ADC-Wandlung bereit ist, ein Fehler aufgetreten ist oder ein anderes bemerkenswertes Ereignis stattgefunden hat.

Abbildung 1: Generisches Co-Prozessor-Diagramm (MCU + FPGA). (Bildquelle: CEPD)

Abbildung 1: Generisches Co-Prozessor-Diagramm (MCU + FPGA). (Bildquelle: CEPD)

Die Stärken des Co-Prozessor-Ansatzes lassen sich wahrscheinlich am besten an den Ergebnissen der einzelnen oben genannten Meilensteine erkennen. Der Wert wird nicht nur durch die Auflistung der Leistungen einer Aufgabe oder Phase bewertet, sondern auch durch die Bewertung der Befähigung, die diese Leistungen ermöglichen. Die Antworten auf die folgenden Fragen helfen dabei, den Gesamtwert der Ergebnisse eines Meilensteins zu beurteilen:

- Können die Fortschritte der anderen Teammitglieder nun schneller fortgesetzt werden, da Projektabhängigkeiten und Engpässe beseitigt werden?

- Wie ermöglichen die Errungenschaften des Meilensteins weitere parallele Ausführungswege?

Der Meilenstein der digitalen Signalverarbeitung mit dem Mikrocontroller

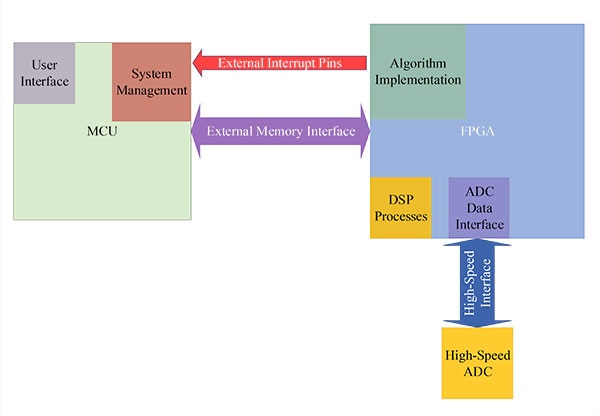

Abbildung 2: Architektur zur digitalen Signalverarbeitung mit dem Mikrocontroller. (Bildquelle: CEPD)

Abbildung 2: Architektur zur digitalen Signalverarbeitung mit dem Mikrocontroller. (Bildquelle: CEPD)

Die erste Entwicklungsstufe, die diese Hardware-Architektur ermöglicht, stellt die MCU in den Mittelpunkt. Alles in allem ist die Entwicklung von MCUs und ausführbarer Software weniger ressourcen- und zeitaufwändig als die Entwicklung von FPGAs und einer Hardware-Beschreibungssprache (HDL, Hardware Descriptive Language). Indem die Produktentwicklung mit der MCU als primärem Prozessor begonnen wird, können Algorithmen schneller implementiert, getestet und validiert werden. Auf diese Weise können algorithmische und logische Fehler bereits in einem frühen Stadium des Entwurfsprozesses entdeckt werden, wodurch auch wesentliche Teile der Signalkette getestet und validiert werden können.

Die Rolle des FPGAs in diesem ersten Meilenstein ist es, als Highspeed-Schnittstelle zur Datenerfassung zu dienen. Seine Aufgabe ist es, Daten zuverlässig vom Highspeed-ADC aufzunehmen, der MCU mitzuteilen, dass Daten verfügbar sind, und diese Daten auf der externen Speicherschnittstelle der MCU zu präsentieren. Obwohl diese Rolle nicht die Implementierung von HDL-basierten DSP-Prozessen oder anderen Algorithmen beinhaltet, ist sie dennoch sehr wichtig.

Die in dieser Phase durchgeführte FPGA-Entwicklung legt den Grundstein für den letztendlichen Erfolg des Produkts sowohl innerhalb der Produktentwicklung als auch bei der Markteinführung. Indem man sich nur auf die Low-Level-Schnittstelle konzentriert, kann ausreichend Zeit für das Testen dieser wesentlichen Operationen verwendet werden. Erst wenn das FPGA diese Schnittstellenfunktion zuverlässig und souverän erfüllt, kann dieser Meilenstein sicher abgeschlossen werden.

Zu den wichtigsten Ergebnissen dieses ersten Meilensteins gehören die folgenden Vorteile:

- Der gesamte Signalpfad - alle Verstärkungen, Abschwächungen und Umwandlungen - wird getestet und validiert sein.

- Die Projektentwicklungszeit und der Aufwand werden durch die anfängliche Implementierung der Algorithmen in Software (C/C++) reduziert worden sein; dies ist von erheblichem Wert für das Management und andere Beteiligte, die die Durchführbarkeit dieses Projekts sehen müssen, bevor sie zukünftige Designphasen genehmigen.

- Die Erkenntnisse aus der Implementierung der Algorithmen in C/C++ werden direkt auf HDL-Implementierungen übertragbar sein - durch den Einsatz von Software-zu-HDL-Tools, z.B. Xilinx HLS.

Der Meilenstein der Systemverwaltung mit dem Mikrocontroller

Abbildung 3: Architektur - Systemverwaltung mit dem Mikrocontroller. (Bildquelle: CEPD)

Abbildung 3: Architektur - Systemverwaltung mit dem Mikrocontroller. (Bildquelle: CEPD)

Die zweite Entwicklungsstufe, die dieser Co-Prozessor-Ansatz bietet, ist durch die Verlagerung von DSP-Prozessen und Algorithmus-Implementierungen von der MCU auf das FPGA definiert. Der FPGA ist immer noch für die Highspeed-ADC-Schnittstelle verantwortlich, aber durch die Übernahme dieser anderen Aufgaben werden die Geschwindigkeit und Parallelität, die der FPGA bietet, voll ausgenutzt. Darüber hinaus können im Gegensatz zur MCU mehrere Instanzen der DSP-Prozesse und Algorithmenkanäle implementiert werden, die gleichzeitig laufen.

Aufbauend auf den Lehren, die aus der Implementierung der MCU gezogen wurden, trägt der Entwickler diese Zuversicht in diesen nächsten Meilenstein. Tools, wie das bereits erwähnte Vivado HLS von Xilinx, bieten eine funktionale Übersetzung vom ausführbaren C/C++-Code in synthetisierbares HDL. Nun müssen noch Timing-Constraints, Prozessparameter und andere Benutzerpräferenzen definiert und implementiert werden, die Kernfunktionalität wird jedoch beibehalten und in die FPGA-Struktur übersetzt.

Für diesen Meilenstein hat die MCU die Rolle eines Systemmanagers. Status- und Steuerregister innerhalb des FPGAs werden von der MCU überwacht, aktualisiert und gemeldet. Außerdem verwaltet die MCU die Benutzeroberfläche (UI). Diese Benutzeroberfläche könnte die Form eines Webservers annehmen, auf den über eine Ethernet- oder Wi-Fi-Verbindung zugegriffen wird, oder sie könnte eine industrielle Touchscreen-Benutzeroberfläche sein, die den Benutzern den Zugriff am Ort der Nutzung ermöglicht. Die wichtigste Erkenntnis aus der neuen, verfeinerten Rolle der MCU ist folgende: Durch die Entlastung von rechenintensiven Verarbeitungsaufgaben werden sowohl die MCU als auch das FPGA jetzt für Aufgaben eingesetzt, für die sie gut geeignet sind.

Zu den wichtigsten Ergebnissen dieses Meilensteins gehören diese Vorteile:

- Die schnelle, parallele Ausführung von DSP-Prozessen und Algorithmus-Implementierungen wird durch das FPGA ermöglicht.Die MCU bietet eine reaktionsschnelle und optimierte Benutzeroberfläche und verwaltet die Prozesse des Produkts.

- Nachdem sie zunächst innerhalb der MCU entwickelt und validiert wurden, sind die algorithmischen Risiken gemildert worden und diese Minderung wird in synthetisierbares HDL übertragen. Tools, wie Vivado HLS, erleichtern diese Übersetzung. Darüber hinaus können FPGA-spezifische Risiken durch integrierte Simulationswerkzeuge, wie z. B. die Vivado Design Suite, gemindert werden.

- Die Beteiligten werden durch die Verlagerung der Prozesse auf das FPGA keinem nennenswerten Risiko ausgesetzt. Im Gegenteil, sie bekommen die Vorteile zu sehen und zu genießen, die die Geschwindigkeit und Parallelität des FPGAs bieten. Es werden messbare Leistungsverbesserungen beobachtet und der Fokus kann nun auf die Vorbereitung dieses Designs für die Fertigung gelegt werden.

Der Meilenstein der Produktbereitstellung

Da die rechenintensive Verarbeitung innerhalb des FPGAs stattfindet und die MCU die Aufgaben der Systemverwaltung und der Benutzeroberfläche übernimmt, ist das Produkt einsatzbereit. Dieses Papier plädiert natürlich nicht dafür, Alpha- und Beta-Releases zu umgehen; der Schwerpunkt für diesen Meilenstein liegt jedoch auf den Fähigkeiten, die die Co-Prozessor-Architektur für die Produktbereitstellung bietet.

Sowohl die MCU als auch das FPGA sind feldaktualisierbare Geräte. Es wurden mehrere Fortschritte gemacht, um FPGA-Updates genauso zugänglich zu machen wie Software-Updates. Da sich das FPGA im adressierbaren Speicherbereich der MCU befindet, kann die MCU zudem als Zugriffspunkt für das gesamte System dienen: Sie erhält sowohl Updates für sich selbst als auch für das FPGA. Updates können basierend auf bestimmten Bedingungen geplant, verteilt und pro Endbenutzer angepasst werden. Schließlich können Benutzer- und Use-Case-Protokolle geführt und mit bestimmten Build-Implementierungen verknüpft werden. Anhand dieser Datensätze kann die Leistung auch dann noch verfeinert und verbessert werden, wenn das Produkt bereits im Einsatz ist.

Vielleicht werden die Stärken dieser Aktualisierbarkeit des Gesamtsystems nirgends mehr unterstrichen als in weltraumgestützten Anwendungen. Sobald ein Produkt auf den Markt kommt, müssen Wartung und Updates aus der Ferne durchgeführt werden. Dies kann so einfach sein wie das Ändern logischer Bedingungen oder so kompliziert wie das Aktualisieren eines Kommunikationsmodulationsschemas. Die Programmierbarkeit, die FPGA-Technologien und die Co-Prozessor-Architektur bieten, können die gesamte Bandbreite dieser Fähigkeiten abdecken und bieten gleichzeitig eine Auswahl an strahlungsgeschützten Komponenten.

Die letzte wichtige Erkenntnis aus diesem Meilenstein ist die progressive Kostenreduzierung. Kostensenkungen, Stücklistenänderungen und andere Optimierungen können ebenfalls an diesem Meilenstein erfolgen. Während des Einsatzes im Feld kann sich herausstellen, dass das Produkt mit einer weniger teuren MCU oder einem weniger leistungsfähigen FPGA genauso gut funktioniert. Durch den Co-Prozessor sind Architekturdesigner nicht darauf angewiesen, Komponenten zu verwenden, deren Fähigkeiten die Anforderungen ihrer Anwendung übersteigen. Sollte darüber hinaus eine Komponente nicht mehr verfügbar sein, erlaubt die Architektur, neue Komponenten in das Design zu integrieren. Dies ist nicht der Fall bei einer Einzelchip- oder System-on-Chip(SoC)-Architektur oder bei einem Hochleistungs-DSP oder einer MCU, die versuchen, die gesamte Verarbeitung des Produkts zu übernehmen. Die Co-Prozessor-Architektur ist eine gute Mischung aus Leistungsfähigkeit und Flexibilität, die dem Entwickler sowohl in der Entwicklungsphase als auch bei der Markteinführung mehr Wahlmöglichkeiten und Freiheiten bietet.

Unterstützende Forschung und verwandte Fallstudien

Beispiel der Satellitenkommunikation

Kurz gesagt, der Wert eines Co-Prozessors besteht darin, die primäre Verarbeitungseinheit zu entlasten, so dass Aufgaben auf der Hardware ausgeführt werden, bei denen Beschleunigungen und Rationalisierungen genutzt werden können. Der Vorteil einer solchen Designwahl ist ein Nettozuwachs an Rechengeschwindigkeit und -fähigkeiten und, wie dieser Artikel argumentiert, eine Reduzierung der Entwicklungskosten und -zeit. Vielleicht ist einer der überzeugendsten Bereiche für diese Vorteile im Bereich der Weltraumkommunikationssysteme.

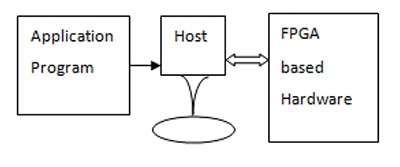

In ihrer Veröffentlichung FPGA-basierte Hardware als Coprozessor beschreiben G. Prasad und N. Vasantha, wie die Datenverarbeitung innerhalb eines FPGAs die Rechenanforderungen von Satellitenkommunikationssystemen erfüllt, ohne die hohen einmaligen Entwicklungskosten (NRE) von anwendungsspezifischen integrierten Schaltungen (ASICs) oder die anwendungsspezifischen Einschränkungen eines Prozessors mit harter Architektur. Wie im Meilenstein „Digitale Signalverarbeitung mit dem Mikrocontroller“ beschrieben, beginnt ihr Design damit, dass der Anwendungsprozessor einen Großteil der rechenintensiven Algorithmen ausführt. Von diesem Ausgangspunkt aus identifizieren sie die wichtigsten Abschnitte der Software, die einen Großteil der Taktzyklen der Zentraleinheit (CPU) verbrauchen, und migrieren diese Abschnitte in die HDL-Implementierung. Die grafische Darstellung ist den bisher vorgestellten sehr ähnlich, allerdings haben sie sich dafür entschieden, das Anwendungsprogramm als eigenständigen Block darzustellen, da es entweder im Host (Prozessor) oder in der FPGA-basierten Hardware realisiert werden kann.

Abbildung 4: Anwendungsprogramm, Host-Prozessor und FPGA-basierte Hardware - verwendet im Beispiel der Satellitenkommunikation.

Abbildung 4: Anwendungsprogramm, Host-Prozessor und FPGA-basierte Hardware - verwendet im Beispiel der Satellitenkommunikation.

Durch die Verwendung einer PCI-Schnittstelle (Peripheral Component Interconnect) und des direkten Speicherzugriffs (DMA) des Host-Prozessors wird die Leistung der Peripherie drastisch erhöht. Dies wird vor allem bei den Verbesserungen für den Prozess der Derandomisierung beobachtet. Als dieser Prozess in der Software des Host-Prozessors durchgeführt wurde, gab es eindeutig einen Engpass im Echtzeitverhalten des Systems. Bei der Verlagerung auf das FPGA wurden jedoch die folgenden Vorteile beobachtet:

- Der Prozess der Derandomisierung wurde in Echtzeit ausgeführt, ohne Engpässe zu verursachen

- Der Rechenaufwand des Host-Prozessors wurde deutlich reduziert, und er konnte nun die gewünschte Protokollierungsfunktion besser erfüllen.

- Die Gesamtleistung des Gesamtsystems wurde hochskaliert.

All dies wurde ohne die mit einem ASIC verbundenen Kosten und unter Nutzung der Flexibilität der programmierbaren Logik erreicht [5]. Die Satellitenkommunikation stellt beträchtliche Herausforderungen dar. Mit diesem Ansatz können diese Anforderungen nachweislich erfüllt werden, wobei die Flexibilität des Designs erhalten bleibt.

Automobiltechnik - Infotainment-Beispiel

Unterhaltungssysteme im Auto sind ein Alleinstellungsmerkmal für den anspruchsvollen Verbraucher. Im Gegensatz zu einem Großteil der Automobilelektronik sind diese Geräte gut sichtbar und es wird erwartet, dass sie eine außergewöhnliche Reaktionszeit und Leistung bieten. Entwickler stehen jedoch oft in der Zwickmühle zwischen den aktuellen Anforderungen an das Design und der Flexibilität, die zukünftige Funktionen erfordern werden. Für dieses Beispiel werden die Implementierungsanforderungen der Signalverarbeitung und der drahtlosen Kommunikation genutzt, um die Stärken der Co-Prozessor-Hardware-Architektur hervorzuheben.

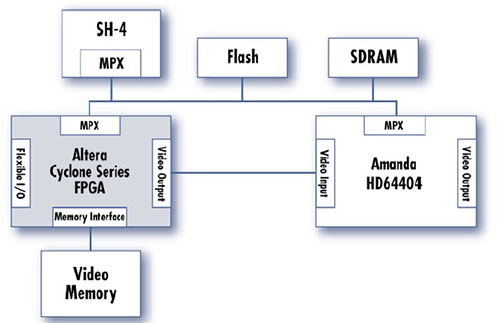

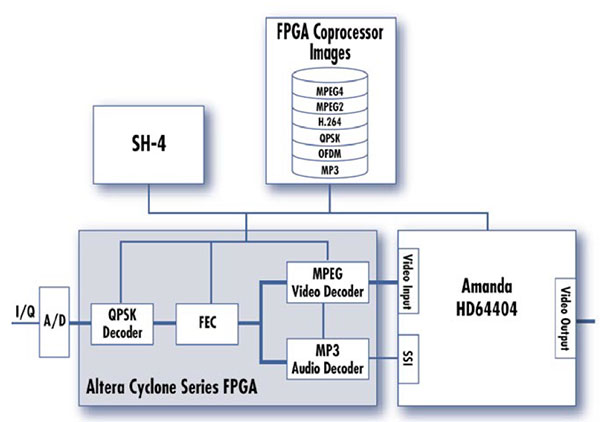

Eine der vorherrschenden Architekturen von Unterhaltungssystemen in Fahrzeugen wurde von der Firma Delphi Delco Electronics Systems veröffentlicht. Diese Architektur verwendet die MCU SH-4 mit einem dazugehörigen ASIC, der Peripheriekomponente HD64404 Amanda von Hitachi. Diese Architektur erfüllte mehr als 75 % der grundlegenden Unterhaltungsfunktionen des Automobilmarktes; allerdings fehlte ihr die Fähigkeit, Videoverarbeitungsanwendungen und drahtlose Kommunikation zu adressieren. Durch die Einbindung eines FPGAs in diese bestehende Architektur kann dieser bereits existierende Designansatz um weitere Flexibilität und Fähigkeiten erweitert werden.

Abbildung 5: Infotainment-FPGA-Coprozessor-Architektur, Beispiel 1.

Abbildung 5: Infotainment-FPGA-Coprozessor-Architektur, Beispiel 1.

Die Architektur in Abbildung 5 ist sowohl für die Videoverarbeitung als auch für die Verwaltung der drahtlosen Kommunikation geeignet. Durch die Verlagerung der DSP-Funktionalitäten in den FPGA kann der Amanda-Prozessor eine Systemmanagement-Rolle übernehmen und ist frei für die Implementierung eines drahtlosen Kommunikationsstacks. Da sowohl der Amanda als auch der FPGA Zugriff auf den externen Speicher haben, können Daten schnell zwischen den Prozessoren und Komponenten des Systems ausgetauscht werden.

Abbildung 6: Infotainment-FPGA-Coprozessor-Architektur, Beispiel 2.

Abbildung 6: Infotainment-FPGA-Coprozessor-Architektur, Beispiel 2.

Das zweite Infotainment in Abbildung 6 verdeutlicht die Fähigkeit des FPGAs, sowohl die eingehenden analogen Hochgeschwindigkeitsdaten als auch die Handhabung der für Videoanwendungen erforderlichen Komprimierung und Codierung zu bewältigen. Tatsächlich können alle diese Funktionen in den FPGA gepusht werden und durch den Einsatz von Parallelverarbeitung können sie alle in Echtzeit angesprochen werden.

Durch die Einbindung eines FPGAs in eine bestehende Hardware-Architektur kann die bewährte Leistung der vorhandenen Hardware mit Flexibilität und Zukunftssicherheit verbunden werden. Auch innerhalb bestehender Systeme bietet die Co-Prozessor-Architektur dem Entwickler Optionen, die sonst nicht zur Verfügung stehen [6].

Vorteile des Rapid Prototyping

Im Kern zielt der Rapid-Prototyping-Prozess darauf ab, einen beträchtlichen Teil des Produktentwicklungsbereichs abzudecken, indem Aufgaben parallel ausgeführt werden, „Bugs“ und Designprobleme schnell identifiziert werden und Daten- und Signalpfade validiert werden, insbesondere diejenigen innerhalb des kritischen Pfads eines Projekts. Damit dieser Prozess jedoch wirklich zu schlanken, effizienten Ergebnissen führt, muss ausreichend Fachwissen in den erforderlichen Projektbereichen vorhanden sein.

Traditionell bedeutet dies, dass es einen Hardware-Ingenieur, einen Embedded-Software- oder DSP-Ingenieur und einen HDL-Ingenieur geben muss. Nun gibt es viele interdisziplinäre Fachleute, die möglicherweise mehrere Rollen erfüllen können; allerdings ist die Koordinierung dieser Bemühungen immer noch mit einem erheblichen Projektaufwand verbunden.

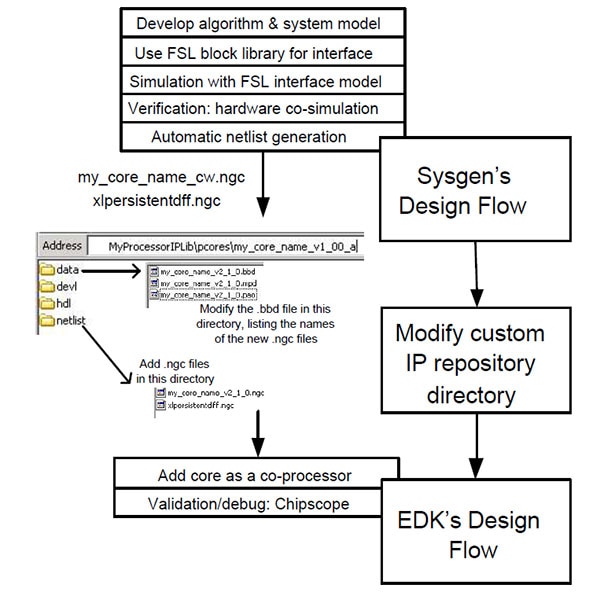

In ihrem Beitrag „An FPGA based rapid prototyping platform for wavelet coprocessors“ (Eine FPGA-basierte Rapid-Prototyping-Plattform für Wavelet-Coprozessoren) propagieren die Autoren die Idee, dass die Verwendung einer Co-Prozessor-Architektur es einem einzelnen DSP-Ingenieur ermöglicht, all diese Rollen effizient und effektiv zu erfüllen. Für diese Studie begann das Team mit dem Entwurf und der Simulation der gewünschten DSP-Funktionalität innerhalb des MATLAB-Tools Simulink. Dies diente zwei Hauptfunktionen, indem es 1) die gewünschte Leistung durch Simulation verifizierte und 2) als Basis diente, mit der zukünftige Designentscheidungen verglichen und referenziert werden konnten.

Nach der Simulation wurden kritische Funktionalitäten identifiziert und in verschiedene Kerne aufgeteilt - das sind Soft-Core-Komponenten und Prozessoren, die innerhalb eines FPGAs synthetisiert werden können. Der wichtigste Schritt während dieser Arbeit war es, die Schnittstelle zwischen diesen Kernen und Komponenten zu definieren und die Datenaustauschleistung mit der gewünschten, simulierten Leistung zu vergleichen. Dieser Entwurfsprozess lehnt sich eng an den Entwurfsablauf von Xilinx für eingebettete Systeme an und ist in Abbildung 7 unten zusammengefasst.

Abbildung 7: Ablauf der Designimplementierung.

Abbildung 7: Ablauf der Designimplementierung.

Durch die Aufteilung des Systems in synthetisierbare Kerne kann sich der DSP-Ingenieur auf die kritischsten Aspekte der Signalverarbeitungskette konzentrieren. Sie/er muss kein Experte für Hardware oder HDL sein, um verschiedene Soft-Core-Prozessoren oder Komponenten innerhalb des FPGAs zu modifizieren, zu routen oder zu implementieren. Solange der Entwickler die Schnittstelle und die Formate der Daten kennt, hat er die volle Kontrolle über die Signalwege und kann die Leistung des Systems verfeinern.

Empirische Erkenntnisse - das Fallbeispiel der diskreten Kosinustransformation

Die empirischen Ergebnisse bestätigen nicht nur die Flexibilität, die die Co-Prozessor-Architektur dem Entwickler von eingebetteten Systemen bietet, sondern zeigen auch die leistungssteigernden Möglichkeiten, die mit modernen FPGA-Tools zur Verfügung stehen. Erweiterungen, wie die unten genannten, sind für andere Hardware-Architekturen möglicherweise nicht verfügbar oder haben weniger Auswirkungen. Als rechenintensiver Algorithmus wurde die diskrete Kosinustransformation (DCT) ausgewählt, deren Weiterentwicklung von einer C-basierten Implementierung zu einer HDL-basierten Implementierung im Mittelpunkt stand. DCT wurde gewählt, da dieser Algorithmus in der digitalen Signalverarbeitung zur Mustererkennung und Filterung verwendet wird [8]. Die empirischen Erkenntnisse basieren auf einer Laborübung, die vom Autor und Mitarbeitern durchgeführt wurde, um die Xilinx Alliance Partner Zertifizierung für 2020 bis 2021 zu erhalten.

Die folgenden Tools und Geräte wurden dabei verwendet:

- Vivado HLS v2019

- Die Komponente zur Bewertung und Simulation war das xczu7ev-ffvc1156-2-e

Beginnend mit der C-basierten Implementierung akzeptiert der DCT-Algorithmus zwei Arrays mit 16-Bit-Zahlen; Array „a“ ist das Eingangsarray für die DCT, und Array „b“ ist das Ausgangsarray der DCT. Die Datenbreite (DB) ist also mit 16 definiert, und die Anzahl der Elemente innerhalb der Arrays (N) ist 1024/DB, also 64. Als letztes wird die Größe der DCT-Matrix (DCT_SIZE) auf 8 gesetzt, d. h. es wird eine 8x8-Matrix verwendet.

Der Prämisse dieses Artikels folgend, ermöglicht die C-basierte Algorithmus-Implementierung dem Entwickler eine schnelle Entwicklung und Validierung der Funktionalität des Algorithmus. Obwohl es eine wichtige Überlegung ist, wird bei dieser Validierung die Funktionalität höher gewichtet als die Ausführungszeit. Diese Gewichtung ist zulässig, da die endgültige Implementierung dieses Algorithmus in einem FPGA erfolgen wird, wo Hardware-Beschleunigung, Schleifenabrollung und andere Techniken leicht verfügbar sind.

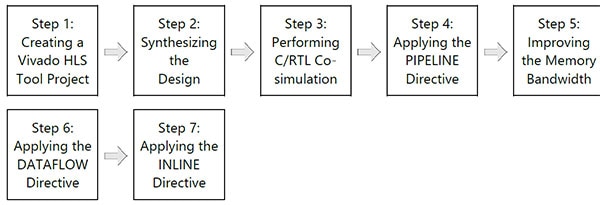

Abbildung 8: Vivado-HLS-Designfluss von Xilinx.

Abbildung 8: Vivado-HLS-Designfluss von Xilinx.

Nachdem der DCT-Code innerhalb des Tools Vivado HLS als Projekt erstellt wurde, kann im nächsten Schritt mit der Synthese des Designs für die FPGA-Implementierung begonnen werden. In diesem nächsten Schritt werden einige der wichtigsten Vorteile der Verlagerung der Ausführung eines Algorithmus von einer MCU zu einem FPGA deutlicher - als Referenz ist dieser Schritt äquivalent zu dem oben besprochenen Meilenstein „Systemverwaltung mit dem Mikrocontroller“.

Moderne FPGA-Tools ermöglichen eine Reihe von Optimierungen und Erweiterungen, die die Leistung komplexer Algorithmen erheblich steigern. Bevor Sie die Ergebnisse analysieren, sollten Sie einige wichtige Begriffe im Hinterkopf behalten:

- Latenz - Die Anzahl der Taktzyklen, die zur Ausführung aller Iterationen der Schleife benötigt werden [10]

- Intervall - Die Anzahl der Taktzyklen, bevor die nächste Iteration einer Schleife beginnt, Daten zu verarbeiten [11]

- BRAM - Block Random Access Memory (Block-Arbeitsspeicher)

- DSP48E - Digitale Signalverarbeitungsscheibe für die UltraScale-Architektur

- FF - Flipflop

- LUT - Lookup-Tabelle

- URAM - Unified Random-Access Memory (Einheitlicher Speicher mit wahlfreiem Zugriff, kann aus einem einzigen Transistor aufgebaut sein)

|

||||||||||||||||||||||||||||||||||||||||

Tabelle 1: Ergebnisse der Optimierung der FPGA-Algorithmusausführung (Latenz und Intervall).

|

Tabelle 2: Ergebnisse der Optimierung der FPGA-Algorithmusausführung (Ressourcenverwendung).

Standard

Die Standardeinstellung der Optimierung stammt aus dem unveränderten Ergebnis der Übersetzung des C-basierten Algorithmus in synthetisierbares HDL. Es sind keine Optimierungen aktiviert, und dies kann als Leistungsreferenz verwendet werden, um die anderen Optimierungen besser zu verstehen.

Pipeline-Innenschleife

Die PIPELINE-Direktive weist Vivado HLS an, die inneren Schleifen abzurollen, so dass neue Daten verarbeitet werden können, während sich die vorhandenen Daten noch in der Pipeline befinden. Neue Daten müssen also nicht warten, bis die vorhandenen Daten vollständig sind, bevor die Verarbeitung beginnen kann.

Pipeline-Außenschleife

Durch die Anwendung der PIPELINE-Direktive auf die äußere Schleife werden die Operationen der äußeren Schleife nun in die Pipeline geleitet. Allerdings laufen die Operationen der inneren Schleifen nun gleichzeitig ab. Durch die direkte Anwendung auf die äußere Schleife werden sowohl die Latenzzeit als auch die Intervallzeit halbiert.

Array-Partition

Diese Direktive bildet den Inhalt der Schleifen auf Arrays ab und verflacht damit alle Speicherzugriffe auf einzelne Elemente innerhalb dieser Arrays. Dadurch wird zwar mehr RAM verbraucht, aber auch hier halbiert sich die Ausführungszeit dieses Algorithmus.

Datenfluss

Mit dieser Direktive kann der Entwickler die Zielanzahl der Taktzyklen zwischen den einzelnen Eingangslesungen festlegen. Diese Direktive wird nur für die Top-Level-Funktion unterstützt. Nur Schleifen und Funktionen, die auf dieser Ebene exponiert sind, profitieren von dieser Richtlinie.

Inline

Die INLINE-Direktive flacht alle Schleifen ab, sowohl innere als auch äußere. Sowohl Zeilen- als auch Spaltenprozesse können jetzt gleichzeitig ausgeführt werden. Die Anzahl der benötigten Taktzyklen wird auf ein Minimum reduziert, auch wenn dadurch mehr FPGA-Ressourcen verbraucht werden.

Fazit

Die Co-Prozessor-Hardware-Architektur bietet dem Embedded-Designer eine Hochleistungsplattform, die ihre Design-Flexibilität während der gesamten Entwicklung und über die Produktfreigabe hinaus beibehält. Indem Algorithmen zunächst in C oder C++ validiert werden, können Prozesse, Daten- und Signalpfade sowie kritische Funktionen in relativ kurzer Zeit verifiziert werden. Durch die Übersetzung der prozessorintensiven Algorithmen in das Co-Prozessor-FPGA kann der Entwickler dann die Vorteile der Hardware-Beschleunigung und eines modulareren Designs nutzen.

Sollten Teile veraltet sein oder Optimierungen erforderlich sein, kann die gleiche Architektur diese Änderungen berücksichtigen. Neue MCUs und neue FPGAs können in das Design eingepasst werden, während die Schnittstellen relativ unangetastet bleiben können. Da sowohl die MCU als auch das FPGA im Feld aktualisierbar sind, können außerdem benutzerspezifische Änderungen und Optimierungen im Feld und aus der Ferne vorgenommen werden.

Zusammenfassend lässt sich sagen, dass diese Architektur die Entwicklungsgeschwindigkeit und Verfügbarkeit einer MCU mit der Leistung und Erweiterbarkeit eines FPGAs verbindet. Mit Optimierungen und Leistungsverbesserungen, die bei jedem Entwicklungsschritt zur Verfügung stehen, kann die Co-Prozessor-Architektur selbst die anspruchsvollsten Anforderungen erfüllen - sowohl für heutige Designs als auch darüber hinaus.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.