Die Grundlagen von Frequenzsynthesizern mit Phasenregelkreis

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2021-02-03

Steigende Datenraten in seriellen Highspeed-Kommunikationsbussen erfordern Systemtakte mit höheren Frequenzen, höherer Stabilität, größerer Frequenzauflösung und höherer Signalreinheit. Direkte digitale Synthesizer bieten diese Eigenschaften aber nur bei Frequenzen unter 2 oder 3 Gigahertz (GHz). Es werden aber Lösungen für Frequenzen bis zu einigen zehn Gigahertz benötigt.

Diese Lösung beginnt mit PLL-basierten (Phase Locked Loop) analogen Frequenzsynthesizern, die Taktfrequenzen bis zu 30 GHz erzeugen. Dann werden bei Integer-N-Synthesizern (die die Referenzfrequenz mit einem ganzzahligen Wert multiplizieren) und bei Fraktionalen-N-Synthesizern (die die Referenzfrequenz mit nicht-ganzzahligen Werten multiplizieren) spezielle Techniken eingesetzt, die das Phasenrauschen und ähnliche Signalverunreinigungen minimieren.

Dieser Artikel beschreibt das Design von sowohl Integer- als auch Fraktionalen-N-Frequenzsynthesizern anhand von Beispielkomponenten von Analog Devices. Der Artikel beleuchtet auch die Innovationen, die es ermöglichen, diese Bauteile sowohl für serielle Highspeed-Datenverbindungen als auch für frequenzagile Radare einzusetzen.

Integer-N-Synthesizer mit Phasenregelkreis

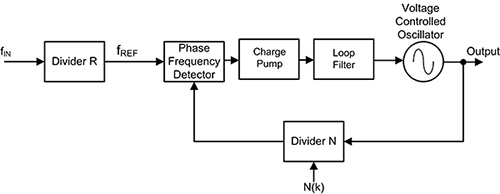

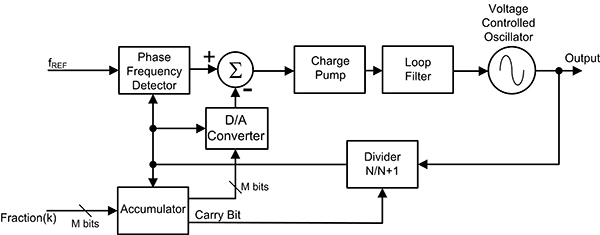

PLL-Schaltkreise werden zur Frequenz- und Phasenregelung verwendet. Sie können als Taktquellen, Frequenzmultiplikatoren, Demodulatoren, Tracking-Generatoren oder Taktrückgewinnungsschaltungen konfiguriert werden. Jede dieser Anwendungen verlangt andere Merkmale, wobei sie jedoch alle dasselbe grundlegende Schaltkreiskonzept verwenden. Abbildung 1 zeigt das Blockdiagramm eines einfachen PLL, der als Frequenzvervielfacher konfiguriert ist.

Abbildung 1: Blockschaltbild eines klassischen Integer-N-Frequenzsynthesizers mit Phasenregelkreis. (Bildquelle: DigiKey)

Abbildung 1: Blockschaltbild eines klassischen Integer-N-Frequenzsynthesizers mit Phasenregelkreis. (Bildquelle: DigiKey)

Die Funktionsweise dieser Schaltung ist typisch für alle Phasenregelkreise. Es handelt sich dabei im Wesentlichen um einen Regelkreis, der die Phase eines spannungsgeregelten Oszillators (VCO) regelt. Das Eingangssignal wird an einen Vorskalierer angelegt, der die Eingangsfrequenz durch einen Faktor R teilt. Der Ausgang des Vorskalierers ist die Referenzfrequenz, die einen Eingang eines Phasen-Frequenz-Detektors (PFD) bildet.

Der andere Eingang ist ein Rückkopplungssignal vom Ausgang eines DIV-N-Zählers (DIV-N: Division durch N). Normalerweise sind die Frequenzen beider Signale annähernd identisch. Der Ausgang des Phasendetektors ist eine Spannung, die proportional zur Phasendifferenz zwischen den zwei Eingängen ist. Wenn die Schleife entriegelt wird, wie es beim Start geschieht, oder wenn es eine große momentane Frequenzverschiebung am Eingang gibt, dann arbeitet der Phasen-Frequenz-Detektor, um die PLL-Betriebsfrequenz auf die gewünschte Einstellung zu steuern. Wenn diese Frequenz erreicht ist, kehrt der PFD in den Phasendetektormodus zurück und hat einen Ausgang, der proportional zur Phasendifferenz zwischen der Referenzfrequenz und dem Rückkopplungssignal ist.

Der Phasenfrequenzdetektor treibt eine Ladungspumpe an, die eine bipolar geschaltete Stromquelle ist. Das bedeutet, dass er positive und negative Stromimpulse in den Schleifenfilter der PLL ausgeben kann.

Der Schleifenfilter glättet das Phasenfehlersignal und bestimmt auch die dynamischen Eigenschaften der PLL. Das gefilterte Signal regelt den VCO. Beachten Sie, dass das Ausgangssignal des VCO eine Frequenz hat, die den N-fachen Wert des Eingangssignals am Frequenzreferenzeingang (FIN) hat. Dieses Ausgangssignal wird über den DIV-N-Zähler zurück an den Phasendetektor gesendet.

Normalerweise ist der Schleifenfilter so konzipiert, dass er den Merkmalen entspricht, die zur Anwendung des PLL erforderlich sind. Falls der PLL ein Signal erfassen und verfolgen soll, wird die Bandbreite des Schleifenfilters größer sein als für eine feste Eingangsfrequenz. Der Frequenzbereich, für den der PLL geeignet ist und den er überwacht, wird als Erfassungsbereich bezeichnet. Sobald der PLL eingerastet ist und ein Signal verfolgt, wird der Frequenzbereich, den der PLL verfolgt, als Haltebereich bezeichnet. Im Allgemeinen ist der Haltebereich größer als der Erfassungsbereich. Der PLL-Schleifenfilter bestimmt auch, wie schnell sich die Signalfrequenz ändern kann, und trotzdem verriegelt bleibt, d. h. die maximale Anstiegsrate. Je enger die Bandbreite ist, desto geringer ist der mögliche Phasenfehler. Das geht zu Lasten einer langsameren Reaktion und eines kleineren Erfassungsbereichs. In Taktanwendungen eingesetzte PLLs werden primär mit festen Frequenzen betrieben. Im Allgemeinen sollte die Bandbreite des Schleifenfilters viel kleiner als die Referenzfrequenz sein.

Da die PLL-Ausgangsfrequenz ein ganzzahliges Vielfaches der Referenzfrequenz ist, ist ihre Frequenzauflösung gleich der Referenzfrequenz. Um eine feinere Frequenzauflösung zu erhalten, muss die Referenzfrequenz verringert werden, was mit dem Vorskalierungszähler R geschieht.

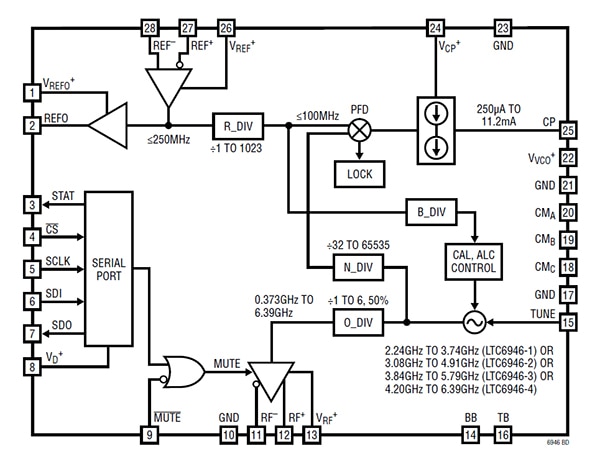

Ein kommerzielles Beispiel für einen Integer-N-Frequenzsynthesizer ist der LTC6946IUFD-3#PBF von Analog Devices, ein rauscharmer Synthesizer von 0,64 bis 5,790 GHz mit integriertem VCO und hervorragendem Störverhalten (Abbildung 2). Er gehört zu einer Familie von vier Synthesizer-ICs mit jeweils unterschiedlichen Frequenzbereichen, die insgesamt einen Bereich von 0,373 bis 6,390 GHz abdecken.

Abbildung 2: Das Blockschaltbild des Integer-N-Frequenzsynthesizers LTC6946IUFD-3#PBF von Analog Devices mit integriertem VCO. (Bildquelle: Analog Devices)

Abbildung 2: Das Blockschaltbild des Integer-N-Frequenzsynthesizers LTC6946IUFD-3#PBF von Analog Devices mit integriertem VCO. (Bildquelle: Analog Devices)

Dieser Synthesizer erfordert einen externen, vom Benutzer bereitgestellten Schleifenfilter, der für die jeweilige Anwendung optimiert werden kann. Es gibt einen internen Vorskalierzähler-Teiler mit einem Teilerbereich von 1 bis 1023. Der Schleifenteiler hat einen Bereich von 32 bis 65535. Der Ladungspumpenstrom ist von 250 Mikroampere (µA) bis 11,2 Milliampere (mA) einstellbar, um ihn an die Anforderungen des Schleifenfilters anzupassen.

Fraktionaler-N-Synthesizer mit Phasenregelkreis

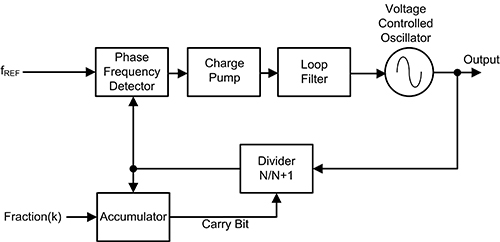

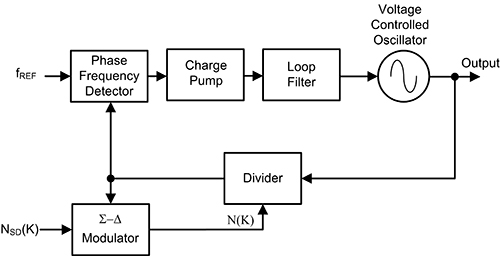

Die Frequenzauflösung des PLL-Synthesizers kann verbessert werden, indem die Schrittweite auf weniger als ganzzahlige Werte reduziert wird - d. h., es werden Teilschritte im Schleifenteiler (N) gemacht. Dies wird durch dynamisches Variieren oder „Dithering“ des Countdown-Wertes erreicht. Das bedeutet, dass die Teilereinstellung den Wert N für eine feste Anzahl von Zyklen der PLL-Ausgangsfrequenz hält und periodisch auf einen anderen Wert, z. B. N+1, gestuft wird. Wenn zum Beispiel die Teilereinstellung 4 für drei Referenzperioden und 5 für die vierte Referenzperiode ist, dann ist der effektive Countdown 4,25. Eine Möglichkeit, dies zu erreichen, ist die Verwendung eines Akkumulators, wie in Abbildung 3 dargestellt.

Abbildung 3: Das Blockdiagramm eines fraktionalen N-PLL-Synthesizers, der einen Akkumulator zur Modulation der Teilerzahl verwendet. (Bildquelle: DigiKey)

Abbildung 3: Das Blockdiagramm eines fraktionalen N-PLL-Synthesizers, der einen Akkumulator zur Modulation der Teilerzahl verwendet. (Bildquelle: DigiKey)

Der Akkumulator zählt die Ausgangsimpulse des Teilers und gibt alle M, wobei M der Modulus des Akkumulators ist, ein Übertragsbit aus, das den Eingang des Teilers verändert. Abbildung 4 setzt das Beispiel der Einstellung eines Bruchteilers von 4,25 fort.

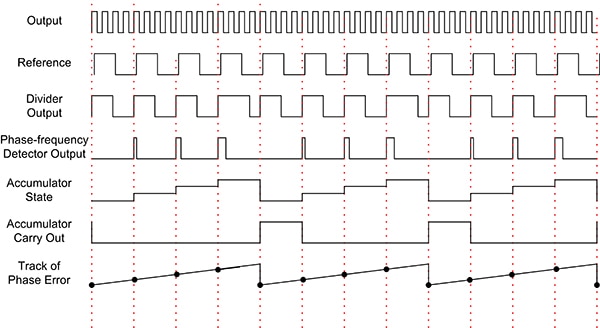

Abbildung 4: Timing-Diagramm für einen fraktionalen N-Synthesizer unter Verwendung eines Akkumulators. (Bildquelle: DigiKey)

Abbildung 4: Timing-Diagramm für einen fraktionalen N-Synthesizer unter Verwendung eines Akkumulators. (Bildquelle: DigiKey)

Der Akkumulator wird durch den geteilten Ausgang angesteuert und zählt Modulo 4, d. h. M ist gleich vier. Bei jedem vierten Impuls erzeugt er eine Übertragsausgabe, der die Teilerzahl um eins erhöht. Der Akkumulator wird zurückgesetzt und beginnt erneut zu zählen. Die Erhöhung der Teilereinstellung verschiebt die Ausgangsfrequenz, was zu einem kumulierten Phasenversatzfehler führt. Die Spur des Phasenfehlers zeigt den Impulswert in Abhängigkeit von der Zeit.

Die durchschnittliche Teilereinstellung ist 4,25, aber der Synthesizer-Ausgang ist phasenmoduliert, was zu Störgeräuschen im Ausgang führt. Betrachtet man den Zustand des Akkumulators, ist es offensichtlich, dass er dem Phasenfehler folgt. Damit kann die Modulation entfernt werden, wie in Abbildung 5 gezeigt.

Abbildung 5: Verwendung des D/A-gewandelten Akkumulatorzustands zur Aufhebung der Phasenmodulation aufgrund des fraktionalen N-Dithering. (Bildquelle: DigiKey)

Abbildung 5: Verwendung des D/A-gewandelten Akkumulatorzustands zur Aufhebung der Phasenmodulation aufgrund des fraktionalen N-Dithering. (Bildquelle: DigiKey)

Der Akkumulatorzustand wird durch einen Digital/Analog-Wandler (D/A) in ein analoges Signal umgewandelt, skaliert und vom Ausgang des Phasenfrequenzdetektors subtrahiert, um die Phasenmodulation aufgrund des fraktionalen N-Dithering aufzuheben. Dies muss mit großer Sorgfalt geschehen; wenn das Korrektursignal nicht genau mit dem Phasenfehler übereinstimmt, kommt es zu Störsignalen am Ausgang.

Einführung des Sigma-Delta-Modulators

Die Periodizität im Akkumulator ist die Ursache für störende Ausgaben des Synthesizers. Wenn der Akkumulator durch einen Sigma-Delta-Modulator ersetzt wird, können digitale Techniken angewandt werden, um die Teilerzahl so zu modulieren, dass Störsignale und Rauschen minimiert werden. Dieser Austausch ist in Abbildung 6 dargestellt.

Abbildung 6: Das Ersetzen des Akkumulators durch einen Sigma-Delta-Modulator ermöglicht die Anwendung digitaler Techniken zur Variation der Teilerzahl, um Störsignale zu reduzieren. (Bildquelle: DigiKey)

Abbildung 6: Das Ersetzen des Akkumulators durch einen Sigma-Delta-Modulator ermöglicht die Anwendung digitaler Techniken zur Variation der Teilerzahl, um Störsignale zu reduzieren. (Bildquelle: DigiKey)

Es gibt eigentlich zwei gängige digitale Techniken, die in der Sigma-Delta-Modulationstopologie eingesetzt werden. Bei der ersten wird die Anzahl der N Teiler über einen größeren Wertebereich erhöht, so dass der durchschnittliche Teilungsfaktor den gewünschten Teilerwert ergibt. Dadurch werden die primären fraktionalen Spuren reduziert. Der akkumulatorbasierte Synthesizer variiert die Zählung zwischen zwei Zuständen. Dies ist ein Modulationsverfahren erster Ordnung. Eine fraktionale Sigma-Delta-PLL n-ter Ordnung moduliert den N-Zähler zwischen 2n verschiedenen Werten. Ein Modulator dritter Ordnung würde z. B. zwischen acht verschiedenen Teilerwerten und ein Modulator vierter Ordnung zwischen 16 verschiedenen Teilerwerten abwechseln.

Die zweite digitale Technik - auch Dithering genannt - beinhaltet die Zufallsgenerierung der 2N-Sequenz, so dass sie pseudozufällig ist. Während immer noch ein durchschnittliches Teilerverhältnis beibehalten wird, wandelt es die fraktionalen Spuren in geformtes Zufallsrauschen um, so dass es von der PLL gefiltert werden kann.

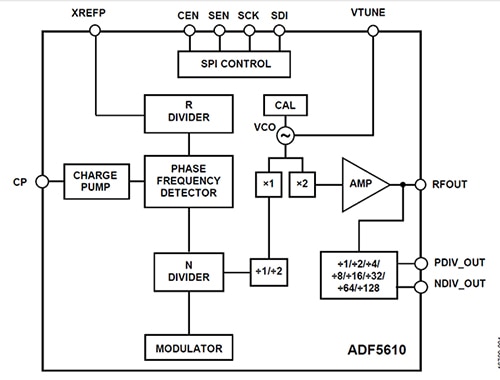

Eine kommerzielle Version eines fraktionalen Sigma-Delta-N-Synthesizers ist der ADF5610BCCZ von Analog Devices, ein rauscharmer fraktionaler N-Synthesizer für 0,57 Megahertz (MHz) bis 14,6 GHz mit integriertem VCO (Abbildung 7).

Abbildung 7: Ein Blockdiagramm des ADF5610BCCZ von Analog Devices, das sowohl fraktionale N- als auch ganzzahlige Synthesizer-Konfigurationen unterstützt. (Bildquelle: Analog Devices)

Abbildung 7: Ein Blockdiagramm des ADF5610BCCZ von Analog Devices, das sowohl fraktionale N- als auch ganzzahlige Synthesizer-Konfigurationen unterstützt. (Bildquelle: Analog Devices)

Der ADF5610 benötigt einen externen Referenzoszillator und einen Schleifenfilter. Er enthält einen integrierten VCO mit einer Grundfrequenz von 3650 MHz bis 7300 MHz. Diese Frequenzen werden intern verdoppelt und an den RFOUT-Pin (HF-Ausgang) geführt. Es gibt einen Differenzausgang, mit dem die verdoppelte VCO-Frequenz durch Faktoren von 1, 2, 4, 8, 16, 32, 64 oder 128 geteilt werden kann, was die Erzeugung von HF-Ausgangsfrequenzen bis zu 57 MHz ermöglicht.

Der ADF5610 verwendet einen fortschrittlichen Sigma-Delta-Modulator mit einem fraktionalen 24-Bit-Modulus, der außergewöhnlich niedrige Störpegel erreicht. Wie bei allen Synthesizern, die einen Sigma-Delta-Modulator verwenden, nutzt dieses Gerät digitale Signalverarbeitungstechniken, um das gewünschte durchschnittliche Teilerverhältnis zu finden. Dieser Prozess, der mit der PFD-Rate getaktet ist, erzeugt ein Ausgangsmodulationsrauschen, das als Quantisierungsrauschen bezeichnet wird und einen Hochpass-Frequenzgang aufweist. Der externe Tiefpassschleifenfilter wird verwendet, um dieses Quantisierungsrauschen auf einen Pegel unterhalb des Phasenrauschens des VCOs zu filtern und so zu verhindern, dass das Rauschen zum Gesamtphasenrauschen des Systems beiträgt.

Der ADF5610 enthält auch einen exakten Frequenzmodus für 0 Hertz (Hz) Frequenzfehler. Dieser Modus ist in der Lage, exakte Frequenzen zwischen benachbarten ganzzahligen N-Grenzschritten zu generieren, während immer noch der volle 24-Bit-Phasenakkumulator-Modulus verwendet wird. Es werden exakte Frequenzschritte mit einer hohen Phasendetektor-Vergleichsrate erreicht, so dass die PLL in diesem Modus ein ausgezeichnetes Phasenrauschen und Störverhalten beibehält.

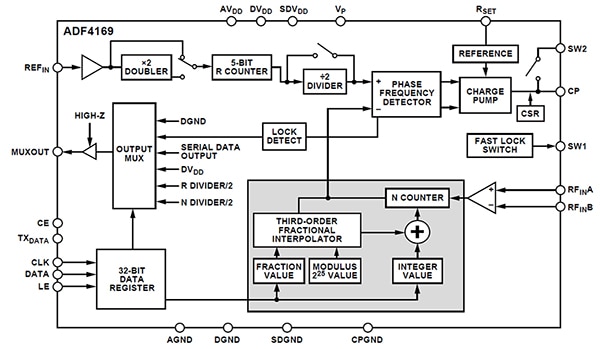

Der ADF4169CCPZ-RL7 von Analog Devices ist ein weiterer PLL-Synthesizer, der entweder als Integer-N- oder als Fraktional-N-Komponente konfiguriert werden kann. Er arbeitet mit einer HF-Bandbreite von bis zu 13,5 GHz mit Modulation und Wellenformerzeugung. Er verwendet einen externen Referenzfrequenzeingang, einen VCO und einen Schleifenfilter. Er verfügt über einen Sigma-Delta-Modulator dritter Ordnung für die fraktionale N-Synthese, der deaktiviert werden kann, so dass das Gerät im Integer-N-Modus betrieben werden kann (Abbildung 8).

Abbildung 8: Der ADF4169CCPZ-RL7 von Analog Devices verwendet einen Sigma-Delta-Modulator dritter Ordnung. (Bildquelle: Analog Devices)

Abbildung 8: Der ADF4169CCPZ-RL7 von Analog Devices verwendet einen Sigma-Delta-Modulator dritter Ordnung. (Bildquelle: Analog Devices)

Der Synthesizer ADF4158WCCPZ-RL7 ist für den Einsatz in frequenzmodulierten Dauerstrichradargeräten (FMCW) vorgesehen. Er ist in der Lage, verschiedene Arten von modulierten Wellenformen im Frequenzbereich zu erzeugen, einschließlich Sägezahn- und Dreiecksrampen. Dies ist eine besondere Funktion, die bei Radaranwendungen erforderlich ist.

Fazit

Steigende Datenraten in seriellen Highspeed-Kommunikationsbussen erfordern, dass Entwickler nicht nur direkte digitale Synthesizer - die am besten unter 3 GHz arbeiten - für Systemtaktlösungen verwenden. PLL-basierte Frequenzsynthesizer mit Integer-N- und Fraktionalen-N-Topologien liefern stabile, rauscharme Signale für Hochfrequenztakt-, serielle Datenkommunikations- und Radaranwendungen für Frequenzen bis zu einigen zehn Gigahertz.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.