Verstehen und Minimieren der Auswirkungen von Jitter auf Highspeed-Verbindungen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2023-12-21

Taktoszillatoren sorgen für den Herzschlag, oder das Timing moderner Schaltkreise, indem sie die Systemkomponenten takten. Da die Systemgeschwindigkeiten auf Hunderte von Megahertz (MHz) und mehr ansteigen, müssen diese Takte schneller sein und einen sehr geringen Jitter aufweisen, der in der Regel unter 100 Femtosekunden (fs) liegt, um die Systemleistung aufrechtzuerhalten. Außerdem müssen sie trotz Temperatur- und Spannungsschwankungen über einen längeren Zeitraum hinweg ihren niedrigen Jitter beibehalten.

Ein gewisser Jitter wird durch Rauschen und Verzerrungen auf dem Signalweg verursacht und kann durch Reclocking- und Retiming-Techniken etwas reduziert werden. Jitter wird jedoch auch durch die Taktquelle erzeugt, bei der es sich in der Regel um einen Oszillator handelt. Dies ist auf verschiedene physikalische Phänomene zurückzuführen, wie z. B. thermisches Rauschen, Prozessmängel, Rauschen der Stromversorgung, andere externe Störungen, die in den Taktoszillator gelangen, Materialspannungen und viele andere subtile Faktoren. Unabhängig von der Quelle muss alles getan werden, um den inhärenten Taktjitter zu minimieren, da die Mängel nicht reversibel sind.

In diesem Artikel werden Jitter-Probleme aus verschiedenen Blickwinkeln erörtert. Anschließend werden verschiedene Taktoszillatoren von Abracon LLC vorgestellt und es wird gezeigt, wie Jitter durch Anpassung der Performance des Taktoszillators an die Anwendung minimiert werden kann.

Jitter-Grundlagen

Unter Takt-Jitter versteht man die Abweichung einer Taktflanke von ihrer idealen Position in der Zeit. Dieser Jitter beeinträchtigt die zeitliche Präzision und Genauigkeit der Übertragung von Datensignalen, die vom Taktsignal getaktet werden, und führt zu einer Verschlechterung des Signal-Rausch-Verhältnisses (SNR) bei den Empfänger-Dekodier-/Demodulationsschaltungen oder anderen System-ICs. Dies führt zu einer höheren Bitfehlerrate (BER), vermehrten Neuübertragungen und einem geringeren effektiven Datendurchsatz.

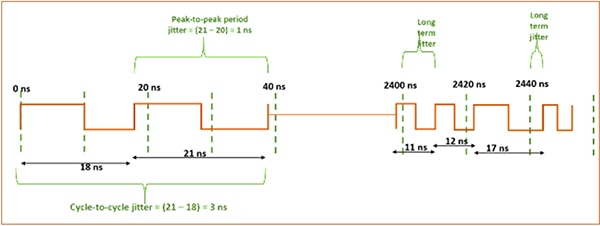

Aufgrund seiner Kritikalität wird Taktjitter in Systemen, die ein Signal von einer Sendequelle über Kabel, Steckverbinder oder Leiterplatten an einen Empfänger weiterleiten, häufig analysiert. Je nach Anwendung kann er auf viele Arten charakterisiert werden, einschließlich Zyklus-zu-Zyklus-Jitter, Periodenjitter und Langzeitjitter (Abbildung 1).

Abbildung 1: Der Begriff „Jitter“ umfasst viele Timing-Variationen, darunter Zyklus-zu-Zyklus-Jitter, Periodenjitter und Langzeitjitter. (Bildquelle: VLSI Universe)

Abbildung 1: Der Begriff „Jitter“ umfasst viele Timing-Variationen, darunter Zyklus-zu-Zyklus-Jitter, Periodenjitter und Langzeitjitter. (Bildquelle: VLSI Universe)

- Zyklus-zu-Zyklus-Jitter bezeichnet die Änderung der Taktperiode über zwei aufeinanderfolgende Zyklen hinweg und hat nichts mit der zeitlichen Frequenzänderung zu tun.

- Der Periodenjitter ist die Abweichung einer beliebigen Taktperiode von ihrer mittleren Periode. Er ist die Differenz zwischen der idealen und der tatsächlichen Taktperiode und kann entweder als RMS-Periodenjitter (Root-Mean-Square) oder als Spitze-zu-Spitze-Periodenjitter angegeben werden.

- Langzeitjitter ist die Abweichung der Taktflanke von ihrer Idealposition über einen längeren Zeitraum. Sie ist in etwa vergleichbar mit einer Drift.

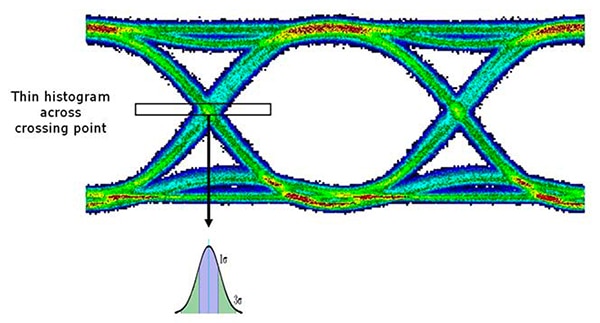

Jitter kann das Timing anderer Unterfunktionen, Komponenten oder Systeme stören, die für eine Datenwiederherstellung mit niedriger BER verwendet werden, oder Komponenten wie Speicherelemente oder Prozessoren in einem synchronen System. Im Augendiagramm von Abbildung 2 ist dies als Verbreiterung des Kreuzungspunktes im Bittakt zu erkennen.

Abbildung 2: In einem Augendiagramm wird Jitter als eine Verbreiterung des kritischen Timing-Crossover-Punkts im Datenstrom dargestellt. (Bildquelle: Kevin K. Gifford/Univ. von Colorado)

Abbildung 2: In einem Augendiagramm wird Jitter als eine Verbreiterung des kritischen Timing-Crossover-Punkts im Datenstrom dargestellt. (Bildquelle: Kevin K. Gifford/Univ. von Colorado)

Bei seriellen Datenverbindungen muss die Schaltung auf der Empfängerseite versuchen, ihren eigenen Takt für eine optimale Dekodierung des Datenstroms wiederherzustellen. Dazu muss sie sich mit dem Quellentakt synchronisieren, was häufig mit einer Phasenregelschleife (PLL) geschieht. Jitter beeinträchtigt die Fähigkeit des Systems, dies präzise zu tun, und gefährdet die Fähigkeit, die Daten mit einer niedrigen BER wiederherzustellen.

Beachten Sie, dass Jitter sowohl im Zeit- als auch im Frequenzbereich gemessen werden kann; beide Sichtweisen sind für dasselbe Phänomen gleichermaßen gültig. Das Phasenrauschen ist eine Betrachtung des Rauschspektrums um das Oszillatorsignal im Frequenzbereich, während der Jitter ein Maß für die zeitliche Genauigkeit der Oszillatorperiode im Zeitbereich ist.

Jitter-Messungen können auf verschiedene Weise ausgedrückt werden. Üblich sind Zeiteinheiten wie „Jitter von 10 Pikosekunden“ (ps). Die Wurzel aus dem quadratischen Mittelwert (RMS) des Phasenjitters ist ein Zeitbereichs-Parameter, der aus der Messung des Phasenrauschens (Frequenzbereich) abgeleitet wird. Jitter wird manchmal auch als Phasenjitter bezeichnet, was verwirrend sein kann, aber es ist immer noch der Jitter-Parameter im Zeitbereich.

Wenn die Betriebsfrequenzen der Verbindungen und ihre Takte von einigen zehn MHz auf Hunderte von MHz und mehr ansteigen, sinkt der zulässige Jitter der Taktquelle auf etwa 100 fs oder weniger. Diese Frequenzen gelten für optische Module, Cloud Computing, Netzwerke und Highspeed-Ethernet, allesamt Funktionen und Anwendungen, die eine Trägerfrequenz zwischen 100 und 212/215 MHz und Datenraten von bis zu 400 Gigabit pro Sekunde (Gbit/s) erfordern.

Die Verwendung des Quarzes

Die gängigste Methode zur Erzeugung eines stabilen, konsistenten und frequenzgenauen Taktsignals ist die Verwendung eines Quarzoszillators. Eine zugehörige Oszillatorschaltung unterstützt den Quarz. Es gibt viele solcher Schaltungsfamilien, die jeweils unterschiedliche Kompromisse aufweisen. Kristalle werden seit den 1930er Jahren für die drahtlose Funkkommunikation im Mittelfrequenzbereich (300 Kilohertz (kHz) bis 3 MHz) und im Hochfrequenzbereich (3 bis 30 MHz) eingesetzt.

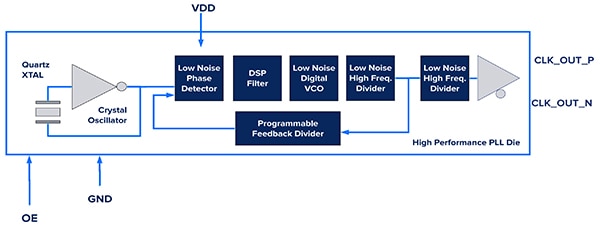

Ein weit verbreiteter Ansatz zur Erzeugung von Taktsignalen mit geringem Jitter ist die Verwendung einer der vielen Varianten PLL-basierter Architekturen. Die Bausteine der AX5- und AX7-ClearClock™-Familien von Abracon beispielsweise haben ein Gehäuse von 5 × 3,2 Millimetern (mm) bzw. 5 × 7 mm und verwenden eine hochentwickelte PLL-Technologie für eine überragend niedrige Jitter-Performance (Abbildung 3).

Abbildung 3: Die Taktoszillatoren AX5 und AX7 von Abracon verwenden eines der vielen PLL-basierten Designs, jedoch mit subtilen Verbesserungen zur Minimierung von Jitter. (Bildquelle: Abracon)

Abbildung 3: Die Taktoszillatoren AX5 und AX7 von Abracon verwenden eines der vielen PLL-basierten Designs, jedoch mit subtilen Verbesserungen zur Minimierung von Jitter. (Bildquelle: Abracon)

Neben der Betriebsfrequenz und dem Oszillatordesign wird die Jitter-Performance auch durch die physische Größe des Quarzes im Oszillatorkern beeinflusst. Je kleiner dieser Kristall ist, desto schwieriger wird es, eine hervorragende RMS-Jitter-Performance zu erzielen.

Für Taktlösungen im 100- bis 200-MHz-Bereich und in kleineren Formfaktoren als die PLL-basierten AX5- und AX7-Bausteine ist eine neue Oszillatorarchitektur erforderlich. Diese Anforderungen an eine geringere Größe sind in der Regel mit den optischen Transceivern und Modulen der neuesten Generation verbunden. Es gibt vier bewährte Möglichkeiten, einen Taktoszillator im Bereich von 100 bis 200 MHz zu entwickeln:

- Verwendung eines Quarzoszillators mit einem invertierten Mesa-Quarz als Resonatorelement

- Verwendung eines Quarzoszillators mit einem Quarzrohling mit dritter harmonischer Oberschwingung (dritte Harmonische) als Resonatorelement

- Verwendung einer Oszillatorschleife, die auf einem Quarzrohling mit dritter harmonischer Oberschwingung/Grundschwingung unter 50 MHz oder einem temperaturkompensierten Quarzoszillator unter 50 MHz basiert, der mit einem PLL-IC mit ganzzahligem oder gebrochenem (fraktionalem) Modus kombiniert ist

- Verwendung einer MEMS-Oszillatorschleife (MikroElektroMechanisches System) unter 50 MHz, die mit einem PLL-IC mit ganzzahligem oder gebrochenem Modus kombiniert ist

Option 1 bietet weder die beste RMS-Jitter-Performance noch ist sie die kostengünstigste Lösung. Option 3 ist kompliziert und weist Leistungsmängel auf, während der MEMS-Resonator-Ansatz von Option 4 die primären Leistungskriterien von maximal 200 fs RMS-Jitter nicht erfüllt. Im Gegensatz dazu wird bei Option 2 ein optimal gestalteter Quarzrohling mit dritter Harmonischer verwendet, wobei die Geometrie der Elektroden und die Optimierung des Schnittwinkels berücksichtigt werden. Diese Kombination ist optimal in Bezug auf Kosten, Performance und Größe.

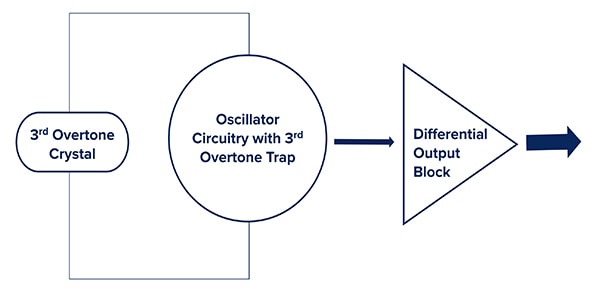

Mit diesem Ansatz hat Abracon ClearClock-Lösungen mit „dritter Harmonischer“ entwickelt (Abbildung 4). Diese Bausteine nutzen eine leisere Architektur, um eine überragende, extrem niedrige RMS-Jitter-Leistung und extreme Energieeffizienz in Miniaturgehäusen von nur 2,5 × 2,0 x 1,0 mm zu ermöglichen.

Abbildung 4: Die ClearClock-Lösung von Abracon mit „dritter Harmonischer“ verwendet eine leisere Architektur, um die Gesamtleistung und Energieeffizienz zu verbessern. (Bildquelle: Abracon)

Abbildung 4: Die ClearClock-Lösung von Abracon mit „dritter Harmonischer“ verwendet eine leisere Architektur, um die Gesamtleistung und Energieeffizienz zu verbessern. (Bildquelle: Abracon)

Bei diesem Schema sorgt ein sorgfältiges Design des Quarzes mit dritter Harmonischer in Verbindung mit der richtigen Filterung und dem „Trapping“ des gewünschten Trägersignals für eine hervorragende RMS-Jitter-Performance bei den gewünschten Trägerfrequenzen.

Bei dieser Architektur wird kein typischer PLL-Ansatz verwendet, so dass es keine Aufwärtswandlung gibt. Folglich ist keine gebrochene oder ganzzahlige PLL-Standardmultiplikation erforderlich, und die endgültige Ausgangsfrequenz steht in einer Eins-zu-Eins-Korrelation mit der Resonanzfrequenz des Quarzes mit dritter Harmonischer. Der Verzicht auf eine gebrochene oder ganzzahlige Multiplikation vereinfacht das Design und ermöglicht minimalen Jitter bei kleinstmöglicher Größe.

Spezifikationen und Performance in der Realität

Taktoszillatoren sind mehr als nur ein Quarz und seine analoge Schaltung. Sie beinhalten eine Pufferung, um sicherzustellen, dass die Ausgangslast des Oszillators und ihre kurz- und langfristigen Schwankungen die Leistung des Geräts nicht beeinträchtigen. Sie unterstützen außerdem verschiedene digitale Logik-Ausgangspegel für die Kompatibilität der Schaltungen. Diese Kompatibilität beseitigt die Notwendigkeit für einen externen Logik-Pegelwandler-IC. Ein solcher IC würde die Kosten, den Platzbedarf und den Jitter erhöhen.

Da Taktoszillatoren in so vielen verschiedenen Anwendungen mit unterschiedlichen Schienenspannungen eingesetzt werden, müssen sie mit einer Vielzahl von Versorgungsspannungen wie +1,8 Volt, +2,5 Volt oder +3,3 Volt sowie mit kundenspezifischen Werten angeboten werden, die typischerweise von 2,25 bis 3,63 Volt reichen. Außerdem müssen sie mit unterschiedlichen Ausgangsformaten wie LVPECL (Low-Voltage Positive/Pseudo-Emitter-Coupled Logic) und LVDS (Low-Voltage Differential Signaling) sowie anderen Formaten verfügbar sein.

Ein Blick auf zwei Familien von Quarztaktoszillatoren, den AK2A und den AK3A, zeigt, was durch ein ausgeklügeltes Verständnis und die Integration von Materialien, Design, Architektur und Test erreicht werden kann. Die beiden Familien ähneln sich, wobei die größten Unterschiede in der Größe und der maximalen Frequenz liegen.

Die Familie AK2A: Diese Familie von Quarzoszillatoren wird mit Nennfrequenzen von 100 bis 200 MHz angeboten und ist mit Betriebsspannungen von 2,5 Volt, 3,3 Volt und 2,25 bis 3,63 Volt mit LVPECL-, LVDS- und HCSL-Differenzausgangslogik erhältlich.

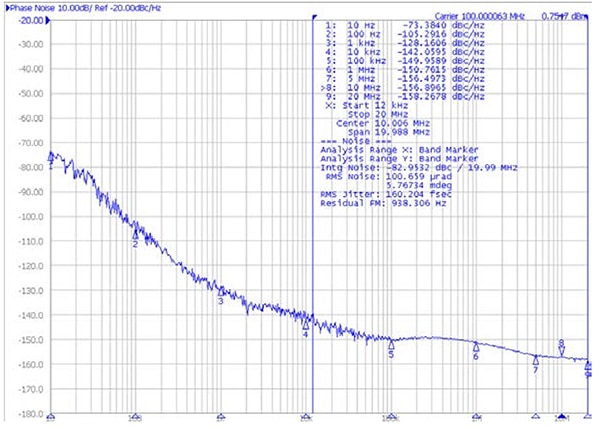

Alle Familienmitglieder haben eine ähnliche Performance, einschließlich eines geringen RMS-Jitters. Der AK2ADDF1-100.000T zum Beispiel ist ein Baustein für 100,00 MHz und 3,3 Volt, mit LVDS-Ausgängen und einem RMS-Jitter von 160,2 fs (Abbildung 5). Seine Frequenzstabilität ist mit mehr als ±15 ppm (parts per million) über die Temperatur ausgezeichnet und er wird in einem SMD-Gehäuse (SMD = oberflächenmontierbar) mit sechs Anschlüssen und den Abmessungen 2,5 × 2,0 × 1,0 mm geliefert.

Abbildung 5: Der Jitter beträgt 160 fs für den AK2ADDF1-100.000T, einen 3,3-Volt-Baustein für 100 MHz und mit LVDS-Ausgängen. (Bildquelle: Abracon)

Abbildung 5: Der Jitter beträgt 160 fs für den AK2ADDF1-100.000T, einen 3,3-Volt-Baustein für 100 MHz und mit LVDS-Ausgängen. (Bildquelle: Abracon)

Mit zunehmender Taktfrequenz muss der Jitter jedoch abnehmen, um die Leistung auf Systemebene zu erhalten. Beim AK2ADDF1-156.2500T, einem 156,25 MHz LVDS-Oszillator, sinkt der typische RMS-Jitter auf 83 fs.

Die Familie AK3A: Die Bauelemente der AK3A-Familie sind etwas größer als die der AK2A-Familie mit einem Footprint von 3,2 × 2,5 × 1,0 mm (Abbildung 6). Es sind Versionen erhältlich, die bis 212,5 MHz spezifiziert sind, also etwas höher als die 200-MHz-Grenze für die AK2A-Familie.

Abbildung 6: Die Quarzoszillatoren der Serie AK3A (rechts) sind etwas länger und breiter als die der Serie AK2A (links); sie sind für Frequenzen bis 212,5 MHz erhältlich, im Vergleich zu 200 MHz für den AK2A. (Bildquelle: Abracon)

Abbildung 6: Die Quarzoszillatoren der Serie AK3A (rechts) sind etwas länger und breiter als die der Serie AK2A (links); sie sind für Frequenzen bis 212,5 MHz erhältlich, im Vergleich zu 200 MHz für den AK2A. (Bildquelle: Abracon)

Die allgemeinen Spezifikationen für diesen AK3A-Baustein ähneln denen des entsprechenden Mitglieds der AK2A-Familie. Ein Beispiel ist der AK3ADDF1-156.2500T3, ein LVDS-Oszillator für 156,25 MHz, der einen typischen RMS-Jitter von 81 fs aufweist und damit etwas besser ist als das entsprechende Mitglied der AK2A-Familie.

Der Jitter für beide Familien variiert je nach Betriebsfrequenz, Betriebsspannung, Gehäusegröße und Wahl der Ausgänge.

Zusätzliche Überlegungen aus der Praxis

Es reicht nicht aus, einen Taktoszillator zu haben, der nur an dem Tag, an dem er das Werk verlässt, die Spezifikationen erfüllt. Wie bei allen Bauteilen, insbesondere bei analogen und passiven Bauteilen, kommt es bei diesen Oszillatoren im Laufe der Zeit aufgrund der Alterung der verwendeten Materialien und der inneren Spannungen zu einer Drift.

Diese Tatsache stellt vor allem für Hochleistungs-Taktoszillatoren eine Herausforderung dar, da es keine bequemen oder einfachen Möglichkeiten gibt, diese Drift durch Hinzufügen von Software oder cleveren Schaltungen zu korrigieren oder zu kompensieren. Es gibt jedoch einige Möglichkeiten, die Auswirkungen der Drift abzuschwächen. Dazu gehören längere Burn-in-Perioden durch den Endbenutzer für eine beschleunigte Alterung des Oszillators oder die Verwendung eines temperaturstabilisierten Oszillators in einem ofengesteuerten Gehäuse. Ersteres ist zeitaufwändig und eine Herausforderung für die Lieferkette, letzteres ist groß, kostspielig und energiehungrig.

In der Erkenntnis, dass die Alterung ein kritischer Parameter ist, bietet die ClearClock-Familie von Abracon eine strenge, allumfassende Frequenzgenauigkeit über die gesamte Lebensdauer des Endprodukts von 10 bis 20 Jahren. Abracon gewährleistet die Einhaltung einer Frequenzstabilität von besser als ±50 ppm über diesen Zeitraum. Dies wird durch die sorgfältige Auswahl und Herstellung des Quarzes mit dritter Harmonischer und dessen Konditionierung erreicht, um eine Stabilität von ±15 ppm über -20°C bis +70°C und ±25 ppm über -40°C bis +85°C zu erreichen.

Wie immer geht es bei der Technik um Kompromisse. Die Abracon-Serien AK2A und AK3A bieten im Vergleich zu ihren Vorgängerserien (Gen I AK2 bzw. AX3) eine verbesserte Jitter-Rausch-Performance, indem sie einen Oszillator-ASIC der nächsten Generation (Gen II) verwenden und damit eine extrem niedrige RMS-Jitter-Performance gewährleisten.

Diese Verbesserung wird auf Kosten eines geringfügigen Anstiegs des Stromverbrauchs erreicht. Der maximale Stromverbrauch steigt von 50 Milliampere (mA) bei Gen I auf 60 mA bei Gen II, wobei die Niederspannungskomponenten etwa die Hälfte dieses Wertes verbrauchen. Die ClearClock-Oszillatoren der zweiten Generation bieten daher einen extrem niedrigen RMS-Jitter bei gleichzeitig niedrigem Stromverbrauch.

Fazit

Taktoszillatoren sind das Herzstück einer Datenverbindung oder einer Taktfunktion, und ihre Genauigkeit, ihr Jitter und ihre Stabilität sind kritische Parameter für das Erreichen der erforderlichen Leistung auf Systemebene, einschließlich eines hohen SNR und einer niedrigen BER. Höhere Taktfrequenzen können durch innovative Materialauswahl und Architekturen erreicht werden, die den strengen Leistungsanforderungen der Industrie und ihren verschiedenen Normen entsprechen. Die Serien AK2A und AK3A von Abracon zeichnen sich durch einen Jitter von unter 100 fs im Bereich von 100 bis 200 MHz in SMD-Gehäusen aus, die nur wenige Millimeter auf jeder Seite messen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.