Verwendung ferroelektrischer Speicher zur Verbesserung der Zuverlässigkeit von Automobilanwendungen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-06-28

Nicht-flüchtiger Speicher (NVM, Non-Volatile Memory) spielt in beinahe allen Embedded-Systemen eine wichtige Rolle. In vielen Designs werden die Anforderungen an den nicht-flüchtigen Speicher jedoch zunehmend strenger, was die Schreib- und Zugriffsgeschwindigkeit für Daten, die Datenhaltung und die Leistungsaufnahme betrifft. Dies gilt insbesondere für Anwendungen im Automobilbau, bei denen die Entwickler erweiterte Funktionen wie moderne Fahrerassistenzsysteme (ADAS) integrieren möchten, die missionskritisch sind.

Um den sicheren und zuverlässigen Betrieb dieser Systeme zu gewährleisten, müssen die Entwickler verstärkt auf moderne F-RAM-Speicher (Ferroelectric Random Access Memory) als stromsparende NVM-Option für den Automobilbau setzen, die zuverlässig, energieeffizient und schneller als aktuell verwendete NVM-Lösungen ist.

Dieser Artikel beschreibt die Hauptmerkmale der F-RAM-Technologie und wie Entwickler mit zwei F-RAM-Lösungen von Cypress Semiconductor die Zuverlässigkeit von ADAS-Systemen verbessern und sie als Proxy zur Nutzung von F-RAM-Technologie in anderen missionskritischen Anwendungen verwenden können.

Anforderungen an NVM für den Automobilbau

Sicherheitsanwendungen für den Automobilbau verkörpern den Trend in der Branche zur Integration modernerer Sensoren mit höherer Auflösung und schnelleren Aktualisierungsraten. Subsysteme im Automobilbau wie ADAS-Systeme, elektronische Steuergeräte (ECUs, Electronic Control Units) und Ereignisdatenschreiber (EDR, Event Data Recorders) entwickeln sich stetig weiter und benötigen enorme Datenmengen, die von einer Vielzahl an Sensoren gesammelt werden. Jeglicher Verlust von Daten oder sogar ein langsamer Zugriff auf die Daten kann die Systemsicherheit, das Fahrzeug und seine Insassen gefährden.

Bei ADAS-Designs beispielsweise kann die Zeit, die für das Schreiben von Daten in den EEPROM (einen elektrisch löschbaren, programmierbaren Nur-Lese-Speicher) benötigt wird, zu einer potenziell verheerenden Verzögerung von automatischen Manövern führen, mit denen erfassten Gefahren ausgewichen werden soll. Bei EDR-Designs können langsame Schreibvorgänge dazu führen, dass wichtige Sensordaten verloren gehen, falls bei einem Unfall mit dem Fahrzeug die Stromversorgung ausfällt. In diesem Fall würden wohl genau diejenigen Daten verloren gehen, die zur Ermittlung der Unfallursache erforderlich wären.

Merkmale von F-RAM-NVMs

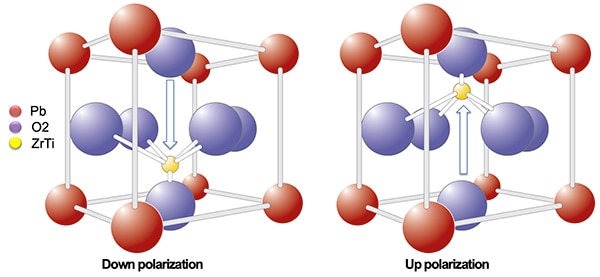

Speicherkomponenten mit F-RAM-Technologie stellen eine effektive NVM-Alternative dar, die der steigenden Nachfrage nach und den Leistungsanforderungen einer zuverlässigen Datenspeicherung mit schnellem Zugriff gerecht werden können. Die Komponenten werden aus Blei-Zirkon-Titanat (Pb[ZrxTi1−x]O3) gefertigt, das auch einfach als PZT bezeichnet wird. PZT besitzt die einzigartige Eigenschaft, dass das positiv geladene Metallion (Kation) im PZT-Kristall einen von zwei möglichen Polarisationszuständen einnimmt – aufwärts oder abwärts – und dabei der Richtung des anliegenden elektrischen Felds folgt (Abbildung 1).

Abbildung 1: Die F-RAM-Technologie nutzt zwei gleich stabile Energiezustände von PZT-Materialien, wenn diese einem elektrischen Feld ausgesetzt werden. (Bildquelle: Cypress Semiconductor)

Abbildung 1: Die F-RAM-Technologie nutzt zwei gleich stabile Energiezustände von PZT-Materialien, wenn diese einem elektrischen Feld ausgesetzt werden. (Bildquelle: Cypress Semiconductor)

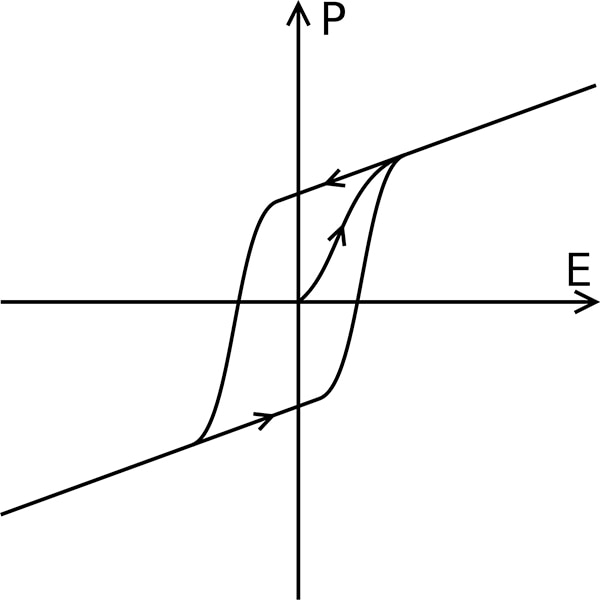

Da es sich bei beiden Zuständen um gleiche Niedrigenergiezustände handelt, verbleibt das Kation in seinem letzten Polarisationszustand, wenn das elektrische Feld entfernt wird (Abbildung 2). In einem elektrischen Feld mit positiver oder negativer Feldstärke wechselt das Kation erneut schnell in den entsprechenden Polarisationszustand, wobei es einer charakteristischen Hystereseschleife folgt, wie sie so auch in ähnlicher Form bei ferromagnetischen Materialien auftritt.

Abbildung 2: PZT-Materialien folgen einer charakteristischen Hystereseschleife, wenn sie als Reaktion auf ein elektrisches Feld zwischen zwei stabilen Polarisationszuständen wechseln. (Bildquelle: WikiMedia Commons/CC-BY-SA-3.0)

Abbildung 2: PZT-Materialien folgen einer charakteristischen Hystereseschleife, wenn sie als Reaktion auf ein elektrisches Feld zwischen zwei stabilen Polarisationszuständen wechseln. (Bildquelle: WikiMedia Commons/CC-BY-SA-3.0)

Die Merkmale der F-RAM-Technologie bringen direkt eine Reihe von Vorteilen für NVM-Komponenten mit sich, die mit dieser Technologie gefertigt werden. Da beide PZT-Energiezustände gleich stabil sind, behält das Kation seine letzte Position über Jahrzehnte oder möglicherweise sogar Jahrhunderte hinweg bei, wodurch F-RAM-NVM-Komponenten auf PZT-Basis eine beispiellose Datenhaltung ermöglichen. Und da diese Technologie statt auf den Ladungsspeicherungsmechanismen anderer NVM-Technologien auf der Kationenposition basiert, sind F-RAM-Komponenten außerdem von sich aus strahlungsbeständig und immun gegen einzelne Ereignisstörungen durch ionisierende Strahlung.

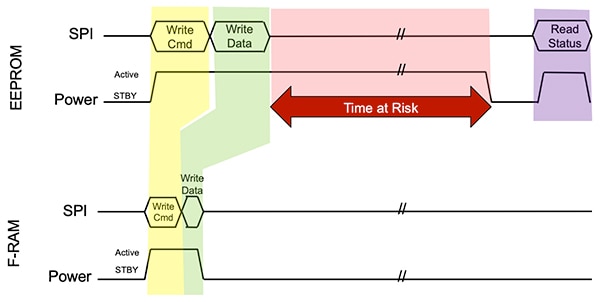

Neben ihren Vorteilen hinsichtlich der Langzeitspeicherung verbessert die F-RAM-Technologie die dynamische Leistung von NVM-Komponenten. Der Zustandsübergang erfolgt sehr schnell und erfordert wenig Energie, wodurch eine grundlegende Einschränkung im Zusammenhang mit EEPROMs oder Flash-Speichern in missionskritischen Anwendungen überwunden wird. EEPROMs und Flash-Komponenten erfordern eine erhebliche „Einwirkzeit“ im Zusammenhang mit der Datenpufferung während ihren relativ langsamen Schreibzyklen. Diese zusätzliche Verzögerung beim Schreibzyklus kann zu einem Zeitraum führen, in dem Daten gefährdet sein und sogar vollständig verloren gehen können, falls die Stromversorgung unterbrochen wird, bevor der Vorgang mit der Lesestatusprüfung abgeschlossen wurde (Abbildung 3).

Abbildung 3: Die zusätzliche Einwirkzeit (rote Markierung) während EEPROM- oder Flash-Schreibvorgängen führt zu einem bedeutenden Zeitraum, in dem Daten im Vergleich zu F-RAM-Komponenten gefährdet sind. (Bildquelle: Cypress Semiconductor)

Abbildung 3: Die zusätzliche Einwirkzeit (rote Markierung) während EEPROM- oder Flash-Schreibvorgängen führt zu einem bedeutenden Zeitraum, in dem Daten im Vergleich zu F-RAM-Komponenten gefährdet sind. (Bildquelle: Cypress Semiconductor)

Um die langsameren Schreibzyklen von EEPROMs oder Flash-Speichern zu kompensieren, mussten Entwickler zur Minderung der Auswirkungen von Stromausfällen große Kondensatoren oder Batterien sowie entsprechende Spannungsregler hinzufügen, um die NVM-Versorgungsspannung bis zum Abschluss der Schreibvorgänge aufrechterhalten zu können. Im Gegensatz dazu arbeiten F-RAMs wie beispielsweise die Excelon-Auto-Komponenten von Cypress Semiconductor während den Schreibvorgängen mit Busgeschwindigkeit, wodurch der Verlust kritischer Daten enorm verringert wird und zusätzliche Spannungsquellen im Design überflüssig werden.

F-RAM-Komponenten für den Automobilbau

Die Excelon™-Auto-F-RAM-Komponenten, die von der Funktion her seriellen EEPROMs und seriellen Flash-Speichern ähneln, sind für die Anforderungen missionskritischer Anwendungen für zuverlässige und leistungsstarke NVMs ausgelegt. Die Entwickler von Systemen für die Automobiltechnik können diese Komponenten mit AEC-Q100-Zulassung verwenden, um andere Speichertypen zu ersetzen. Wählen können sie dabei zwischen den Komponenten CY15V102QN für Spannungsquellen mit 1,71 Volt bis 1,89 Volt und CY15B102QN für Spannungsquellen mit 1,8 Volt bis 3,6 Volt. Bei beiden handelt es sich um 2-Megabit-Komponenten, die als 256 KB x 8 logisch organisiert sind.

Über ihren Betriebstemperaturbereich von -40 °C bis +125 °C bieten die Excelon-F-RAMs eine Datenhaltungsdauer, die weit über die von anderen NVM-Technologien hinausgeht. Die CY15x102QN-Komponente beispielsweise kann Daten bei einer Betriebstemperatur von 85 °C geschätzt für 121 Jahre speichern. Da die Datenhaltung umgekehrt proportional zur Temperatur ist, bieten die F-RAMs eine geschätzte Datenhaltungsdauer von 35 Jahren, wenn sie am oberen Ende des typischen Temperaturbereichs von Motoren (z. B. bei 95 °C) arbeiten müssen.

In Bezug auf die Zuverlässigkeit bieten F-RAMs eine Lebensdauer von 1013 Schreibzyklen. Das sind etwa sieben Größenordnungen mehr als bei einem typischen EEPROM oder Flash-Speicher. Aus diesem Grund können Entwickler, die mit diesen F-RAM-Komponenten arbeiten, auf die Implementierung von Techniken wie Verschleißnivellierung verzichten, die Schreibvorgänge auf mehrere Sektoren verteilt, um die geringere Anzahl an Schreibzyklen im Zusammenhang mit anderen NVM-Technologien zu kompensieren.

Vereinfachtes Design mit F-RAM

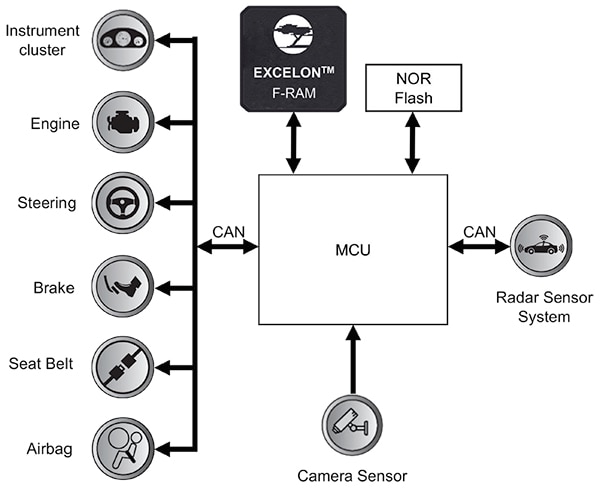

In einem typischen Design können Entwickler diese Komponenten als Ersatz für oder zur Ergänzung anderer Typen von NVM-Komponenten (z. B. eines NOR-Flash) verwenden. In einem ADAS-Design beispielsweise können Entwickler einen NOR-Flash, der zur Speicherung der Firmware verwendet wird, mit einem Excelon-F-RAM kombinieren, um die von den zahlreichen Subsystemen im Automobilbau kommenden Datenströme, die Daten für ADAS-Anwendungen liefern, zuverlässig zu verarbeiten (Abbildung 4).

Abbildung 4: Entwickler von ADAS-Designs für den Automobilbau können Excelon-F-RAM-Komponenten zur Speicherung kritischer Daten mit NOR-Flash-Komponenten kombinieren, die üblicherweise zur Speicherung von Firmware oder Konfigurationsdaten in Designs auf MCU-Basis verwendet werden. (Bildquelle: Cypress Semiconductor)

Abbildung 4: Entwickler von ADAS-Designs für den Automobilbau können Excelon-F-RAM-Komponenten zur Speicherung kritischer Daten mit NOR-Flash-Komponenten kombinieren, die üblicherweise zur Speicherung von Firmware oder Konfigurationsdaten in Designs auf MCU-Basis verwendet werden. (Bildquelle: Cypress Semiconductor)

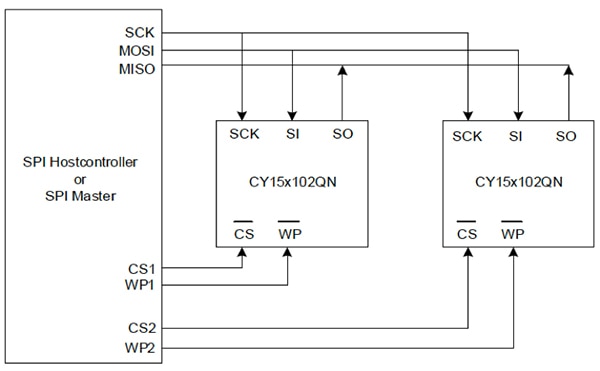

Excelon-F-RAMs können problemlos in ein Design integriert werden, indem die Entwickler sie einach mit dem SPI-Bus des Host-Prozessors verbinden. Die als SPI-Slave-Komponente konzipierten CY15x102QN-F-RAMs unterstützen SPI-Taktraten von bis zu 50 Megahertz (MHz). In einer typischen Hardwarekonfiguration verbinden Entwickler den seriellen Eingang (SI) und den seriellen Ausgang (SO) der F-RAM-Komponente mit den Leitungen MOSI (Master Out Slave In) und MISO (Master In Slave Out) des SPI-Masters. Verbindungen zu den entsprechenden Leitungen des seriellen Takts (SCK) und der Chipauswahl (/CS) runden die Hardwareschnittstelle ab. Entwickler können mehrere Komponenten kombinieren, die den SPI-Bus des Hosts dann gemeinsam verwenden (Abbildung 5).

Abbildung 5: Entwickler können einen gemeinsam genutzten SPI-Bus verwenden, um einen Host-Prozessor mit einem oder mehreren CY15x102QN-F-RAMs zu verbinden. (Bildquelle: Cypress Semiconductor)

Abbildung 5: Entwickler können einen gemeinsam genutzten SPI-Bus verwenden, um einen Host-Prozessor mit einem oder mehreren CY15x102QN-F-RAMs zu verbinden. (Bildquelle: Cypress Semiconductor)

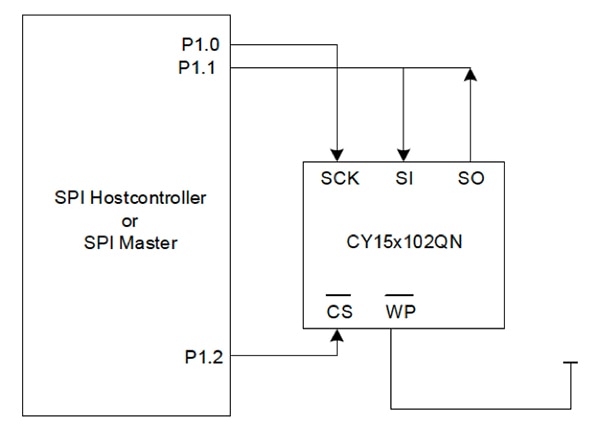

Für MCUs ohne SPI-Funktionen unterstützen die CY15x102QN-Komponenten eine einfache Alternative zur Emulierung der SPI-Hardwareschnittstelle, indem sie für die Verbindung zum F-RAM die GPIO-Pins des Mikrocontrollers verwenden. Entwickler können diese Schnittstelle über nur drei GPIO-Pins implementieren, indem sie für die SI- und SO-Datenleitungen des F-RAM denselben Pin verwenden (Abbildung 6).

Abbildung 6: Für einen Mikrocontroller ohne native SPI-Funktionen können Entwickler ganz einfach die GPIO-Pins des Mikrocontrollers verwenden, um für den Zugriff auf einen seriellen CY15x102QN-F-RAM das SPI-Protokoll zu emulieren. (Bildquelle: Cypress Semiconductor)

Abbildung 6: Für einen Mikrocontroller ohne native SPI-Funktionen können Entwickler ganz einfach die GPIO-Pins des Mikrocontrollers verwenden, um für den Zugriff auf einen seriellen CY15x102QN-F-RAM das SPI-Protokoll zu emulieren. (Bildquelle: Cypress Semiconductor)

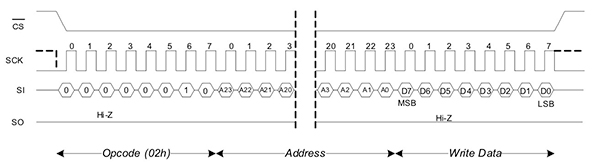

Im SPI-Standardprotokoll initiiert ein Master eine Transaktion, indem er /CS auf Low zieht. Im Anschluss daran interpretiert der F-RAM das nächste Byte als einen Opcode. So folgt beispielsweise ein Schreibvorgang auf den standardmäßigen Schreib-Opcode (02h) des SPI-Protokolls mit der 3-Byte-Adresse und Datenbytes (Abbildung 7).

Abbildung 7: Die CY15x102QN-F-RAM-Komponenten von Cypress unterstützen standardmäßige SPI-Opcodes und -Protokolle und ermöglichen Entwicklern dadurch die problemlose Durchführung von verzögerungsfreien Schreibvorgängen, indem der Schreib-Opcode (02h), die Adresse und die Daten nacheinander gesendet werden. (Bildquelle: Cypress Semiconductor)

Abbildung 7: Die CY15x102QN-F-RAM-Komponenten von Cypress unterstützen standardmäßige SPI-Opcodes und -Protokolle und ermöglichen Entwicklern dadurch die problemlose Durchführung von verzögerungsfreien Schreibvorgängen, indem der Schreib-Opcode (02h), die Adresse und die Daten nacheinander gesendet werden. (Bildquelle: Cypress Semiconductor)

Für die CY15x102QN-F-RAMs mit 2 Mbit handelt es sich bei der Adresse um eine 3-Byte-Sequenz, wobei die oberen sechs Bit ignoriert werden. Cypress empfiehlt, diese oberen sechs Bit auf den Wert Null zu setzen, um zukünftig einen einfachen Umstieg auf F-RAM-Komponenten mit höherer Kapazität zu ermöglichen

Ein Lesevorgang folgt demselben Protokoll. Nach dem Empfangen des standardmäßigen Lese-Opcodes (03h) und der Adresse überträgt die F-RAM-Komponente Datenbytes sequenziell über die SO-Leitung. Dabei wird die Speicheradresse automatisch erhöht, während /CS auf Low verbleibt und die Taktsignale weiterhin gesendet werden. Dadurch können Entwickler ganz einfach einen Massenlesevorgang durchführen, indem sie /CS auf Low belassen und weiterhin SCK-Taktsignale senden, bis die erforderliche Anzahl an Datenbytes gelesen wurde.

Die CY15x102QN-F-RAMs unterstützen außerdem eine schnelle Lesefunktion, die mit der eines seriellen Flash-Speichers kompatibel ist. Nach dem Empfangen des Opcodes für schnelles Lesen (0Bh) und der Adresse sendet der SPI-Host ein Dummy-Byte, um die Latenz des Flash-Speichers beim Lesen zu emulieren. Nach dem Empfangen des Dummy-Bytes antwortet der F-RAM mit den angeforderten Daten. Auch mit schnellen Lesevorgängen können Massenlesevorgänge durchgeführt werden, indem derselbe Mechanismus wie für standardmäßige Lesevorgänge verwendet wird.

Schreibschutz

Neben der Steuerungslogik der SPI-Schnittstelle bieten die CY15x102QN-F-RAMs weitere Mechanismen zur Identifizierung der Komponente und zur Bereitstellung eines Schreibschutzes für das F-RAM-Array.

Entwickler können SPI-Opcodes ausgeben, um auf die schreibgeschützte eindeutige ID der CY15x102QN-Komponente und die Komponenten-ID zuzugreifen, die unter anderem Informationen zu Hersteller, Speicherdichte und Bauteilversion enthalten. Außerdem können Entwickler ein 8-Byte-Lese-/Schreibregister festlegen, um einen F-RAM mit einem System oder einer Konfiguration zu verknüpfen.

Zum Schutz des F-RAM bietet die Komponente sowohl Software- als auch Hardwaremechanismen. Für den Datenschutz während der Fertigung wird ein dedizierter 256-Byte-Spezialbereich entwickelt, um für ganze drei standardmäßige Reflow-Lötzyklen die Datenintegrität aufrechtzuerhalten. Für den Schutz im Normalbetrieb verwendet die Komponente eine Verriegelung zur Schreibfreigabe, um das F-RAM-Array vor versehentlichen Schreibvorgängen zu schützen. Beim Einschalten wird diese Verriegelung standardmäßig aufgehoben. Aus diesem Grund muss der Entwickler vor der Durchführung von Schreibvorgängen den Opcode für die Schreibfreigabe (06h) ausgeben.

Im Statusregister der Komponente ermöglichen die zwei Blockschutz-Bits BP0 und BP1 den Entwicklern den Schutz des Speichers über den gesamten Adressbereich (BP1 = 1, BP0 = 1), nur in der oberen Hälfte des Speichers (BP1 = 1, BP0 = 0) oder nur im oberen Viertel des Speichers (BP 1= 0, BP0 = 1).

Mit dem Schreibschutz-Pin der Hardware (/WP) können die Entwickler verhindern, dass die Blockschutz-Bits im normalen Betrieb per Software geändert werden. Hier setzen die Entwickler das WPEN-Bit (Write Protect Enable) im Statusregister und ziehen den /WP-Pin auf Low, um das Statusregister zu sperren.

Energiemanagement

Im Normalbetrieb liegt die Leistungsaufnahme der CY15V102QN-Komponente (VDD 1,71 Volt bis 1,89 Volt) aufgrund der Energieeffizienz der F-RAM-Technologie üblicherweise bei lediglich 5,0 Milliampere (mA) für Operationen bei einer maximalen Taktrate von 50 MHz. Um die Leistungsaufnahme noch weiter zu senken, können Entwickler die Taktfrequenz verringern. Hierdurch kann die Leistungsaufnahme für die CY15V102QN-Komponente auf etwa 0,4 mA bei 1 MHz gesenkt werden. Die Leistungsaufnahme der CY15B102QN-Komponente (VDD 1,8 Volt bis 3,6 Volt) ist mit 6,0 mA bei 50 MHz und 0,5 mA bei 1 MHz nur geringfügig höher.

Bei längerer Inaktivität können Entwickler die Leistungsaufnahme erheblich senken, indem sie die CY15x102QN-Komponenten mithilfe von SPI-Opcodes in einen von drei Energiesparmodi versetzen:

- Standby-Modus: typische Leistungsaufnahme von 2,7 Mikroampere (μA) für CY15V102QN oder 3,2 μA für CY15B102QN

- Deep-Power-Down-Modus: typische Leistungsaufnahme von 1,1 μA für CY15V102QN oder 1,3 μA für CY15B102QN

- Hibernate-Modus: 0,1 μA für beide Komponenten

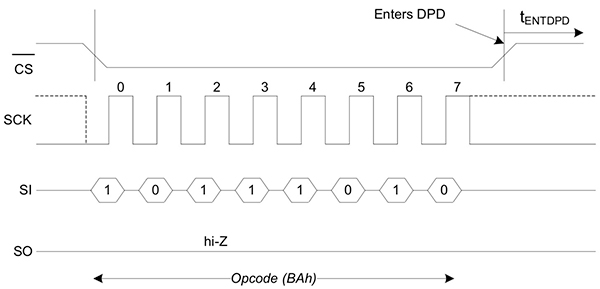

Die CY15x102QN-Komponenten schalten automatisch in den Standby-Modus, wenn der SPI-Host /CS am Ende einer Opcode-Sequenz auf High zieht. Um die Komponente in den Deep-Power-Down- oder in den Hibernate-Modus zu versetzen, nutzt der SPI-Host das SPI-Opcode-Protokoll. Im Einzelnen schaltet der SPI-Host in einen der zwei sparsamsten Energiesparmodi, indem er zuerst /CS auf Low zieht, dann einen speziellen Opcode für den Deep-Power-Down-Modus (BAh) oder den Hibernate-Modus (B9h) senden und abschließend /CS auf High zieht (Abbildung 8).

Abbildung 8: Während CY15x102QN-F-RAM-Komponenten von Cypress nach einer Opcode-Sequenz automatisch in den Standby-Modus wechseln, können Entwickler die Komponenten mit dem normalen SPI-Opcode-Verfahren in noch stromsparendere Modi wie beispielsweise den DPD-Modus (Deep Power Down) versetzen. (Bildquelle: Cypress Semiconductor)

Abbildung 8: Während CY15x102QN-F-RAM-Komponenten von Cypress nach einer Opcode-Sequenz automatisch in den Standby-Modus wechseln, können Entwickler die Komponenten mit dem normalen SPI-Opcode-Verfahren in noch stromsparendere Modi wie beispielsweise den DPD-Modus (Deep Power Down) versetzen. (Bildquelle: Cypress Semiconductor)

Wenn der SPI-Host /CS auf High zieht, nachdem der Opcode für einen Energiesparmodus gesendet wurde, wechselt die CY15x102QN-F-RAM-Komponente innerhalb von etwa 3 μs in den entsprechenden Energiesparmodus.

Aus dem Standby-Modus wechseln die F-RAMs von Cypress umgehend in den aktiven Modus, sobald /CS auf Low gezogen wird, um die nächste Opcode-Sequenz zu initiieren. Aus dem Deep-Power-Down- oder dem Hibernate-Modus wechseln die F-RAMs ebenfalls in den aktiven Modus, nachdem /CS auf Low gezogen wurde, allerdings mit einer kurzen Verzögerung von etwa 10 μs für den Deep-Power-Down-Modus bzw. 450 μs für den Hibernate-Modus.

Fazit

Zuverlässige, schnelle, energieeffiziente und leistungsstarke NVMs gewinnen immer mehr an Bedeutung für eine Vielzahl von Anwendungen, die auf Daten von einer stetig wachsenden Anzahl an Sensoren abhängig sind. In missionskritischen Bereichen, beispielsweise in ADAS-Anwendungen im Automobilbau, können Datenverluste die Sicherheitsmechanismen zum Schutz von Fahrzeug und Insassen erheblich beeinträchtigen.

Mit F-RAM-Komponenten von Cypress Semiconductor können Entwickler ganz einfach NVMs integrieren, die kritische Daten über Jahrzehnte hinweg zuverlässig speichern können, ohne dafür Abstriche hinsichtlich Leistung oder Leistungsaufnahme machen zu müssen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.