Nutzen Sie den schnellen FPGA-Weg zum Aufbau leistungsfähiger, energieeffizienter KI-Anwendungen am Netzwerkrand

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2021-01-12

Entwickler, die Algorithmen für künstliche Intelligenz (KI) auf Inferenzprozessoren am Netzwerkrand (Edge) implementieren möchten, stehen unter ständigem Druck, den Stromverbrauch und die Entwicklungszeit zu senken, auch wenn die Anforderungen an die Verarbeitung steigen. FPGAs (Field Programmable Gate Arrays, feldprogrammierte Gatter-Arrays) bieten eine besonders effektive Kombination aus Geschwindigkeit und Leistungseffizienz für die Implementierung der für KI am Netzwerkrand erforderlichen Inferenz-Engines für neuronale Netzwerke (NN). Für Entwickler, die mit FPGAs nicht vertraut sind, können konventionelle FPGA-Entwicklungsmethoden jedoch komplex erscheinen, was Entwickler oft dazu veranlasst, sich weniger optimalen Lösungen zuzuwenden.

Dieser Artikel beschreibt einen einfacheren Ansatz von Microchip Technology, der es Entwicklern ermöglicht, die herkömmliche FPGA-Entwicklung zu umgehen und trainierte NNs mit FPGAs und einem Software-Entwicklungskit (SDK, Software Development Kit) zu erstellen oder ein FPGA-basiertes Video-Kit zu verwenden, um sofort in die Entwicklung intelligenter eingebettete Bildverarbeitungsanwendungen einzusteigen.

Warum KI am Netzwerkrand einsetzen?

Edge-Computing (Datenverarbeitung am Netzwerkrand) bringt eine Reihe von Vorteilen für IoT-Anwendungen (Internet of Things, Internet der Dinge) in so unterschiedlichen Segmenten wie industrielle Automatisierung, Sicherheitssysteme, Smart Homes und mehr. In einer industriellen IoT-Anwendung (IIoT), die auf die Fabrikhalle abzielt, kann Edge-Computing die Reaktionszeit in Prozesssteuerungsschleifen dramatisch verbessern, indem es Roundtrip-Verzögerungen zu Cloud-basierten Anwendungen eliminiert. In ähnlicher Weise kann ein Edge-basiertes Sicherheitssystem oder ein Smart-Home-Türschloss auch dann weiter funktionieren, wenn die Verbindung zur Cloud versehentlich oder absichtlich unterbrochen wird. In vielen Fällen kann der Einsatz von Edge-Computing in einer dieser Anwendungen dazu beitragen, die Gesamtbetriebskosten zu senken, indem die Abhängigkeit des Produkts von Cloud-Ressourcen reduziert wird. Anstatt mit einem unerwarteten Bedarf an zusätzlichen teuren Cloud-Ressourcen konfrontiert zu werden, wenn die Nachfrage nach ihren Produkten steigt, können sich die Entwickler auf die in ihre Produkte integrierten lokalen Verarbeitungsfunktionen verlassen und so die Betriebskosten stabiler halten.

Die schnelle Akzeptanz und die steigende Nachfrage nach Inferenzmodellen des maschinellen Lernens (ML) verstärken die Bedeutung des Edge-Computing dramatisch. Dem Entwickler hilft die lokale Verarbeitung von Inferenzmodellen, die Antwortlatenz und die Kosten für Cloud-Ressourcen zu reduzieren, die für cloudbasierte Inferenz erforderlich sind. Für die Anwender bedeutet die Verwendung lokaler Inferenzmodelle die Gewissheit, dass ihre Produkte auch bei gelegentlichem Verlust der Internetverbindung oder bei Änderungen an den cloudbasierten Angeboten des Produktanbieters weiterhin funktionieren. Darüber hinaus können Bedenken hinsichtlich der Sicherheit und des Datenschutzes den Bedarf an lokaler Verarbeitung und Inferenz weiter vorantreiben, um die Menge an sensiblen Informationen zu begrenzen, die über das öffentliche Internet in die Cloud übertragen werden.

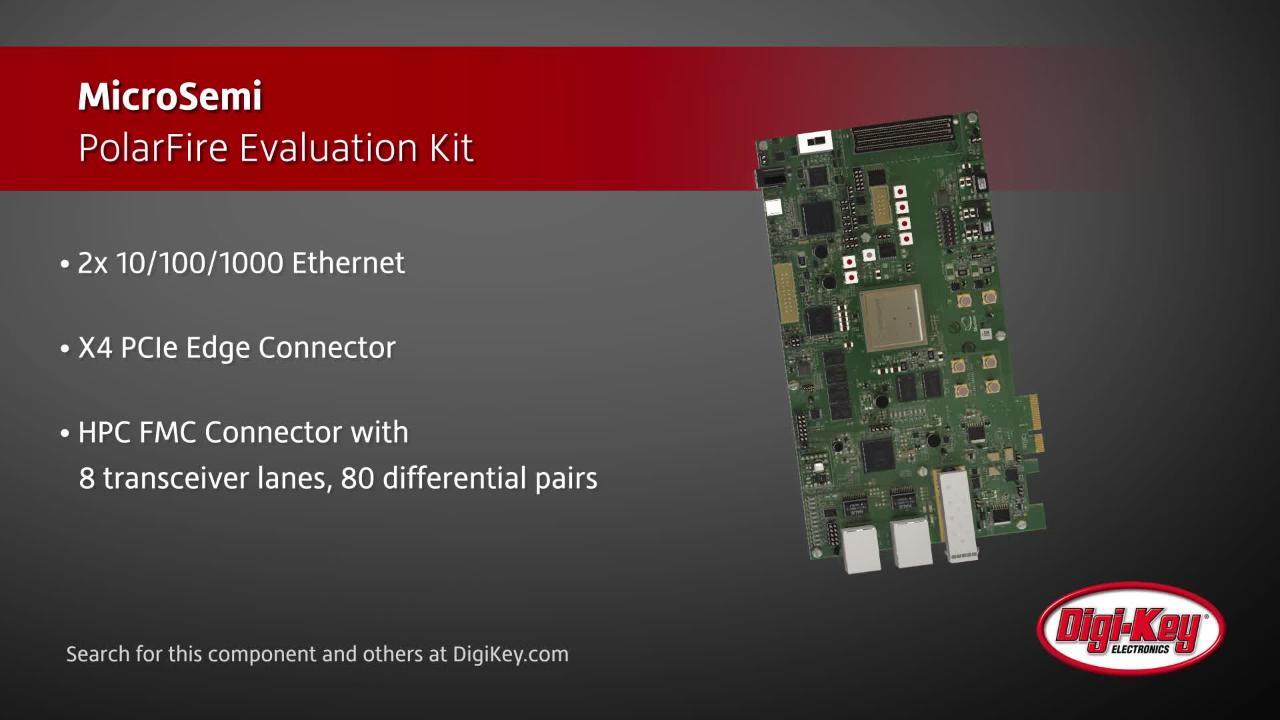

Die Entwicklung eines NN-Inferenzmodells für die bildverarbeitungsbasierte Objekterkennung ist ein mehrstufiger Prozess, der mit dem Modelltraining beginnt, das typischerweise auf einem ML-Framework wie TensorFlow unter Verwendung öffentlich verfügbarer gelabelter Bilder oder benutzerdefinierter gelabelter Bilder durchgeführt wird. Aufgrund der hohen Anforderungen an die Verarbeitung wird das Modelltraining in der Regel mit Grafikprozessoren (GPUs) in der Cloud oder einer anderen Hochleistungs-Computerplattform durchgeführt. Nach Abschluss des Trainings wird das Modell in ein Inferenzmodell umgewandelt, das auf Edge- oder Fog-Computing-Ressourcen ausgeführt werden kann und die Inferenzergebnisse als einen Satz von Objektklassenwahrscheinlichkeiten liefert (Abbildung 1).

Abbildung 1: Die Implementierung eines Inferenzmodells für Edge-KI steht am Ende eines mehrstufigen Prozesses, der das Training und die Optimierung von NNs auf Frameworks mit verfügbaren oder eigenen Trainingsdaten erfordert. (Bildquelle: Microchip Technology)

Abbildung 1: Die Implementierung eines Inferenzmodells für Edge-KI steht am Ende eines mehrstufigen Prozesses, der das Training und die Optimierung von NNs auf Frameworks mit verfügbaren oder eigenen Trainingsdaten erfordert. (Bildquelle: Microchip Technology)

Warum Inferenzmodelle rechnerisch anspruchsvoll sind

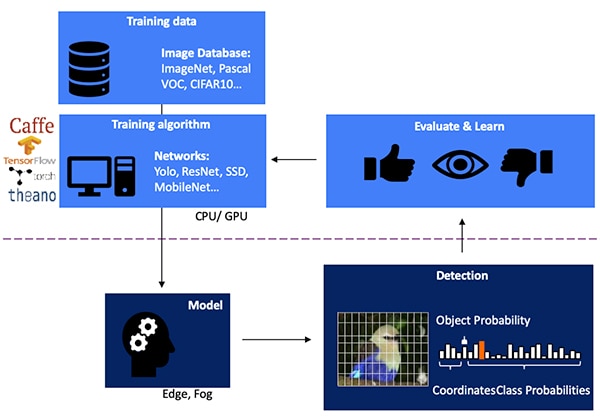

Obwohl die Größe und Komplexität im Vergleich zu dem während des Trainingsprozesses verwendeten Modell reduziert ist, stellt ein NN-Inferenzmodell aufgrund der großen Anzahl der erforderlichen Berechnungen immer noch eine rechnerische Herausforderung für Allzweckprozessoren dar. In seiner allgemeinen Form besteht ein tiefes NN-Modell aus mehreren Schichten von Neuronensätzen. Innerhalb jeder Schicht in einem vollständig verbundenen Netzwerk muss jedes Neuron nij die Summe der Produkte jeder Eingabe mit einem zugehörigen Gewichtungsfaktor wij berechnen (Abbildung 2).

Abbildung 2: Die Anzahl der Berechnungen, die für die Inferenz mit einem NN erforderlich sind, kann einen erheblichen Rechenaufwand bedeuten. (Bildquelle: Microchip Technology)

Abbildung 2: Die Anzahl der Berechnungen, die für die Inferenz mit einem NN erforderlich sind, kann einen erheblichen Rechenaufwand bedeuten. (Bildquelle: Microchip Technology)

In Abbildung 2 nicht dargestellt ist der zusätzliche Rechenaufwand, der durch die Aktivierungsfunktion entsteht, die die Ausgabe jedes Neurons modifiziert, indem sie negative Werte auf Null abbildet, Werte größer als 1 auf 1 abbildet und ähnliche Funktionen. Die Ausgabe der Aktivierungsfunktion für jedes Neuron nij dient als Eingabe für die nächste Schicht i+1, und so geht es für jede Schicht weiter. Schließlich erzeugt die Ausgabeschicht des NN-Modells einen Ausgabevektor, der die Wahrscheinlichkeit darstellt, dass der ursprüngliche Eingabevektor (oder die Matrix) einer der Klassen (oder Labels) entspricht, die während des überwachten Lernprozesses verwendet wurden.

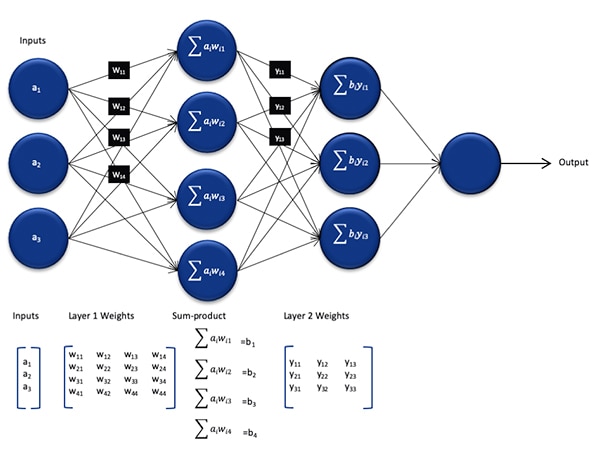

Effektive NN-Modelle werden mit Architekturen gebaut, die viel größer und komplexer sind als die oben gezeigte repräsentative generische NN-Architektur. Ein typisches Faltungs-NN (CNN), das für die Erkennung von Bildobjekten verwendet wird, wendet diese Prinzipien stückweise an, indem es die Breite, Höhe und Farbtiefe eines Eingabebildes abtastet, um eine Reihe von Merkmalskarten zu erzeugen, die schließlich den Ausgabevorhersagevektor ergeben (Abbildung 3).

Abbildung 3: CNNs, die für die Erkennung von Bildobjekten verwendet werden, beinhalten eine große Anzahl von Neuronen in vielen Schichten, was eine höhere Anforderung an die Rechenplattform stellt. (Bildquelle: Aphex34 CC BY-SA 4.0)

Abbildung 3: CNNs, die für die Erkennung von Bildobjekten verwendet werden, beinhalten eine große Anzahl von Neuronen in vielen Schichten, was eine höhere Anforderung an die Rechenplattform stellt. (Bildquelle: Aphex34 CC BY-SA 4.0)

Einsatz von FPGAs zur Beschleunigung von NN-Mathematik

Obwohl eine Reihe von Optionen für die Ausführung von Inferenzmodellen am Netzwerkrand auftauchen, bieten nur wenige Alternativen eine optimale Mischung aus Flexibilität, Leistung und Energieeffizienz, die für praktische Hochgeschwindigkeitsinferenz am Netzwerkrand benötigt wird. Unter den leicht verfügbaren Alternativen für Edge-KI sind FPGAs besonders effektiv, da sie eine hochperformante hardwarebasierte Ausführung rechenintensiver Operationen bei relativ geringem Stromverbrauch bieten können.

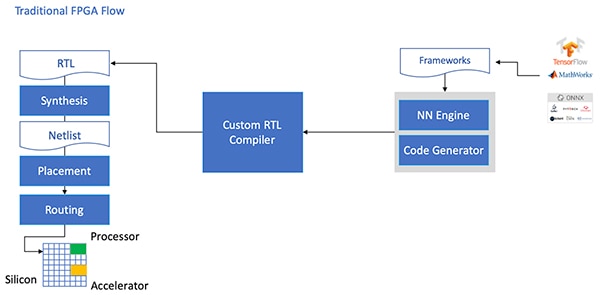

Trotz ihrer Vorteile werden FPGAs manchmal aufgrund eines traditionellen Entwicklungsablaufs umgangen, der für Entwickler ohne umfangreiche FPGA-Erfahrung entmutigend sein kann. Um eine effektive FPGA-Implementierung eines NN-Modells zu erstellen, das von einem NN-Framework generiert wurde, muss der Entwickler die Feinheiten der Konvertierung des Modells in die Registertransfersprache (RTL), die Synthese des Designs und die abschließende Place-and-Route-Phase des physikalischen Designs verstehen, um eine optimierte Implementierung zu erzeugen (Abbildung 4).

Abbildung 4: Um ein NN-Modell auf einem FPGA zu implementieren, mussten Entwickler bisher verstehen, wie sie ihre Modelle in RTL umwandeln und den traditionellen FPGA-Ablauf durchlaufen. (Bildquelle: Microchip Technology)

Abbildung 4: Um ein NN-Modell auf einem FPGA zu implementieren, mussten Entwickler bisher verstehen, wie sie ihre Modelle in RTL umwandeln und den traditionellen FPGA-Ablauf durchlaufen. (Bildquelle: Microchip Technology)

Mit den PolarFire-FPGAs, spezieller Software und zugehörigem geistigen Eigentum (IP) bietet Microchip Technology eine Lösung, die hochleistungsfähige, stromsparende Inferenz am Rande des Netzwerks auch für Entwickler ohne FPGA-Erfahrung breit verfügbar macht.

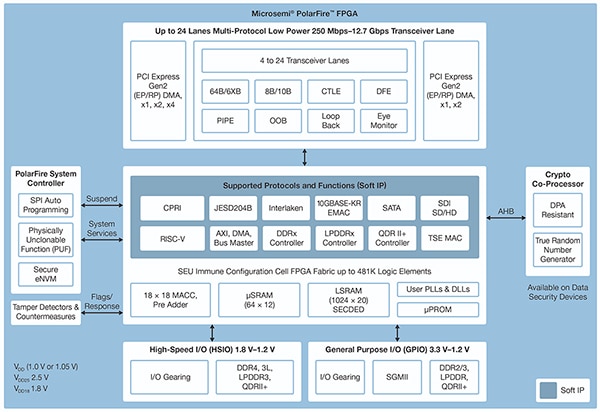

Die in einer fortschrittlichen, nichtflüchtigen Prozesstechnologie gefertigten PolarFire-FPGAs wurden entwickelt, um die Flexibilität und Leistung zu maximieren und gleichzeitig die Leistungsaufnahme zu minimieren. Neben einem umfangreichen Array von Hochgeschwindigkeitsschnittstellen für Kommunikation und Ein-/Ausgabe (I/O) verfügen sie über eine tiefe FPGA-Struktur, die in der Lage ist, erweiterte Funktionalität unter Verwendung von Soft-IP-Cores zu unterstützen, darunter RISC-V-Prozessoren, fortschrittliche Speicher-Controller und andere Standard-Schnittstellen-Subsysteme (Abbildung 5).

Abbildung 5: Die PolarFire-Architektur von Microchip Technology bietet eine tiefe Struktur, die zur Unterstützung von Hochleistungs-Designanforderungen einschließlich rechenintensiver Inferenzmodell-Implementierung entwickelt wurde. (Bildquelle: Microchip Technology)

Abbildung 5: Die PolarFire-Architektur von Microchip Technology bietet eine tiefe Struktur, die zur Unterstützung von Hochleistungs-Designanforderungen einschließlich rechenintensiver Inferenzmodell-Implementierung entwickelt wurde. (Bildquelle: Microchip Technology)

Die PolarFire-FPGA-Struktur bietet einen umfangreichen Satz an Logikelementen und spezialisierten Blöcken, die in einer Reihe von Kapazitäten von verschiedenen Mitgliedern der PolarFire-FPGA-Familie unterstützt werden, einschließlich der Serien MPF100T, MPF200T, MPF300T und MPF500T (Tabelle 1).

|

Tabelle 1: Eine Vielzahl von FPGA-Struktur-Funktionen und Kapazitäten sind in der PolarFire-Serie verfügbar. (Quelle der Tabelle: DigiKey, basierend auf dem PolarFire-Datenblatt von Microchip Technology)

Zu den Funktionen, die für die Inferenzbeschleunigung von besonderem Interesse sind, gehört in der PolarFire-Architektur ein dedizierter Mathematikblock, der eine vorzeichenbehaftete 18 Bit × 18 Bit Multiplikations-Akkumulations-Funktion (MAC) mit einem Voraddierer bereitstellt. Ein eingebauter Punktproduktmodus verwendet einen einzigen Mathematikblock, um zwei 8-Bit-Multiplikationsoperationen durchzuführen und bietet so einen Mechanismus zur Erhöhung der Kapazität, indem die vernachlässigbaren Auswirkungen der Modellquantisierung auf die Genauigkeit genutzt werden.

Zusätzlich zur Beschleunigung der mathematischen Operationen hilft die PolarFire-Architektur, die Art von Speicherüberlastung zu vermeiden, die bei der Implementierung von Inferenzmodellen auf Mehrzweckarchitekturen auftritt, wie z. B. kleine verteilte Speicher für die Speicherung von Zwischenergebnissen, die während der Ausführung des NN-Algorithmus erzeugt werden. Außerdem können die Gewichtungen und Bias-Werte eines NN-Modells in einem 16 mal 18 Bit tiefen Koeffizienten-Festwertspeicher (ROM) gespeichert werden, der aus Logikelementen in der Nähe des Mathematikblocks besteht.

In Kombination mit anderen Merkmalen der PolarFire-FPGA-Struktur bilden die Mathematikblöcke die Grundlage für die höherwertige CoreVectorBlox-IP von Microchip Technology. Dies dient als flexible NN-Engine, die verschiedene Typen von NNs ausführen kann. Neben einer Reihe von Steuerregistern umfasst die CoreVectorBlox-IP drei Hauptfunktionsblöcke:

- Mikrocontroller: Ein einfacher RISC-V-Softprozessor, der die Microchip-Firmware „Binary Large Object“ (BLOB) und die benutzerspezifische NN-BLOB-Datei aus dem externen Speicher liest. Er steuert den gesamten CoreVectorBlox-Betrieb, indem er Anweisungen aus dem Firmware-BLOB ausführt.

- Matrix-Prozessor (MXP): Ein Softprozessor, der acht 32-Bit-Arithmetik-Logikeinheiten (ALUs) umfasst und für die Durchführung paralleler Operationen auf Datenvektoren unter Verwendung von elementweisen Tensoroperationen, einschließlich add, sub, xor, shift, mul, dotprod und anderen, unter Verwendung gemischter 8-Bit-, 16-Bit- und 32-Bit-Präzision, je nach Bedarf, ausgelegt ist.

- CNN-Beschleuniger: Beschleunigt MXP-Operationen unter Verwendung eines zweidimensionalen Arrays von MAC-Funktionen, die mit Mathematikblöcken implementiert sind und mit 8-Bit-Präzision arbeiten.

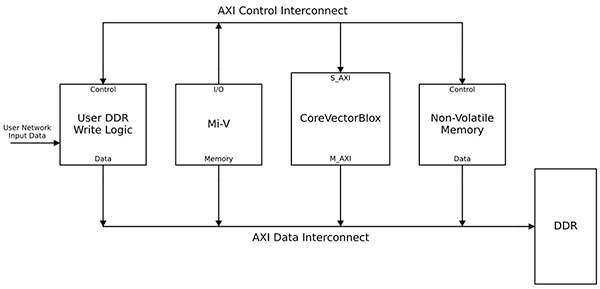

Ein komplettes NN-Verarbeitungssystem würde einen CoreVectorBlox-IP-Block, Speicher, Speicher-Controller und einen Host-Prozessor, wie z. B. den Microsoft RISC-V (Mi-V) Software-Prozessorkern, kombinieren (Abbildung 6).

Abbildung 6: Der CoreVectorBlox-IP-Block arbeitet mit einem Host-Prozessor wie dem Mi-V-RISC-V-Mikrocontroller von Microchip, um ein NN-Inferenzmodell zu implementieren. (Bildquelle: Microchip Technology)

Abbildung 6: Der CoreVectorBlox-IP-Block arbeitet mit einem Host-Prozessor wie dem Mi-V-RISC-V-Mikrocontroller von Microchip, um ein NN-Inferenzmodell zu implementieren. (Bildquelle: Microchip Technology)

In einer Videosystem-Implementierung würde der Host-Prozessor die Firmware- und Netzwerk-BLOBs aus dem System-Flash-Speicher laden und in den DDR-RAM (Double Data Rate Random Access Memory) zur Verwendung durch den CoreVectorBlox-Block kopieren. Wenn Videobilder ankommen, schreibt der Host-Prozessor sie in den DDR-RAM und signalisiert dem CoreVectorBlox-Block, mit der Verarbeitung des Bildes zu beginnen. Nach der Ausführung des im Netzwerk-BLOB definierten Inferenzmodells schreibt der CoreVectorBlox-Block die Ergebnisse, einschließlich der Bildklassifizierung, zur Verwendung durch die Zielanwendung zurück ins DDR-RAM.

Entwicklungsablauf vereinfacht NN-FPGA-Implementierung

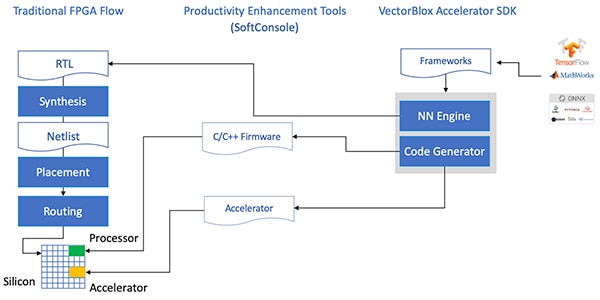

Microchip schirmt Entwickler von der Komplexität der Implementierung eines NN-Inferenzmodells auf PolarFire-FPGAs ab. Anstatt sich mit den Details der traditionellen FPGA-Abarbeitung zu beschäftigen, arbeiten NN-Modellentwickler wie gewohnt mit ihren NN-Frameworks und laden das resultierende Modell in das VectorBlox Accelerator Software Development Kit (SDK) von Microchip Technology. Das SDK generiert den erforderlichen Satz von Dateien, einschließlich derjenigen, die für den normalen FPGA-Entwicklungsablauf benötigt werden, sowie die bereits erwähnten Firmware- und Netzwerk-BLOB-Dateien (Abbildung 7).

Abbildung 7: Das VectorBlox Accelerator SDK verwaltet die Details der Implementierung eines NN-Modells auf einem FPGA und generiert automatisch Dateien, die für das Design und die Ausführung des FPGA-basierten Inferenzmodells benötigt werden. (Bildquelle: Microchip Technology)

Abbildung 7: Das VectorBlox Accelerator SDK verwaltet die Details der Implementierung eines NN-Modells auf einem FPGA und generiert automatisch Dateien, die für das Design und die Ausführung des FPGA-basierten Inferenzmodells benötigt werden. (Bildquelle: Microchip Technology)

Da der VectorBlox-Accelerator-SDK-Ablauf das NN-Design auf die im FPGA implementierte NN-Engine überlagert, können verschiedene NNs auf demselben FPGA-Design laufen, ohne dass der FPGA-Design-Synthese-Prozess erneut durchgeführt werden muss. Entwickler erstellen C/C++-Code für das resultierende System und sind in der Lage, Modelle innerhalb des Systems "on the fly" umzuschalten oder mit Hilfe von Zeitscheiben Modelle gleichzeitig laufen zu lassen.

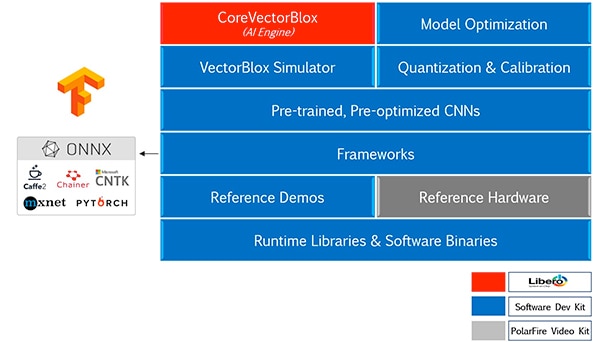

Das VectorBlox Accelerator SDK verbindet die Libero-FPGA-Design-Suite von Microchip Technology mit einem umfassenden Satz an Funktionen für die Entwicklung von NN-Inferenzmodellen. Neben den Diensten zur Modelloptimierung, Quantisierung und Kalibrierung bietet das SDK einen NN-Simulator, mit dem Entwickler dieselben BLOB-Dateien verwenden können, um ihr Modell vor der Verwendung in der FPGA-Hardwareimplementierung zu evaluieren (Abbildung 8).

Abbildung 8: Das VectorBlox Accelerator SDK bietet einen umfassenden Satz von Diensten zur Optimierung der FPGA-Implementierung von Framework-generierten Inferenzmodellen. (Bildquelle: Microchip Technology)

Abbildung 8: Das VectorBlox Accelerator SDK bietet einen umfassenden Satz von Diensten zur Optimierung der FPGA-Implementierung von Framework-generierten Inferenzmodellen. (Bildquelle: Microchip Technology)

Das VectorBlox Accelerator SDK unterstützt Modelle im ONNX-Format (Open Neural Network Exchange) sowie Modelle aus einer Reihe von Frameworks wie TensorFlow, Caffe, Chainer, PyTorch und MXNET. Unterstützte CNN-Architekturen sind MNIST, MobileNet-Versionen, ResNet-50, Tiny Yolo V2 und Tiny Yolo V3. Microchip arbeitet daran, die Unterstützung zu erweitern, um die meisten Netzwerke im quelloffenen Modell-Zoo des OpenVINO-Toolkits mit vortrainierten Modellen einzuschließen, darunter Yolo V3, Yolo V4, RetinaNet und SSD-MobileNet, neben vielen anderen.

Video-Kit demonstriert FPGA-Inferenz

Um Entwicklern den schnellen Einstieg in die Entwicklung intelligenter eingebetteter Bildverarbeitungsanwendungen zu erleichtern, stellt Microchip Technology eine umfassende Beispielanwendung zur Verfügung, die auf dem PolarFire-FPGA-Video- und -Bildverarbeitungskit und Referenzdesign MPF300-VIDEO-KIT des Unternehmens läuft.

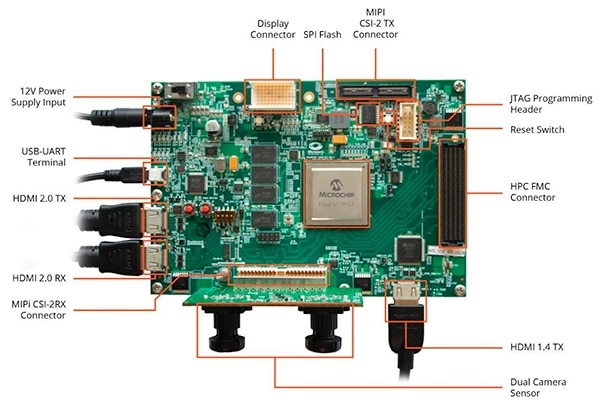

Das auf dem PolarFire-FPGA MPF300T von Microchip basierende Board des Kits kombiniert einen Dual-Kamera-Sensor, DDR4-RAM (Double Data Rate 4), Flash-Speicher, Energiemanagement und eine Vielzahl von Schnittstellen (Abbildung 9).

Abbildung 9: Das PolarFire-FPGA-Video- und -Bildverarbeitungskit MPF300-VIDEO-KIT und die zugehörige Software bieten Entwicklern einen schnellen Einstieg in die FPGA-basierte Inferenz in intelligenten eingebetteten Bildverarbeitungsanwendungen. (Bildquelle: Microchip Technology)

Abbildung 9: Das PolarFire-FPGA-Video- und -Bildverarbeitungskit MPF300-VIDEO-KIT und die zugehörige Software bieten Entwicklern einen schnellen Einstieg in die FPGA-basierte Inferenz in intelligenten eingebetteten Bildverarbeitungsanwendungen. (Bildquelle: Microchip Technology)

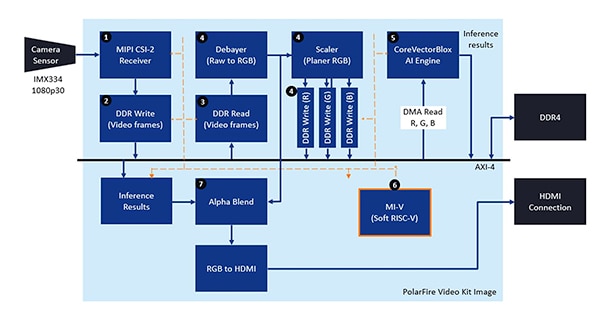

Das Kit enthält ein komplettes Libero-Designprojekt, mit dem die Firmware und die Netzwerk-BLOB-Dateien erzeugt werden. Nach der Programmierung der BLOB-Dateien in den On-Board-Flash-Speicher klicken die Entwickler auf die Schaltfläche „Ausführen“ in Libero, um die Demonstration zu starten, die Videobilder vom Kamerasensor verarbeitet und Inferenzergebnisse auf einem Display anzeigt (Abbildung 10).

Abbildung 10: Das PolarFire-FPGA-Video- und -Bildverarbeitungskit von Microchip Technology zeigt, wie eine FPGA-Implementierung eines intelligenten eingebetteten Bildverarbeitungssystems, das auf der CoreVectorBlox-NN-Engine von Microchip aufbaut, entworfen und verwendet wird. (Bildquelle: Microchip Technology)

Abbildung 10: Das PolarFire-FPGA-Video- und -Bildverarbeitungskit von Microchip Technology zeigt, wie eine FPGA-Implementierung eines intelligenten eingebetteten Bildverarbeitungssystems, das auf der CoreVectorBlox-NN-Engine von Microchip aufbaut, entworfen und verwendet wird. (Bildquelle: Microchip Technology)

Für jedes Eingangs-Videobild führt das FPGA-basierte System die folgenden Schritte aus (wobei die Schrittnummern mit Abbildung 10 korrelieren):

- Laden eines Frames von der Kamera

- Speichern des Frames im RAM

- Lesen des Frames aus dem RAM

- Konvertieren des Rohbilds in RGB, glätten von RGB und speichert des Ergebnisses im RAM

- Der Mi-V-Soft-RISC-V-Prozessor startet die CoreVectorBlox-Engine, die das Bild aus dem RAM abruft, eine Inferenz durchführt und die Ergebnisse der Klassifizierungswahrscheinlichkeit wieder im RAM speichert

- Der Mi-V erstellt aus den Ergebnissen einen Überlagerungsframe mit Boundingboxen, Klassifizierungsergebnissen und anderen Metadaten und speichert den Frame im RAM

- Der Originalframe wird mit dem Überlagerungsframe gemischt und auf das HDMI-Display geschrieben

Die Demonstration unterstützt die Beschleunigung von Tiny-Yolo-V3- und MobileNet-V2-Modellen, aber Entwickler können auch andere vom SDK unterstützte Modelle mit den zuvor beschriebenen Methoden ausführen, indem sie eine kleine Codeänderung vornehmen, um den Modellnamen und die Metadaten zu der vorhandenen Liste mit den beiden Standardmodellen hinzuzufügen.

Fazit

KI-Algorithmen wie NN-Modelle stellen typischerweise rechenintensive Prozesse dar, die robustere Rechenressourcen erfordern, als sie bei Allzweckprozessoren verfügbar sind. Für Entwickler, die mit FPGAs nicht vertraut sind, können konventionelle FPGA-Entwicklungsmethoden jedoch komplex erscheinen, was Entwickler oft dazu veranlasst, sich weniger optimalen Lösungen zuzuwenden.

Wie gezeigt, können Entwickler ohne FPGA-Erfahrung mit Hilfe von spezieller IP und Software von Microchip Technology inferenzbasierte Designs implementieren, die die Anforderungen an Leistung, Stromverbrauch und Design-Zeitplan besser erfüllen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.