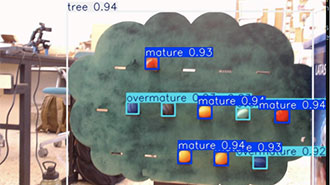

From Webcam to Cloud: Building an IoT-Ready Computer Vision System

From Webcam to Cloud: Building an IoT-Ready Computer Vision System

Use a laptop webcam, OpenCV, YOLOv8, and MQTT to detect objects in real time and publish events to the cloud. Code and setup included.

This video discusses the Infineon PSOC Edge MCUs, designed to deliver powerful compute, AI acceleration, and strong security for edge devices.

Faster printf Debugging (Part 3)

Faster printf Debugging (Part 3)

Learn serialization and COBS framing to send debug logs at lightning speed from STM32 boards. Compare MessagePack, FlatBuffers, & bitproto for fast debug output.

EDR Compliance for UNECE R169 with iWave Telematics Solutions

EDR Compliance for UNECE R169 with iWave Telematics Solutions

As commercial vehicles become increasingly connected and automated, the ability to record, store, and analyze driving data is more important than ever.

Learn how our PolarFire® Core FPGAs and SoC FPGAs bring power savings and design simplicity to intelligent edge applications, without compromising performance or reliability.

Intro to ROS Part 5: Services, Requests, and Responses with Python

Intro to ROS Part 5: Services, Requests, and Responses with Python

In this tutorial, we will see how services work by creating a custom server and client in Python ROS nodes.

Renesas RA8M2 and RA8D2 MCU feature Arm® Cortex®-M85 and Cortex-M33 cores deliver breakthrough performance that meets demanding application needs.

STSAFL010DFSPL01 Secure Authentication Element for Consumables and Peripherals

Datum der Veröffentlichung: 2025-10-23

STSAFL010DFSPL01 Secure Authentication Element for Consumables and Peripherals

Datum der Veröffentlichung: 2025-10-23

The STSAFL010DFSPL01 secure system-on-chip from STMicroelectronics is designed to provide authentication and data management services to a local host.

Faster printf Debugging (Part 2)

Faster printf Debugging (Part 2)

Learn non-blocking UART and USB tricks to slash printf debug times on STM32 boards. Speed up embedded logging with interrupts, DMA, and smart buffering.

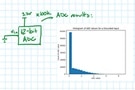

Can an ADC Be Just a Random Number Generator?

Datum der Veröffentlichung: 2025-10-22

Can an ADC Be Just a Random Number Generator?

Datum der Veröffentlichung: 2025-10-22

A 16-bit ADC will not always give 16-bits of useful information. A lot of 16-bit ADCs really operate as 7-bit ADCs and 9-bit random number generators.

Experience real-time AI acceleration on iWave’s iW-RainboW-G57D Versal VE2302 SoM with Mipsology Stack integration. Achieve high-performance, power efficient, low-latency edge inference and seamless AI model deployment using AMD’s Vitis AI platform.

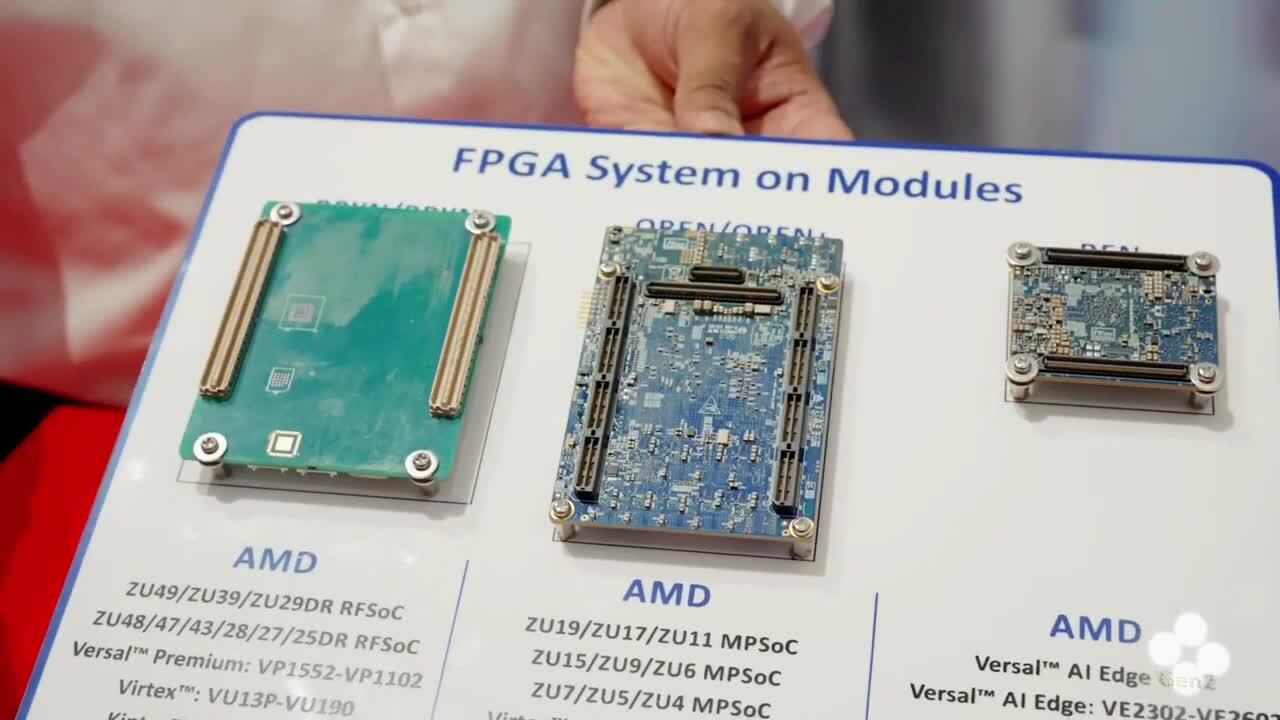

Discover iWave’s high-performance SmartNIC solutions powered by Altera Agilex 7, AMD Zynq UltraScale+ MPSoC & RFSoC, and Achronix Speedster7t FPGAs enabling low-latency, AI-driven, and high-speed networking for data centers and edge applications.

Join iWave and DigiKey at Embedded World 2025 as Mr. Tawfeeq Ahmad from iWave discuss with Paige West from ES, FPGA System on Modules, AI, and networking trends, and how FPGA technology is transforming industries.

Extrem energiesparender 32-MHz-Einstiegsmikrocontroller RA0L1 auf Basis des Arm® Cortex®-M23

Datum der Veröffentlichung: 2025-10-21

Extrem energiesparender 32-MHz-Einstiegsmikrocontroller RA0L1 auf Basis des Arm® Cortex®-M23

Datum der Veröffentlichung: 2025-10-21

Der Mikrocontroller RA0L1 von Renesas bietet eine kapazitive Touch-Funktion und ein Peripheriedesign für einen optimierten Materialaufwand.

MYIR's MYD-LR3576 Development Board centered around the MYC-LR3576 SOM and a base board, offering a complete evaluation platform for the Rockchip RK3576 (J) Processor based on 2.2 GHz Quad Cortex-A72 Cores and 1.8 GHz Quad Cortex-A53 Cores.

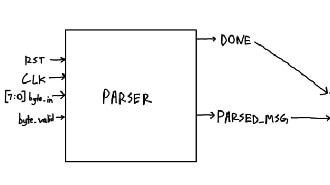

ITCH Parser Design in SystemVerilog

ITCH Parser Design in SystemVerilog

Learn how to design and simulate an ITCH protocol parser in SystemVerilog for FPGAs. Explore the intersection of FPGA design and finance.

Pi Vision 10.1 CM5 von SECO, die professionelle Touch-Display-Plattform für Entwickler und Unternehmen, wird mit einer kostenlosen Clea-Testversion für 90 Tage vollen Zugriff auf alle Funktionen geliefert.

Das Entwicklungskit DE23-Lite von Terasic Inc. ist für eingebettete Bildverarbeitungs-, digitale Logik- und Robotik-Anwendungen konzipiert.

RZ/G2 Series SoM with Arm® Cortex®-A57 Cores up to 1.5 GHz

Datum der Veröffentlichung: 2025-10-17

RZ/G2 Series SoM with Arm® Cortex®-A57 Cores up to 1.5 GHz

Datum der Veröffentlichung: 2025-10-17

Renesas RZ/G2 series SoM with Arm® Cortex®-A57 cores up to 1.5 GHz feature up to seven 500 Mpix/s video signal processors (VSP).

Intro to ROS Part 4: Nodes, Topics, Publishers, and Subscribers (C++)

Intro to ROS Part 4: Nodes, Topics, Publishers, and Subscribers (C++)

In this tutorial, we’ll walk through how to write ROS 2 nodes in C++ that communicate using the publish/subscribe model.