Die Lieferung von Bestellungen nach Schweiz erfolgt je nach Bestimmungsort normalerweise innerhalb von 48 Stunden.

Kostenlose Lieferung nach Schweiz für Bestellungen im Wert von 54 CHF oder mehr. Für Bestellungen im Wert von unter 54 CHF werden Versandkosten in Höhe von 20 CHF berechnet.

UPS, FedEx- oder DHL-Fracht im Voraus bezahlt: DDP (Zoll- und Einfuhrgebühren bezahlt von DigiKey)

Rechnungskonto für qualifizierte Institutionen und Unternehmen

Vorauszahlung per Banküberweisung

![]()

![]()

![]()

![]()

Weitere Produkte von vollständig autorisierten Partnern

Die durchschnittliche Dauer bis zum Versand beträgt 1-3 Tage; es können zusätzliche Versandgebühren anfallen. Die tatsächliche Lieferzeit entnehmen Sie bitte der Produktseite, dem Warenkorb und der Kasse.

Incoterms: CPT (Zoll und anwendbare Mehrwertsteuer/Steuer fällig zum Zeitpunkt der Lieferung)

Weitere Informationen erhalten Sie über Hilfe und Kundendienst

Embark on your FPGA journey with the iCE40 Calculator project. This beginner's guide walks you through every step, offering valuable tips and lessons learned.

The tutorial will demonstrate how to build a PWM hardware peripheral and integrate it with an existing RISC-V softcore processor

This tutorial will demonstrate how to modify a RISC-V softcore processor to enable button inputs

This tutorial will demonstrate a FIFO implementation for an FPGA that can be used asynchronously and mitigates metastability

In this tutorial, we demonstrate how to use a phase-locked loop (PLL) in an FPGA as well as demonstrate methods to avoid glitches

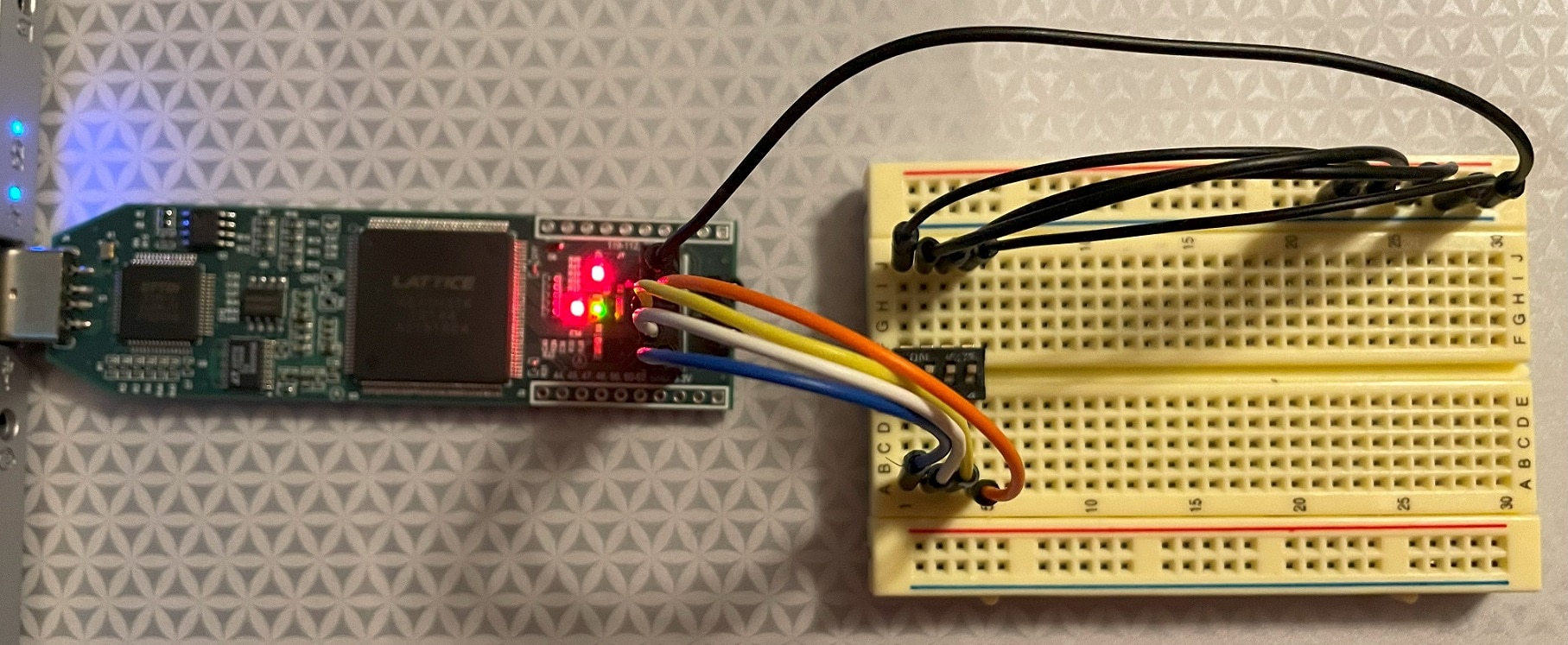

In this FPGA tutorial, we demonstrate how to instantiate block RAM in Verilog, read and write to/from it, and initialize values from a text file.

In this FPGA tutorial, we demonstrate how to write a testbench in Verilog, simulate a design with Icarus Verilog, and view the resultant waveform with GTKWave

In this FPGA tutorial, we demonstrate how to use parameters and modules in Verilog to create hierarchical designs

In this FPGA tutorial, we demonstrate how to create a finite state machine in Verilog

In this FPGA tutorial we demonstrate how to create a clock divider using procedural assignments in Verilog

In this tutorial, we demonstrate how to create a full adder using Verilog continuous assignment statements.

How to configure apio, yosys, and Project IceStorm to build and upload FPGA designs

Co-Browse

Wenn Sie die Co-Browse-Funktion verwenden, erklären Sie sich damit einverstanden, dass ein Kundendienstmitarbeiter von DigiKey Ihren Browser aus der Ferne betrachten kann. Wenn das Co-Browse-Fenster geöffnet wird, geben Sie bitte die Sitzungs-ID, die Sie in der Symbolleiste finden, an den Kundendienstmitarbeiter weiter.

DigiKey misst dem Schutz Ihrer Privatsphäre große Bedeutung bei. Weitere Informationen finden Sie in unserer Datenschutzerklärung und unserem Cookie-Hinweis.

Ja, weiter zu Co-Browse

Vielen Dank!

Behalten Sie Ihren Posteingang im Auge, um Neuigkeiten und Updates von DigiKey nicht zu verpassen.

Bitte geben Sie eine E-mail-Adresse ein

Bitte akzeptieren Sie den Erhalt von Marketing-Informationen per E-Mail