Entwicklung und Zertifizierung von funktional sicheren Systemen auf RTD-Basis

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2023-07-24

Ein Widerstand-Temperatur-Detektor (RTD), bestehend aus einem Transducer und seinem analogen Frontend(AFE)-Schaltkreis zur Signalaufbereitung, ist weit verbreitet, genau und zuverlässig. Für unternehmenskritische und hochzuverlässige Anwendungen ist es jedoch oft notwendig, ein funktionell sicheres System zu entwerfen und zu gewährleisten, und zwar über den Zertifizierungsprozess für Komponenten nach Route 1S oder Route 2S.

Die Zertifizierung eines Systems für funktionale Sicherheit ist ein komplexer Prozess, da alle Komponenten des Systems auf potenzielle Fehlermöglichkeiten und -mechanismen überprüft werden müssen. Es gibt verschiedene Methoden zur Fehlerdiagnose, und die Verwendung von bereits zertifizierten Teilen erleichtert diesen Arbeitsaufwand ebenso wie den Zertifizierungsprozess.

Beachten Sie, dass „Zuverlässigkeit“ mit funktionaler Sicherheit zusammenhängt, aber nicht dasselbe ist. Vereinfacht ausgedrückt bedeutet „zuverlässig“ einen Entwurf und eine Implementierung, die gemäß den Spezifikationen ohne Probleme oder Ausfälle funktioniert, während „funktional sicher“ bedeutet, dass etwaige Ausfälle durch die Schaltung erkannt werden müssen. Für kritische Anwendungen sind sowohl Zuverlässigkeit als auch funktionale Sicherheit erforderlich.

Dieser Artikel befasst sich mit den Grundlagen von Widerstandsthermometern und ihren Signalaufbereitungsschaltungen im Zusammenhang mit der funktionssicheren Zertifizierung. Anschließend werden die verschiedenen Stufen der Zuverlässigkeits- und Ausfallzertifizierung erörtert und was erforderlich ist, um sie auf beiden Wegen zu erreichen. Zur Veranschaulichung der wichtigsten Punkte werden zwei mehrkanalige RTD-AFE-ICs, das Paar AD7124 von Analog Devices, zusammen mit einem zugehörigen Evaluierungsboard verwendet.

Die Rolle der funktionalen Sicherheit

Die Aufgabe der funktionalen Sicherheit besteht darin, durch die ordnungsgemäße Ausführung einer oder mehrerer automatischer Schutz-/Sicherheitsfunktionen ein inakzeptables Risiko von Verletzungen oder Gesundheitsschäden für Menschen zu vermeiden. Sie gewährleistet, dass das Produkt, das Gerät oder das System im Falle einer Störung weiterhin sicher funktioniert. Sie wird in einer Vielzahl von industriellen, kommerziellen und sogar einigen Verbraucheranwendungen benötigt, wie z. B.:

- Autonome Fahrzeuge

- Maschinensicherheit und Robotik

- Industrielle Steuerungssysteme (ICS)

- Smart-Home-Produkte für Verbraucher

- Intelligente Fabriken und Lieferketten

- Sicherheitstechnische Anlagen und Gefahrstellensteuerungen

Bei einer funktional sicheren Konstruktion würde beispielsweise die Funktion eines Hauptschalters das Abschalten der Stromversorgung unterstützen, selbst wenn andere Komponenten im System ausfallen (Abbildung 1).

Abbildung 1: In einem funktional sicheren System kann es keinen Zweifel daran geben, dass dieser Schalter das tut, wofür er ausgelegt ist. (Bildquelle: Pilla via City Electric Supply Co.)

Abbildung 1: In einem funktional sicheren System kann es keinen Zweifel daran geben, dass dieser Schalter das tut, wofür er ausgelegt ist. (Bildquelle: Pilla via City Electric Supply Co.)

RTD-Grundlagen

Warum sollte man sich bezüglich funktionaler Sicherheit mit der Temperatur befassen? Ein guter Grund dafür ist, dass die Temperatur die am häufigsten gemessene physikalische Größe ist. Sie ist häufig mit sicherheitsrelevanten oder kritischen Anwendungen verbunden und wird durch eine große Auswahl an Messwertgebern unterstützt. Dazu gehören RTDs, die konzeptionell einfach sind: Sie nutzen den bekannten und wiederholbaren Temperaturkoeffizienten des Widerstands (TCR) von Metallen wie Nickel, Kupfer und Platin. Platin-Widerstandsthermometer mit einem Widerstand von 100 Ohm (Ω) und 1000 Ω bei 0 °C sind am weitesten verbreitet und können im Bereich von -200 °C bis +850 °C eingesetzt werden.

Diese RTDs haben eine sehr lineare Beziehung zwischen Widerstand und Temperatur über diesen Temperaturbereich; für Situationen mit extrem hoher Genauigkeit gibt es Korrektur- und Kompensationstabellen und -faktoren, die angewendet werden können. Das Platin-Widerstandsthermometer mit einem Nennwiderstand von 100 Ω (bezeichnet als PT100) hat einen typischen Widerstand von 18 Ω bei -200°C und 390,4 Ω bei +850°C.

Ein RTD muss mit einem bekannten Strom erregt werden, der in der Regel auf etwa 1 Milliampere (mA) begrenzt ist, um die Selbsterhitzung zu minimieren. Je nach dem Nennwiderstand des RTD werden auch andere Stromwerte verwendet.

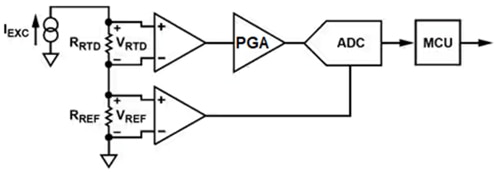

Der Spannungsabfall über dem RTD wird gleichzeitig über ein AFE gemessen, das aus einem Verstärker mit programmierbarer Verstärkung (PGA) und, in fast allen Fällen, aus einem Analog/Digital-Wandler (ADC) in Verbindung mit einem Mikrocontroller (MCU) besteht (Abbildung 2).

Abbildung 2: Um mit einem RTD die Temperatur zu messen, muss ein bekannter Strom durch den RTD fließen und der Spannungsabfall an ihm gemessen werden, um dann das Ohmsche Gesetz anzuwenden. (Bildquelle: Digi-Key)

Abbildung 2: Um mit einem RTD die Temperatur zu messen, muss ein bekannter Strom durch den RTD fließen und der Spannungsabfall an ihm gemessen werden, um dann das Ohmsche Gesetz anzuwenden. (Bildquelle: Digi-Key)

Die Schaltungstopologie dieses Grundschemas ist identisch mit der Verwendung eines Messwiderstands zur Bestimmung des Stroms durch eine Last, aber hier werden die bekannten und unbekannten Variablen vertauscht. Bei der Strommessung ist der Widerstand bekannt, während der Strom unbekannt ist, so dass die Berechnung I = V/R lautet. Bei RTDs ist der Strom bekannt, nicht aber der Widerstand, so dass die Berechnung R = V/I lautet.

Der PGA wird benötigt, um die Signalintegrität aufrechtzuerhalten und den dynamischen Bereich zu maximieren, da die Spannungspegel über dem RTD je nach RTD-Typ und Temperatur von einigen zehn Millivolt bis zu Hunderten von Millivolt reichen können.

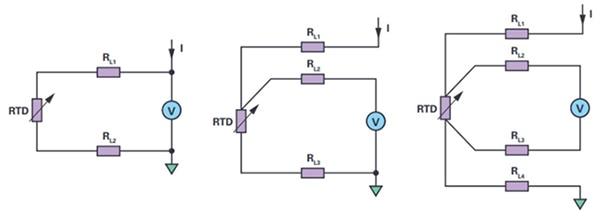

Die physikalische Verbindung zwischen der Erregungsquelle, dem RTD und dem PGA kann eine Zwei-, Drei- oder Vier-Draht-Schnittstelle sein. Während zwei Leitungen im Prinzip ausreichen, gibt es Probleme mit IR-Abfall in den Verbindungsleitungen sowie andere Artefakte. Die Verwendung der Drei- und Vierdraht-Topologien in einer fortschrittlicheren Kelvin-Verbindung führt zu einer genaueren und gleichmäßigeren Leistung, auch wenn dies die Verdrahtungskosten erhöht (Abbildung 3).

Abbildung 3: Das Widerstandsthermometer kann über nur zwei Drähte (links) angesteuert und abgefragt werden, aber die Verwendung von drei (Mitte) und sogar vier (rechts, Kelvin-Anschluss) Drähten ermöglicht die Eliminierung verschiedener Fehlerquellen aufgrund der Drähte. (Bildquelle: Analog Devices)

Abbildung 3: Das Widerstandsthermometer kann über nur zwei Drähte (links) angesteuert und abgefragt werden, aber die Verwendung von drei (Mitte) und sogar vier (rechts, Kelvin-Anschluss) Drähten ermöglicht die Eliminierung verschiedener Fehlerquellen aufgrund der Drähte. (Bildquelle: Analog Devices)

Beginnen wir mit Terminologie und Normen

Wie bei vielen anderen Fachgebieten gibt es auch bei der funktionalen Sicherheit viele einzigartige Begriffe, Datensätze und Akronyme, die in den entsprechenden Diskussionen häufig verwendet werden. Zu diesen gehören:

- Ausfälle pro Zeit (FIT): die Anzahl der Ausfälle, die in einer Milliarde (109) Betriebsstunden des Geräts zu erwarten sind.

- Fehlermöglichkeits- und -einflussanalyse (FMEA): Der Prozess, bei dem so viele Komponenten, Baugruppen und Teilsysteme wie möglich überprüft werden, um potenzielle Fehlermöglichkeiten in einem System sowie deren Ursachen und Auswirkungen zu ermitteln.

- Fehlereffekt- und Diagnoseanalysen (FMEDA): Eine systematische Analysetechnik zur Ermittlung von Fehlerraten, Fehlermöglichkeiten und Diagnosefähigkeiten auf Teilsystem-/Produktebene.

Für eine vollständige Analyse werden FIT-Daten zusammen mit Fehlereffekt- und Diagnoseanalysen (FMEDAs) für die verschiedenen Komponenten des Systems benötigt. Die FMEA bietet nur qualitative Informationen, während die FMEDA sowohl qualitative als auch quantitative Informationen bietet, die es dem Benutzer ermöglichen, den Grad der Kritikalität der Fehlermodi zu messen und sie nach ihrer Wichtigkeit zu ordnen. FMEDA fügt Informationen zu Risiko, Fehlermöglichkeiten, Auswirkungen und Diagnose sowie Zuverlässigkeit hinzu.

- Sicherheitsintegritätslevel (SIL): Es gibt vier diskrete Integritätslevel, die mit SIL verbunden sind: SIL 1, SIL 2, SIL 3 und SIL 4. Je höher der SIL-Level ist, desto höher ist das damit verbundene Sicherheitsniveau und desto geringer ist die Wahrscheinlichkeit, dass ein System nicht ordnungsgemäß funktioniert.

Eine SIL-2-Einstufung bedeutet, dass über 90 % der Fehler im System diagnostiziert werden können. Um einen Entwurf zu zertifizieren, muss der Systementwickler der Zertifizierungsstelle Nachweise über die potenziellen Fehler vorlegen, ob es sich um sichere oder gefährliche Fehler handelt und wie die Fehler diagnostiziert werden können.

- Die IEC 61508 mit dem offiziellen Titel „Funktionale Sicherheit elektrischer/elektronischer/programmierbarer elektronischer sicherheitsbezogener Systeme“ (informell auch als „Elektronische Funktionssicherheit“ bezeichnet) ist die Spezifikation für funktional sichere Designs. Sie dokumentiert den Entwicklungsablauf, der für die Entwicklung eines SIL-zertifizierten Teils erforderlich ist. Für jeden Schritt muss eine Dokumentation erstellt werden, vom Konzept und der Definition über den Entwurf, das Layout, die Fertigung, die Montage und die Prüfung.

Dieses Verfahren wird als Route 1S bezeichnet und ist kompliziert. Es gibt jedoch eine Alternative zur Route 1S, die Route 2S. Dies ist ein Weg, der sich in der Praxis bewährt hat, und ist anwendbar, wenn große Mengen des Produkts für Endprodukte und Systeme entwickelt wurden und in der Praxis mit Tausenden von Betriebsstunden eingesetzt werden.

Auf der Route 2S kann ein Produkt immer noch zertifiziert werden, indem der Zertifizierungsbehörde der Nachweis über folgende Informationen erbracht wird:

- In der Praxis verwendete Anzahl an Komponenten

- Analyse von Rücksendungen aus dem Feld und Nachweis, dass die Rücksendungen nicht auf Fehler im Bauteil selbst zurückzuführen sind

- Sicherheitsdatenblatt mit detaillierten Angaben zu den Diagnosen und dem von ihnen gebotenen Umfang

- Pin- und Chip-FMEDA

Zusammenführung von RTD-Schnittstellen mit SIL Route 2S

Die Zertifizierung eines Systems ist ein langwieriger Prozess, da alle Komponenten des Systems auf mögliche Fehlermechanismen überprüft werden müssen und es verschiedene Methoden zur Fehlerdiagnose gibt. Die Verwendung bereits zertifizierter Teile reduziert den Aufwand und verkürzt den Zertifizierungsprozess.

Eine hochintegrierte, ausgereifte RTD-Schnittstellenkomponente ist der Schlüssel zur Erleichterung der Route-2S-Zertifizierung, da sie ein komplettes Lösungspaket definiert und somit vollständig mit Daten aus dem Feldeinsatz und Fehlern charakterisiert werden kann. Dies steht im Gegensatz zur Verwendung mehrerer kleinerer Baustein-ICs, bei denen die verschiedenen Schnittstellen und Wechselwirkungen für die jeweils verwendete Verbindungskonfiguration analysiert werden müssen.

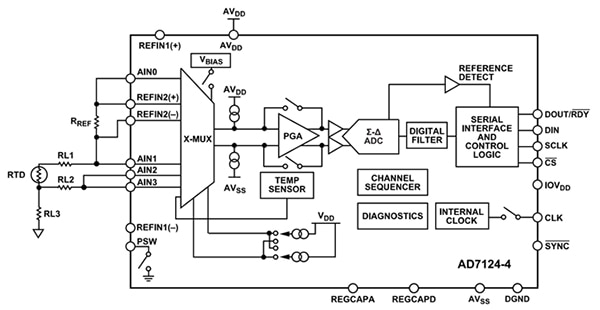

Ein Beispiel dafür ist der vierkanalige AD7124-4 (Abbildung 4) und der ähnliche achtkanalige AD7124-8 (im Folgenden als „AD7124“ bezeichnet, wenn es um die vielen gemeinsamen Merkmale geht). Diese Komponenten eignen sich aufgrund ihrer eingebetteten Selbsttest- und Diagnosefunktionen sowie ihrer Erfolgsbilanz in der Praxis hervorragend für den Route-2S-Fluss.

Abbildung 4: Der vierkanalige AD7124-4 ist eine funktionell vollständige RTD-Sensor-zu-Prozessor-Signalkette. (Bildquelle: Analog Devices)

Abbildung 4: Der vierkanalige AD7124-4 ist eine funktionell vollständige RTD-Sensor-zu-Prozessor-Signalkette. (Bildquelle: Analog Devices)

Diese ICs sind Komplettlösungen für die mehrkanalige RTD-Messung und enthalten alle Bausteine, die vom Sensor bis zum digitalisierten Ausgang und zur Kommunikation mit einem zugehörigen Mikrocontroller benötigt werden. Dazu gehören der Mehrkanal-Multiplexer, PGA, 24-Bit-Sigma-Delta-ADC, Stromquellen für die RTDs, Spannungsreferenzen für den internen Betrieb, Systemtakt, analoge und digitale Filterung sowie drei- oder vierdrähtige serielle Schnittstellen für SPI, QSPI, MICROWIRE und DSP-kompatible Verbindungen.

Das Vorhandensein dieser Funktionen stellt jedoch nicht per se eine Grundlage für die Qualifikation nach SIL-Route-2S dar. Für ein funktionssicheres Design ist eine Reihe von eingebetteten Diagnosen für die vielen Funktionen erforderlich, aus denen das RTD-System besteht. Die vielfältigen eingebetteten Diagnosen im AD7124 minimieren sowohl die Designkomplexität als auch die Designzeit und machen eine Duplizierung der Signalkette zur Diagnoseabdeckung überflüssig.

Zu diesen Diagnosen gehören u. a. die Überwachung der Stromversorgung, der Referenzspannung und des Analogeingangs, die Erkennung einer offenen Leitung zu den RTDs, die Überprüfung der Umwandlungs- und Kalibrierungsleistung, die Überprüfung der Funktionalität der Signalkette, die Überwachung der Lese-/Schreibfunktionen und die Überwachung der Registerinhalte.

Wie lassen sich diese „High-Level“-Aussagen in die notwendigen On-Chip-Diagnosen umsetzen? Die Antwort hat viele Facetten, unter anderem:

SPI-Diagnose: Bei jedem Schreibvorgang an den AD7124 erzeugt der Prozessor einen CRC-Wert (Cyclic Redundancy Check), der an die an den ADC gesendeten Informationen angehängt wird. Der ADC erzeugt dann seinen eigenen CRC-Wert aus den empfangenen Informationen und vergleicht ihn mit dem vom Prozessor empfangenen CRC-Wert. Wenn beide Werte übereinstimmen, ist die Information intakt und wird in das entsprechende On-Chip-Register geschrieben.

Wenn die Werte nicht übereinstimmen, bedeutet dies, dass bei der Übertragung eine Verfälschung aufgetreten ist, und der IC setzt ein Fehlerflag, das anzeigt, dass eine Datenverfälschung aufgetreten ist. Der AD7124 schützt sich auch selbst, indem er die korrupten Informationen nicht in ein Register schreibt.

Ein ähnliches CRC-Verfahren wird verwendet, wenn Informationen vom AD7124 zum Systemprozessor gelesen werden. Schließlich zählt die Schnittstelle auch die Taktimpulse, um sicherzustellen, dass es bei jedem Lese- oder Schreibdatenrahmen nur acht solcher Impulse gibt, so dass sichergestellt ist, dass keine Taktstörung aufgetreten ist.

Speicherprüfungen: Ein CRC wird auch verwendet, um die Registerinhalte beim Einschalten oder bei jeder Änderung von On-Chip-Registern (z. B. bei der Änderung der Verstärkung) zu überprüfen. Der CRC-Prozess wird auch regelmäßig durchgeführt, um sicherzustellen, dass kein Speicherbit aufgrund von Rauschen oder anderen Ursachen „umgedreht“ wurde. Wenn eine Änderung eintritt und der Prozessor darauf hingewiesen wird, dass die Registereinstellungen beschädigt wurden, kann er den ADC zurücksetzen und die Register neu laden.

Überprüfungen der Signalkette: Alle kritischen statischen Spannungen können über den ADC überprüft werden, einschließlich der Stromversorgungsschienen, LDO-Reglerausgänge und Referenzspannungen; das Vorhandensein oder Fehlen des externen Kondensators über dem LDO kann ebenfalls überprüft werden. Darüber hinaus kann eine bekannte Spannung an den ADC-Eingang angelegt werden, um den ADC und die Einstellungen der Verstärkungsfunktion zu überprüfen. Außerdem können bekannte Ströme über die Analogeingänge eingespeist werden, um zu prüfen, ob ein RTD offen oder kurzgeschlossen ist.

Umwandlung und Kalibrierung: Die Ergebnisse der ADC-Umwandlung werden kontinuierlich überprüft, um festzustellen, ob sie alle Nullen oder den vollen Skalenwert erreichen, was jeweils auf ein Problem hinweist. Der Bitstrom vom Modulator im Kern des ADC wird überwacht, um sicherzustellen, dass er nicht gesättigt ist. Tritt eine Sättigung ein (d. h. es wurden 20 aufeinanderfolgende Einsen oder Nullen vom Modulator geliefert), wird ein Fehlerflag gesetzt.

Haupttaktfrequenz: Die Frequenz dieses Taktgebers steuert nicht nur die Wandlungsraten, sondern legt auch die Kerbfrequenzen der digitalen Filter mit 50/60 Hertz (Hz) fest. Ein internes Register im AD7124 ermöglicht es dem Begleitprozessor, die Zeit zu messen und damit die Genauigkeit des Haupttaktgebers zu überprüfen.

Zusätzliche Merkmale: Der AD7124 verfügt über einen Temperatursensor, der auch zur Überwachung der Chiptemperatur verwendet werden kann. Beide Versionen haben eine ESD-Einstufung (elektrostatische Entladung) von 4 Kilovolt (kV) und sind in einem 5 × 5 Millimeter (mm) großen LFCSP-Gehäuse untergebracht, das für eigensichere Designs geeignet ist.

Aufgrund der internen Komplexität, der Raffinesse und der fortschrittlichen Selbsttestfunktionen des AD7124-4 und des AD7124-8 ist es sinnvoll, eine Möglichkeit zu haben, um die ICs zu testen und zu bewerten.

Zu diesem Zweck bietet Analog Devices zwei miteinander verbundene Boards an: das Evaluierungsboard EVAL-AD7124-4SDZ für den AD7124-4 (Abbildung 5) und die dazugehörige (System-Demonstrationsplattform)/Schnittstellenkarte EVAL-SDP-CB1Z SDP (Abbildung 6). Ersteres ist spezifisch für den AD7124-4 und funktioniert in Verbindung mit letzterer, die die Kommunikation mit dem PC des Anwenders und der Auswertungssoftware über eine USB-Verbindung ermöglicht.

Abbildung 5: Das EVAL-AD7124-4SDZ ist ein Evaluierungsboard für den AD7124-4. (Bildquelle: Analog Devices)

Abbildung 5: Das EVAL-AD7124-4SDZ ist ein Evaluierungsboard für den AD7124-4. (Bildquelle: Analog Devices)

Abbildung 6: Die Schnittstellenkarte EVAL-SDP-CB1Z ist eine Ergänzung zum Evaluierungsboard EVAL-AD7124-4SDZ und bietet eine USB-Verbindung zu einem Host-PC. (Bildquelle: Analog Devices)

Abbildung 6: Die Schnittstellenkarte EVAL-SDP-CB1Z ist eine Ergänzung zum Evaluierungsboard EVAL-AD7124-4SDZ und bietet eine USB-Verbindung zu einem Host-PC. (Bildquelle: Analog Devices)

Die Evaluierungsanordnung wird durch die Software AD7124-4 EVAL+ unterstützt, die die Bausteinregisterfunktionalität des AD7124-4 vollständig konfiguriert und den IC ansteuert. Darüber hinaus bietet es Zeitbereichsanalysen in Form von Wellenformdiagrammen, Histogrammen und zugehörigen Rauschanalysen zur Bewertung der ADC-Performance.

Übergang zum funktional sicheren Design

Es ist wichtig zu wissen, dass der AD7124-4 und der AD7124-8 nicht nach SIL eingestuft sind, was bedeutet, dass sie nicht nach den Entwicklungsrichtlinien der Norm IEC 61508 entworfen und entwickelt wurden. Wenn man jedoch die Endanwendung versteht und die verschiedenen Diagnosen richtig einsetzt, kann man sie für die Verwendung in einem SIL-bewerteten Design bewerten.

Auf dem Weg zur Route-1S-Zertifizierung gibt es zahlreiche Überlegungen zur Analyse und Behebung von Fehlern, die systembedingt oder zufällig sein können. Systembedingte Fehler sind auf Konstruktions- oder Fertigungsmängel zurückzuführen, wie z. B. ein verrauschter Interrupt aufgrund mangelnder Filterung am externen Interrupt-Pin oder unzureichendem Headroom für ein Signal. Im Gegensatz dazu sind zufällige Fehler auf physikalische Ursachen wie Korrosion, thermische Belastung oder Abnutzung zurückzuführen.

Ein wichtiges Problem ist das gefährliche unentdeckte Versagen, das mit mehreren Techniken angegangen wird. Um zufällige Fehler zu minimieren, wenden Entwickler eine oder alle von drei Taktiken an:

- Verwendung zuverlässigerer, robusterer Komponenten.

- Nutzung von Diagnosen, die sich auf integrierte Erkennungsmechanismen stützen, die über Hardware oder Software implementiert sind.

- Fehlertoleranz durch redundante Schaltungen. Durch Hinzufügen eines redundanten Pfades kann ein einzelner Ausfall toleriert werden. Dies wird als System mit Hardware-Fehlertoleranz 1 (HFT 1) bezeichnet, was bedeutet, dass ein Fehler nicht zum Ausfall des Systems führen kann.

Ein Hilfsmittel zum Verständnis der SIL-Level-Abdeckung ist eine Matrix, die den Anteil der sicheren Ausfälle (SFF) (den Umfang der Diagnoseabdeckung) und die Hardware-Fehlertoleranz (die Redundanz) darstellt (Abbildung 7).

|

|||||||||||||||||||||||

Abbildung 7: Diese Matrix charakterisiert den Anteil der sicheren Ausfälle (SFF) gegenüber der Hardware-Fehlertoleranz (HFT) und gibt Aufschluss über die SIL-Abdeckung. (Bildquelle: Analog Devices)

Die Zeilen zeigen den Umfang der Diagnoseabdeckung, während die Spalten die Hardware-Fehlertoleranz angeben. Eine HFT von 0 bedeutet, dass bei einem Fehler im System die Sicherheitsfunktion verloren geht. Eine höhere Diagnosestufe reduziert die benötigte Systemredundanz oder verbessert den SIL-Level der Lösung bei gleichbleibender Redundanz (Verschiebung in der Matrix nach unten).

Beachten Sie, dass die FMEDA einer typischen Temperaturanwendung, bei der diese Geräte eingesetzt werden, einen sicheren Ausfallanteil (SFF) von mehr als 90 % gemäß IEC 61508 aufweist. Normalerweise wären zwei herkömmliche ADCs erforderlich, um diesen Grad der Abdeckung durch Redundanz zu erreichen, aber der AD4172 benötigt nur einen einzigen ADC, was zu erheblichen Einsparungen bei den Stücklistenkosten und dem Platz auf der Platine führt.

Dokumentation für SIL-bewertete Designs

Um die Route-1S-Zertifizierung zu erhalten, ist eine umfangreiche Dokumentation erforderlich. Zu den erforderlichen Quellendokumenten gehören:

- Sicherheitsdatenblatt (das Sicherheitshandbuch für ein SIL-bewertetes Teil)

- Pin-FMEDA und Chip-FMEDA, mit Fehlermodi, Auswirkungen und Analysen für beide

- Anhang F Checkliste (definiert durch IEC 61508)

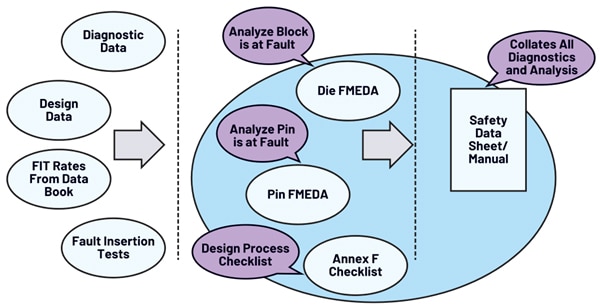

Diese Unterlagen stammen wiederum aus einer Vielzahl von Quellen (Abbildung 8):

- Die Diagnosedaten aus dem Datenblatt decken alle auf dem Bauteil verfügbaren Diagnosefunktionen ab.

- Designdaten beziehen sich auf interne Daten. Zum Beispiel die Chipfläche und die Auswirkung der einzelnen internen Blöcke der Komponente.

- Die FIT mit den Raten für die verschiedenen Komponenten sind im Datenbuch verfügbar.

- Fehlereinfügetests werden für Blöcke durchgeführt, die nicht anhand von Entwurfs- und Diagnosedaten analysiert werden können. Diese Tests werden auf der Grundlage der Anwendungsanforderungen geplant, und die Ergebnisse der Fehlereinfügetests werden zur Stärkung der FMEDA- und FMEA-Dokumente verwendet.

Abbildung 8: Die verschiedenen Dokumentationsquellen werden zusammengeführt und zu einem vollständigen Informationspaket zusammengestellt, das für die SIL-Zertifizierung benötigt wird. (Bildquelle: Analog Devices)

Abbildung 8: Die verschiedenen Dokumentationsquellen werden zusammengeführt und zu einem vollständigen Informationspaket zusammengestellt, das für die SIL-Zertifizierung benötigt wird. (Bildquelle: Analog Devices)

Eine genauere Betrachtung der Einzelheiten:

- Das Sicherheitshandbuch bzw. Sicherheitsdatenblatt enthält alle Informationen, die für die Integration des AD7124-4 oder AD7124-8 erforderlich sind. Es fasst alle Diagnosen und Analysen zusammen, die aus verschiedenen Dokumenten und Datensätzen einfließen.

- Die Chip-FMEDA für den AD7124-4 und AD7124-8 analysiert die Hauptblöcke im Anwendungsschaltplan, identifiziert Fehlermodi und -effekte und überprüft die Diagnose und Analysen für eine bestimmte Sicherheitsfunktion. Die Analyse des Taktgebermoduls zeigt beispielsweise die Fehlermodi, die Auswirkung der einzelnen Fehler auf die Ausgabe, den Umfang der Diagnoseabdeckung und eine Analyse der Auswirkungen (Abbildung 9).

|

Abbildung 9: Diese Tabelle definiert den Ausfallmodus, die Auswirkungen, die Diagnose und die Analyse des Master-Taktgeberblocks. (Bildquelle: Analog Devices)

Das Ergebnis dieser FMEDA ist eine quantitative Darstellung der Ausfallraten für sichere Ausfälle, gefährliche entdeckte Ausfälle und gefährliche unentdeckte Ausfälle. All dies wird zur Berechnung des SFF herangezogen.

Die Pin-FDEMA betrachtet Fehler aus einem anderen Blickwinkel. Es werden verschiedene Arten von Fehlern an den Pins des AD7124-4 und AD7124-8 und deren Auswirkungen auf die RTD-Anwendung analysiert. Sie tut dies für jeden einzelnen Pin und beschreibt das Ergebnis für den Fall, dass der Pin getrennt wird, einen Kurzschluss mit der Versorgung/Masse oder einen Kurzschluss mit benachbarten Pins hat.

Die Checkliste in Anhang F ist eine Checkliste für Konstruktionsmaßnahmen zur Vermeidung von systematischen Fehlern. Sie umfasst:

- Produktübersicht

- Anwendungsinformationen

- Sicherheitskonzept

- Vorhersagen zur Lebensdauer

- FIT

- FMEDA-Berechnungen - SFF und DC

- Hardware-Sicherheitsmechanismen

- Beschreibung der Diagnostik

- EMV-Stabilität

- Betrieb in redundanten Konfigurationen

- Anhänge und Dokumentenliste

Zusammenfassend lässt sich sagen, dass die Zertifizierung der funktionalen Sicherheit eines neu eingeführten Bauteils über Route 1S lang, komplex, zeitaufwändig, intensiv und umfassend ist. Glücklicherweise ist die oben erwähnte Route 2S ein alternativer Ansatz, der für einige Komponenten praktikabel ist.

Route 2S: Ein alternativer Weg

Der als Route 2S bekannte Weg ist für ein veröffentlichtes Bauteil mit Felderfahrung und Daten anwendbar und wird als „in der Praxis bewährt“ bezeichnet. Sie basiert auf einer Analyse der Kundenrückgaben und der Anzahl der ausgelieferten Komponenten. Sie kann nicht für neue Komponenten verwendet werden, die noch nicht oder nur wenig in der Praxis verwendet wurden.

Route 2S ermöglicht eine SIL-Zertifizierung, als ob das Teil vollständig nach der Norm IEC 61508 analysiert worden wäre. Sie steht Modul- und Systementwicklern zur Verfügung, wenn sie den betreffenden IC in der Vergangenheit erfolgreich eingesetzt haben und die Ausfallrate aus der Praxis kennen. Die eingebetteten Test- und Verifikationsfunktionen sowie die Leistungsdaten machen den AD7214-4 und den AD7214-8 zu guten Kandidaten für Route 2S.

Die Anwendung von Route 2S erfordert detaillierte und statistisch signifikante Daten über Rückgaben und Ausfälle im Feld. Diese Anforderung ist für IC-Anbieter viel schwieriger zu erfüllen als für Anbieter von Boards oder Modulen. Der Grund dafür ist, dass erstere im Allgemeinen nicht genügend Kenntnis über die endgültige Anwendung haben oder darüber, welcher Prozentsatz der fehlerhaften Einheiten aus dem Feld zu ihnen zur Analyse zurückgeschickt wird.

Fazit

Der Route-1S-Pfad für die funktional sichere Zertifizierung neuer Produkte ist gründlich, umfassend und detailliert. Er ist auch eine technische Herausforderung und definitiv zeitaufwändig. Im Gegensatz dazu ermöglicht das Route-2S-Verfahren die Zertifizierung freigegebener Produkte auf der Grundlage von Felderfahrungen, Fehlern und Analysedaten. Dies ist ein nützlicher Weg, der von den RTD-Schnittstellen-ICs AD7214-4 und AD7214-8 unterstützt wird, da sie über die erforderliche Historie verfügen. Ebenso wichtig ist, dass diese ICs viele Diagnose- und Selbsttestfunktionen und -merkmale enthalten, die sie zu geeigneten Kandidaten für eine solche Zertifizierung machen.

Verwandte Inhalte

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.