Implementierung des Internets der Dinge mit einem integrierten Mikrocontroller

Zur Verfügung gestellt von Europäische Fachredakteure von DigiKey

2014-08-28

Zu den wesentlichen Konstruktionskriterien für einen preiswerten Drahtlosknoten für das Internet der Dinge zählt ein ausgewogenes Verhältnis zwischen Integration und Flexibilität. Mit hochintegrierten, extrem stromsparenden Drahtlos-Transceivern lassen sich die Kosten eines Sensorknotens auf verschiedene Weise verringern, und sie ermöglichen einen Knoten, der überall platziert und mit dem Internet verbunden werden kann.

In vielen Drahtlos-Transceivern ist heutzutage ein Mikrocontroller integriert, um die Drahtlosstacks zu verarbeiten, und zur Auswahl stehen dabei viele unterschiedliche Bausteine. Einige davon bringen auch zusätzlichen Speicher und Rechenleistung mit, um kleine Codeblöcke ausführen zu können, wodurch unter Umständen die Notwendigkeit eines getrennten Mikrocontrollers im Drahtlosknoten entfällt. So lassen sich Einsparungen bei Platz, Kosten und Stromverbrauch erzielen, und der Knoten kann mit einer kleinen Batterie länger betrieben werden. Letztendlich steigt damit die Flexibilität der Endanwendung.

Beim Internet der Dinge ermöglichen Technologien wie IEEE802.15.4 ZigBee preisgünstige Drahtlosknoten in einem 2,4-GHz-Netz, das mit dem Internet verbunden werden kann, wobei die Überwachung und Steuerung der einzelnen Bausteine sicher von einem Terminal aus erfolgt, das irgendwo in der Welt Internetzugang hat. Über Cloud-Services wird dann ein skalierbarer Steuerungsmechanismus zur Verwaltung dieser Drahtlosknoten bereitgestellt. Dieses Prinzip kommt zunehmend in Anwendungen wie Smart Homes, Gebäudemanagement und Sicherheitssystemen zum Einsatz.

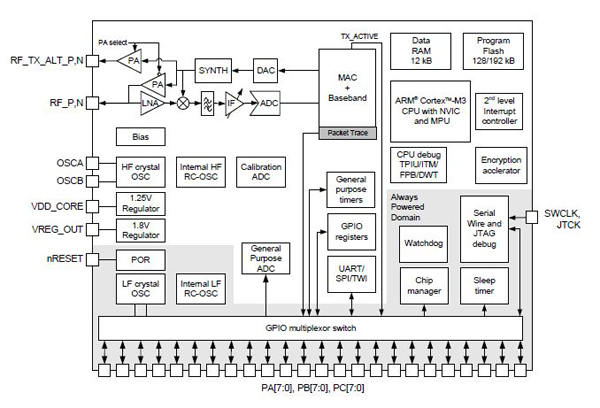

Der EM351 und der EM357 von Silicon Labs sind voll integrierte SoCs (System on Chip), die einen IEEE 802.15.4-2003-konformen 2,4-GHz-Transceiver, einen 32-Bit ARM Cortex-M3-Mikroprozessor, Flash- und RAM-Speicher sowie praktische Peripherieeinrichtungen enthält. Sie sind für Entwickler von ZigBee-basierten Systemen vorgesehen.

Abbildung 1: Die EM35x-Familie von Silicon Labs enthält einen ARM Cortex-M3-Prozessor zur Verarbeitung sowohl des ZigBee-Drahtlosprotokollstacks als auch von Benutzeranwendungen für das Internet der Dinge.

Der Transceiver nutzt eine effiziente Architektur, mit der die Anforderungen hinsichtlich des Dynamikbereichs, die vom IEEE 802.15.4-2003-Standard vorgegeben sind, sogar noch um über 15 dB übertroffen werden. Dank der integrierten Empfangskanalfilterung wird eine belastbare Koexistenz mit anderen Kommunikationsstandards im 2,4-GHz-Spektrum wie Wi-Fi und Bluetooth möglich. Integriert sind bereits Regler, VCO, Schleifenfilter und Leistungsverstärker, was die Anzahl der externen Komponenten und damit die Kosten minimiert.

Der integrierte ARM Cortex-M3-Kern ist für eine effiziente Speicherauslastung optimiert und bietet zwei verschiedene Betriebsarten: privilegierter Modus und Benutzermodus. Dank dieser Architektur lässt sich der Netzwerkstack vom Anwendungscode trennen. So wird eine unerwünschte Modifikation von beschränkt zugänglichen Speicherbereichen und Registern vermieden, was zu einer erhöhten Stabilität und Zuverlässigkeit der bereitgestellten Lösungen führt.

Der EM351 verfügt über 128 kB eingebetteten Flash-Speicher, und der EM357 verfügt über 192 kB eingebetteten Flash-Speicher. Beide Chips verfügen über 12 kB integrierten RAM zur Daten- und Programmspeicherung, und die integrierte Software nutzt einen effektiven Wear-Leveling-Algorithmus, der die Lebensdauer des eingebetteten Flash-Speichers optimiert. Das ist eine entscheidende Überlegung, kann doch der Drahtlosknoten bis zu 10 Jahre in Betrieb sein, sodass hier auch die Abnutzung der Flash-Zellen berücksichtigt werden muss.

Zur Erfüllung der strengen Timing-Anforderungen seitens der ZigBee-Drahtlosverbindung sind in die Bausteine hardwareseitig eine Reihe von MAC-Funktionen, ein AES128-Verschlüsselungsbeschleuniger sowie automatisches CRC-Handling integriert. Die MAC-Hardware übernimmt das automatische ACK-Senden und -Empfangen, die automatische Back-Off-Verzögerung und das Clear Channel Assessment für das Senden sowie die automatische Filterung der empfangenen Pakete. In den MAC ist außerdem eine Packet-Tracer-Schnittstelle integriert, die eine vollständige eingriffsfreie Erfassung aller Pakete zu und von den Entwicklungstools ermöglicht.

Beim EM35x-Funkempfänger handelt es sich um einen Überlagerungsempfänger für niedrige ZF, der unterschiedliche Signalpfade verwendet, um die Empfindlichkeit gegenüber Rauschstörungen zu verringern. Nach der HF-Verstärkung wird das Signal durch einen Spiegelunterdrückungsmixer abwärtsgemischt, gefiltert und dann durch einen ADC digitalisiert. Der digitale Abschnitt des Empfängers nutzt einen kohärenten Demodulator zur Erzeugung von Symbolen für den hardwarebasierten MAC. Der Digitalempfänger enthält außerdem die Routinen zur Analogfunkkalibrierung und steuert die Verstärkung innerhalb des Empfängerpfads.

Der MAC verbindet den On-Chip-RAM mit den RX- und TX-Basisbandmodulen. Außerdem übernimmt der MAC die hardwarebasierte IEEE 802.15.4-2003-Paketebenenfilterung. Er liefert eine präzise Symbol-Zeitbasis, die den Synchronisierungsaufwand der Stacksoftware verringert und die Protokoll-Timing-Anforderungen erfüllt. Außerdem bietet er Timer- und Synchronisierungsunterstützung für den IEEE 802.15.4-2003 CSMA-CA-Algorithmus.

Die Bausteine verfügen über 24 GPIO-Pins, die mit anderer Peripherie oder alternativen Funktionen geteilt werden, um Schnittstellen zu externen digitalen Sensoren oder Controllern zu ermöglichen. Der integrierte serielle Controller SC1 kann für den SPI- (Master oder Slave), TWI- (nur Master) oder UART-Betrieb konfiguriert werden, und der serielle Controller SC2 kann für den SPI- (Master oder Slave) oder den TWI-Betrieb (nur Master) konfiguriert werden.

Der EM35x verfügt über einen Mehrzweck-ADC, der Analogsignale von sechs GPIO-Pins im asymmetrischen oder Differenzialmodus für analoge Sensoren abtasten kann. Dieser ADC besitzt einen DMA-Modus zur Erfassung von Samples und zu deren automatischer Übertragung in den RAM, wo auf sie durch den integrierten Mikrocontroller ganz einfach zugegriffen werden kann.

Der Stromverbrauch ist für einen Drahtlosknoten im Internet der Dinge eine der Hauptüberlegungen, und die EM35x-Bausteine bieten einen extrem stromsparenden Tiefschlafbetrieb, für den mehrere Taktmodi zu Auswahl stehen. Die Taktung des Schlaf-Timers kann entweder mit dem externen 32,768-kHz-Quarzoszillator oder mit einem 1-kHz-Takt erfolgen, der vom internen 10-kHz-RC-Oszillator abgeleitet wird. Als Alternative kann auch die gesamte Taktung deaktiviert werden, wodurch der Modus mit dem niedrigsten Energieverbrauch erzielt wird. In diesem Niedrigststromverbrauchsmodus kann der Chip ausschließlich durch externe Ereignisse an den GPIO-Pins aufgeweckt werden. Der EM35x zeichnet sich durch einen kurze Startzeit (typischerweise 110 μs) aus dem Tiefschlaf bis zur Ausführung der ersten ARM Cortex-M3-Anweisung aus. Durch die Integration des Prozessorkerns in den Baustein können alle Stromversorgungskreise direkt gesteuert werden, wodurch der insgesamt minimale Stromverbrauch für die Anwendung erreicht wird.

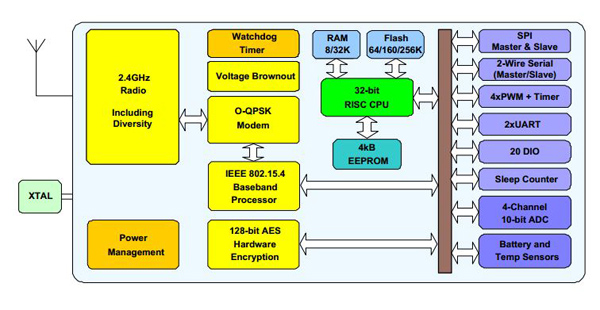

Einen anderen Ansatz beim integrierten Mikroprozessor verfolgt der JN516x von NXP Semiconductor, in den ein 2,4-GHz-Funkmodul, ein Modem, ein Basisband-Controller sowie ein Sicherheitscoprozessor integriert sind. Er verfügt über einen angepassten 32-Bit-Load/Store-RISC-Kern, der die On-Chip-Ausführung von Software ermöglicht, wobei die Rechenleistung zwischen dem IEEE802.15.4 MAC-Protokoll, Protokollen anderer höherer Ebenen und der Benutzeranwendung geteilt wird.

Der JN516x weist eine einheitliche Speicherarchitektur mit dem Kernspeicher, dem Datenspeicher, den Peripheriegeräten und den E/A-Anschlüssen auf, die sämtlich im selben linearen Adressraum organisiert sind, um die Code-Entwicklung und das Debugging zu vereinfachen. Der Baustein enthält bis zu 256 kB Flash, bis zu 32 kB RAM und 4 kB EEPROM.

Abbildung 2: Der JN516x nutzt einen angepassten 32-Bit-Load/Store-RISC-Prozessor zur Verarbeitung eines ZigBee-Protokollstacks und von Benutzeranwendungen in einem linearen Adressraum.

Von der Architektur her wurde die CPU neben den Drahtlos-Transceiver integriert und für geringen Stromverbrauch im Hinblick auf batteriebetriebene Anwendungen ausgelegt. Er ist ausreichend leistungsstark, um gleichzeitig ein Drahtlosprotokoll und komplexe Anwendungen sowie die effiziente Codierung von höheren Programmiersprachen wie C zu implementieren, die mit dem Softwareentwicklungskit bereitgestellt werden.

Die CPU hat Zugriff auf einen Block aus 15 32-Bit-Mehrzweckregistern (General Purpose, GP) und eine kleine Anzahl zweckgebundener Register, die zur Speicherung des Prozessorstatus und zur Steuerung des Interrupt-Handlings verwendet werden. Der Inhalt jedes GP-Registers kann aus dem Speicher geladen oder dort gespeichert werden, während arithmetische und logische Operationen, Schiebe- und Rotieroperationen sowie signierte und unsignierte Vergleiche entweder zwischen zwei Registern ausgeführt und in einem dritten gespeichert oder zwischen Registern und einer in der Anweisung enthaltenen Konstante ausgeführt werden können. Operationen zwischen Mehrzweck- und zweckgebundenen Registern werden in einem Zyklus ausgeführt, während solche mit Speicherzugriff einen weiteren Zyklus benötigen, um das Antworten des Speichers zu ermöglichen.

Das Anweisungsset manipuliert 8-, 16- und 32-Bit-Daten; das heißt, dass Programme Objekte dieser Größen äußerst effizient verwenden können. Die Manipulation von 32-Bit-Daten ist insbesondere für Protokolle und High-End-Anwendungen nützlich, weil so die Implementierung von Algorithmen mit weniger Anweisungen als bei Prozessoren mit geringerer Wortgröße möglich wird, und es werden weniger Taktzyklen ausgeführt, was den Energieverbrauch senkt. Der Kern unterstützt auch Hardware-Multiplikator-Blöcke, die zur effizienten Implementierung von DSP-Algorithmen genutzt werden können.

Die CPU-Architektur weist auch Merkmale auf, die den Prozessor für eingebettete Echtzeitanwendungen tauglich machen, bei denen mehrere Aufgaben im Prozessor laufen müssen. Zum Schutz der Ressourcen im gesamten Baustein kann der Prozessor entweder im Supervisor- oder im Benutzermodus arbeiten, wodurch der Zugriff entweder auf alle Register oder nur auf die GP-Register gewährt wird. Der Wechsel in den Supervisor-Modus erfolgt bei einem Reset oder per Interrupt, und gestartete Aufgaben, die normalerweise im Benutzermodus laufen würden, werden dann in einer RTOS-Umgebung ausgeführt.

Fazit

Die Integration eines 32-Bit-Prozessors neben dem Drahtlos-Transceiver liefert Leistung sowohl für einen bewährten und robusten Netzwerkstack als auch für Benutzeranwendungen, wodurch sich die Anzahl der verwendeten Bauelemente und der Stromverbrauch eines Drahtlosknotens im Internet der Dinge verringern lässt. Dazu können angepasste Kerne wie der JN516x oder Kerne nach dem Industriestandard wie bei den EM35x-Bausteinen verwendet werden. In beiden Beispielen wird durch die Integration des Kerns die Verwaltung der Stromversorgungskreise sowohl des Drahtlos-Transceiver-Blocks als auch des Kerns durch den Code ermöglicht, was zu einem geringeren Gesamtstromverbrauch und einer längeren Batteriebetriebszeit führt. Damit verringert sich der Wartungsaufwand und der Batteriewechselbedarf über die gesamte Lebensdauer des Knotens, was wiederum die Betriebskosten senkt.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.