Programmierbare SoCs helfen Herstellern, das richtige Gleichgewicht zwischen Konfigurierbarkeit und Leistung zu finden

Zur Verfügung gestellt von Europäische Fachredakteure von DigiKey

2017-10-24

Zwar ist die Halbleitertechnologie die Basis aller elektronischen Produkte, aber es ist die Software, die unsere moderne Welt erst möglich macht. Im Vergleich mit der Hardware bietet Software eine nahezu grenzenlose Flexibilität, und in Zusammenarbeit mit einem Hochleistungs-Mikroprozessor kann sie atemberaubende Ergebnisse liefern. Die Fortschritte der künstlichen Intelligenz wären beispielsweise ohne Software, die auf den modernsten Mikroprozessoren läuft, unmöglich.

In den letzten Jahrzehnten war eine Verschiebung des Gleichgewichts zwischen Hardware und Software zu erkennen. Es wird allgemein akzeptiert, dass heutzutage etwa 70 % der Funktionalität eines Produkts durch eingebettete Software bereitgestellt wird, und dies fast ausschließlich aufgrund ihrer Flexibilität.

Da die Leistungsgrenzen durch Anwendungen ständig nach oben verschoben werden, wird dieses Ungleichgewicht zu einem einschränkenden Faktor. Software ist letztlich die Implementierung einer Funktion in abstrakter Form, was aber unvermeidbare Kosten in Form von Ausführungszeit generiert. Wenn dieselbe Funktion in dedizierter Hardware auf Transistorebene implementiert wird, wird sie zwangsläufig schneller ausgeführt. Dieser Leistungszuwachs wird normalerweise mit einem Flexibilitätsverlust erkauft, aber das Gleichgewicht zwischen Leistung und Flexibilität wird durch Bausteine erleichtert, in denen drei Schlüsseltechnologien integriert sind: Prozessorkerne, feste Funktionen und konfigurierbare Hardware.

Hohe Leistung und optimierte Lösungen

Bausteine, in die diese drei Technologien integriert sind, werden als System-on-Chip (SoC) bezeichnet. Aufgrund ihrer Eigenschaften bieten sie eine größere Flexibilität als Bausteine mit festen Funktionen, sind besser konfigurierbar als ein Mikrocontroller und verfügen über mehr Funktionen als ein FPGA, da sie die Vorzüge dieser Merkmale auf einer einzigen Plattform vereinen.

Dies ist aus verschiedenen Gründen eine gute Mischung für eine Anwendung. Der wichtigste ist Leistung, die entweder als Durchsatz oder als Echtzeit-Reaktion interpretiert werden könnte. Geringe Leistungsaufnahme und optimiertes Design könnte ein weiterer Grund sein. Je mehr Funktionen in einen einzigen Baustein integriert werden können, desto weniger externe Komponenten werden benötigt. Diese Szenarien decken die „Eckpunkte“ eines SoCs ab: das Liefern von reiner Leistung und die Bereitstellung eines optimierten Designs.

Wenn letztlich der Durchsatz das Ziel ist, so ist die von einem frei gestaltbaren Design in Form eines ASIC gebotene Leistung kaum zu schlagen. Da allerdings die nicht wiederkehrenden Kosten sinken, müssen die Entwicklungskosten für ein ASIC gegen den Preis pro Einheit aufgewogen werden, und diese Zahl wirkt sich nur bei großen Stückzahlen aus. Die FPGA-Technologie hat die Branche lange mit ASIC-ähnlicher Leistung auf einer nach dem Verlassen des Werks konfigurierbaren Plattform versorgt. Bei der zugrunde liegenden Technologie wird spezialisierte Logik durch Lookup-Tabellen simuliert, aber es wurden immer fest verdrahtete Funktionen integriert – insbesondere dann, wenn es um Funktionen ging, die nur schwer durch Programmlogik emuliert werden können. Dies führte in letzter Zeit dazu, dass Prozessor-Subsysteme einbezogen werden. Damit gehören diese Bausteine definitiv zur Kategorie SoC. Die FPGA-Branchenführer bieten Bausteine an, die die drei Schlüsselelemente eines SoC umfassen. Dazu gehört die Zynq®-UltraScale+-Familie von Xilinx, die Bausteine anbietet, in denen Dual- oder Quad-ARM®-Cortex®-A53-Kerne mit ARM-Cortex-R5-Kernen gepaart sind.

Während diese Bausteine auf Anwendungen abzielen, die hohe Leistung fordern, gehören die SmartFusion2-Familie von SoC-FPGAs von Microsemi und die PSoC-5LP-Familie von Cypress Semiconductor zu den SoCs, die in die zweite Kategorie fallen. In beiden ist ein ARM-Cortex-M3-Kern mit fest verdrahteten Funktionen und konfigurierbarer Hardware integriert. Die oben genannten Bausteine werden von Plattformen unterstützt, die sowohl auf Hardware- als auch auf Softwareebene umfassenden Support für die Anwendungsentwicklung bieten.

Multicore-SoCs

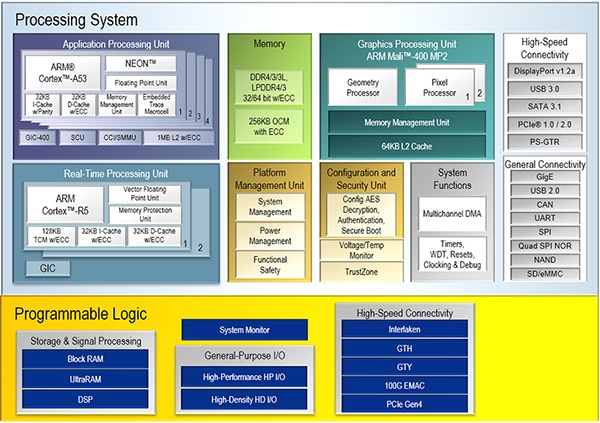

Die Evaluierungsplatine ZCU102 von Xilinx bietet das Zynq-UltraScale+-Multiprozessor-SoC XCZU9EG, das einen unglaublichen Integrationsgrad aufweist. Seine Multicore-Verarbeitungsmöglichkeiten umfassen einen 64-Bit-Quad-Core-Prozessor Cortex-A53 und einen Dual-Core-Echtzeitprozessor Cortex-R5, die eng über FPGA-Logik gekoppelt sind, Kommunikationsschnittstellen und einen Grafikprozessor (Abbildung 1).

Abbildung 1: Blockdiagramm der hoch integrierten Zynq-UltraScale+-EG von Xilinx.

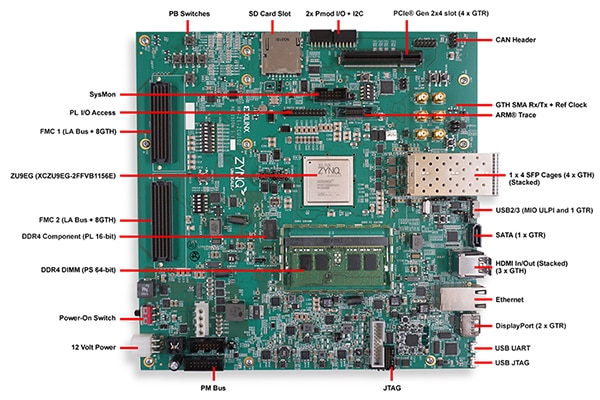

Diese Evaluierungsplatine (Abbildung 2) verfügt über 4 Gbit mit dem Prozessor-Subsystem verbundenes DDR4-SODIMM und weitere 512 Mbit mit der programmierbaren Logik verbundenen DDR4-Arbeitsspeicher. Sie umfasst zwei Schnittstellen für FPGA-Mezzanin-Karten (FMC) für künftige Erweiterungen sowie weitere moderne Schnittstellen (PCIe Gen2x4, USB3, Displayport, SATA), die sie zu einer perfekten Evaluierungsplattform für viele Anwendungen in den Bereichen Automobilbau, Industrie, Video und Kommunikation machen.

Abbildung 2: Die Hauptmerkmale der Evaluierungsplatine ZCU102.

Die EG-Familie kann von etwa 100.000 auf mehr als eine Million Systemlogikzellen mit 50.000 bis über 500.000 Lookup-Tabellen (LUT) für konfigurierbare Logikblöcke skaliert werden. Dieser Konfigurierbarkeitsgrad eröffnet der Zynq-UltraScale+-Familie zusammen mit Hardware-Multimediablöcken und der integrierten Hochgeschwindigkeits-Peripherie einen großen Bereich von anspruchsvollen Anwendungen. Die Evaluierungsplatine ZCU102 ist eine perfekte Entwicklungsplattform mit der fünffachen Leistung pro Watt im Vergleich mit der Zynq-7000-Familie.

Anwendungsbeispiele

Die Nachfrage nach Leistung steigt ständig, insbesondere im Bereich Kommunikation. Der größte Teil der Internetaktivitäten stützt sich auf Informationen, die in Datenbanken gespeichert sind. Am weitesten verbreitet ist SQL. Eine Technik, mit der SQL-Datenbanken beschleunigt werden können, ist die Verwendung eines Cache-Speichers, der normalerweise als Standardprozessor mit integriertem DRAM implementiert ist.

Dies funktioniert zwar, ist aber ebenfalls durch die Grenzen der Prozessorarchitektur beschränkt, die nicht für diesen Einsatzzweck konzipiert wurde. Ein Baustein wie der Zynq-UltraScale+ bietet eine optimierte Lösung für das Streamen von Daten, ohne den Prozessor zu beanspruchen, indem er unter Verwendung seiner hochentwickelten Merkmale als eigenständiger Server im Netzwerk fungiert. Damit kann eine vierfache Leistung mit einem Zwanzigstel der Leistungsaufnahme verglichen mit einem Standard-x86-Prozessor erreicht werden.

In der Automobilindustrie werden mit Fahrerassistenzsystemen (ADAS) immer häufiger Kameras in Autos eingesetzt. Dadurch entsteht ein Bedarf an SoCs, die 2-Megapixel-Kameradaten mit 30 fps bewältigen können. Dank seines hohen Integrationsgrads ist der Zynq-UltraScale+ hervorragend für diese anspruchsvolle Anwendung geeignet.

Die ZCU102 wird mit kompletter IP und Tools geliefert, sodass Sie sofort mit der Entwicklung dieser und vieler weiterer Anwendungen beginnen können. Mitgeliefert wird die Vivado Design Suite: Design Edition-Gutschein mit Lizenzen, die auf das Gerät und den Baustein XCZU9EG auf der Platine beschränkt sind.

SoCs im IoT

Das IoT wird oft als Netzwerk von Geräten mit beschränkten Ressourcen und Funktionen beschrieben, aber es umfasst auch die Vernetzung und Automatisierung vieler vorhandener Anwendungen. SoCs mit dem richtigen Funktionsumfang und geringer Leistungsaufnahme können aufgrund ihres hohen Integrationsgrades die ideale Plattform für ein vernetztes Gerät darstellen.

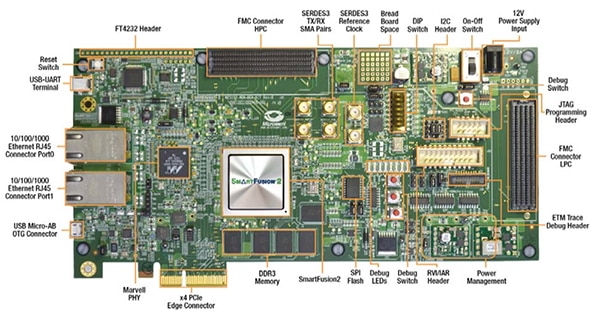

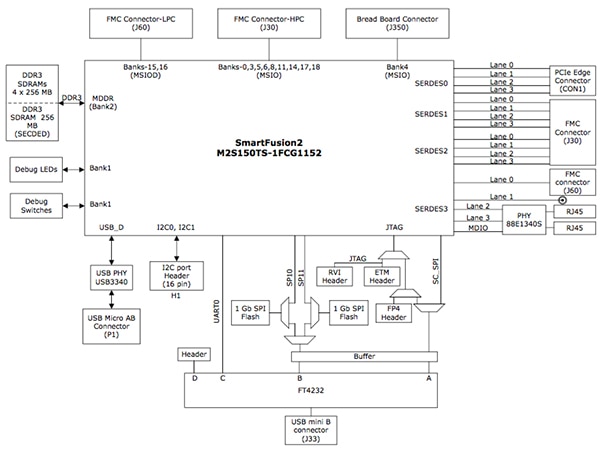

Der SmartFusion2 von Microsemi ist beispielsweise für Motorsteuerung und industrielle Automatisierung bestimmt, kann aber problemlos als Basis eines sicheren vernetzten Geräts fungieren. In ihm sind eine Flash-basierte FPGA-Struktur mit einem ARM-Cortex-M3-Kern und Hochleistungs-Kommunikationsschnittstellen wie CAN, Gigabit Ethernet, HS-USB und PCIe sowie DDR2/DDR3-Speichercontroller integriert. Microsemi hat zur Unterstützung der Entwicklung von Anwendungen mit dem SmartFusion2 das erweiterte SmartFusion2-Entwicklungskit entwickelt. Abbildungen 3 und 4 zeigen die wesentlichen Merkmale der Platine.

Abbildung 3: Blockdiagramm des erweiterten SmartFusion2-Evaluierungskits.

Abbildung 4: Das erweiterte SmartFusion2-Entwicklungskit von Microsemi.

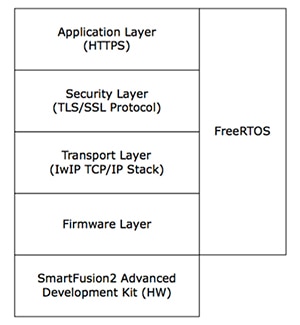

Auf der Grundlage dieses Kits hat Microsemi eine Demo-Anwendung entwickelt, die die für das Erstellen eines sicheren Webservers mit Unterstützung des Sicherheitsprotokolls TLS/SSL zum Senden und Empfangen von verschlüsselten Daten erforderliche Software einschließlich Unterstützung enthält, also genau für die Anwendung, die jetzt im IoT an Bedeutung gewinnt.

Wie Abbildung 5 zeigt, erhält die Anwendungsschicht Anforderungen von einem Client-Browser und beantwortet diese mit statischen Webseiten, während die Serveranwendung auf dem SmartFusion2 läuft. Das Protokoll TLS/SSL wurde mithilfe der Open-Source-Bibliothek PolarSSL implementiert. Die Transportschicht (TCP/IP) wird durch weitere Open-Source-Software realisiert, die mit oder ohne Betriebssystem verwendet werden kann. In diesem Beispiel werden Tasks mit dem Open-Source-Echtzeitbetriebssystem FreeRTOS priorisiert und geplant. Das erweiterte Entwicklungskit kann auch zur Ausführung von uClinux konfiguriert werden, eines Betriebssystems auf Linux-Basis, das von Microsemi für das SmartFusion2-SoC modifiziert wurde.

Abbildung 5: Übersicht über eine sichere Webserver-Anwendung, die auf demSmartFusion2 implementiert ist.

Mit 150.000 Logikelementen, einem 166-MHz-Cortex-M3-Kern und dedizierten DSP-Blöcken zusammen mit eingebettetem, nicht flüchtigem Speicher (Non-Volatile Memory, NVM) und SRAM bietet der SmartFusion2 ein leistungsfähiges Gleichgewicht zwischen Konfigurierbarkeit und fest verdrahteter Funktionalität. Das erweiterte Entwicklungskit nutzt dieses Potenzial durch die Unterstützung von PCIe-Randverbindern, FMC-Verbindern, zwei Gigabit-Ethernet-Anschlüssen, SPI und UART. Über einen zusätzlichen Hochleistungs-Operationsverstärker kann der Energieverbrauch des Bausteins während der Entwicklung gemessen werden. Dies ermöglicht den Entwicklern, eine optimale Lösung innerhalb eines vorgegebenen Budgets zu entwickeln.

Optimiertes Design

In einem breiten Bereich von Anwendungen können Ein-Chip-Lösungen eingesetzt werden, in denen die richtige Mischung von digitalen und analogen Komponenten und Arbeitsspeicher integriert werden kann. So entsteht ein optimierter und maßgeschneiderter Baustein. Die Technik führt zwangsläufig zu einer kleineren Platinenfläche, weniger externen Komponenten und geringeren Materialkosten.

Programmierbare analoge Bausteine sind weit weniger verbreitet als ihre digitalen Gegenstücke. Der Markt wird hier von der PSoC-Familie von Cypress Semiconductor beherrscht. PSoC-Bausteine, d. h. programmierbare SoCs, verfügen über einen Mikrocontrollerkern, fest verdrahtete Blöcke und programmierbare Logik, unterscheiden sich aber durch ihre konfigurierbare analoge Peripherie, die über eine Schaltkondensator-Technologie, Operationsverstärker, Komparatoren, ADCs und DACs und digitale Filterblöcke aktiviert werden. Zusammen ermöglichen diese Merkmale den Aufbau von komplexen analogen Signalpfaden, die eng mit den digitalen Funktionen auf dem Chip gekoppelt sind.

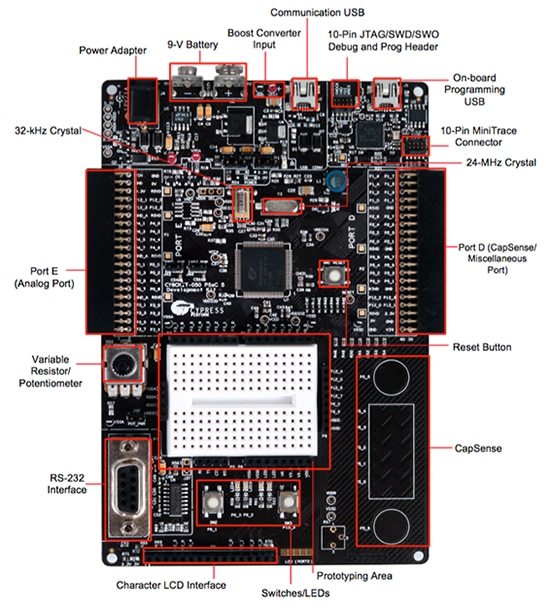

Das Entwicklungskit CY8CKIT-050 kann zusammen mit der integrierten Entwicklungsumgebung (IDE) PSoC Creator verwendet werden. Damit können zahlreiche Anwendungen auf Grundlage des PSoC 5LP entwickelt werden. Abbildung 6 zeigt die wesentlichen Elemente des Entwicklungskits.

Abbildung 6: Das Entwicklungskit für das PSoC 5LP.

PSoC Creator ist eine IDE mit einem Unterschied: Sie kann für die gleichzeitige Entwicklung von Embedded-Software (die in diesem Fall auf dem ARM-Cortex-M3-Kern des PSoC 5 läuft) und von Hardwarefunktionen verwendet werden, die in den konfigurierbaren analogen Blöcken des Bausteins implementiert werden. Analoge Funktionen können mittels Ziehen und Ablegen eingefügt werden und APIs, die den Zugriff auf diese Funktionen per Software erlauben, können dynamisch generiert werden. Zum Lieferumfang der IDE gehört eine große Anzahl vordefinierter Verstärker und Filter. Die Entwickler können aber auch eigene Funktionen erstellen.

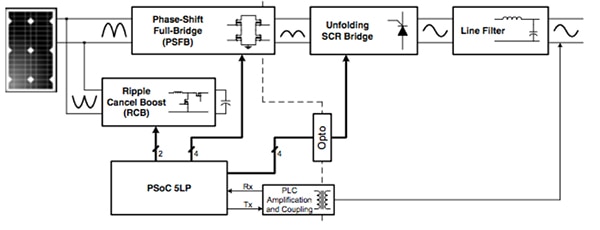

Cypress hat eine Anzahl von Anwendungsbeispielen zur Demonstration der Fähigkeiten des PSoC 5 erstellt, darunter die Implementierung eines Solar-Controllers mit Mikro-Inverter. Abbildung 7 zeigt einen Überblick über die Architektur der Anwendung. Der Mikro-Inverter umfasst mehrere Konvertierungsstufen einschließlich einer Boost-Steuerung zur Unterdrückung der Welligkeit, Steuerung des Ausgangsstroms, Phasenregelkreis und MPPT-Algorithmus (Maximum Power Point Tracking). In dieser Anwendung werden die Fähigkeiten der Plattform hervorragend demonstriert.

Abbildung 7: Der mit dem PSoC 5LP implementierte Solar-Controller mit Mikro-Inverter.

Fazit

Zwar stellt Software eine abstrakte Möglichkeit zur Implementierung fast jeder Aufgabe oder Funktion dar, aber die Leistungsfähigkeit dedizierter Hardware kann selten übertroffen werden. Bei der steigenden Nachfrage nach höherem Durchsatz und besserer Konfigurierbarkeit setzen sich Plattformen, auf denen Hardware, Software, analoge und digitale Bereiche kombiniert werden, vermehrt in Form von Ein-Chip-Lösungen durch.

Diese SoCs erfüllen einen Bedarf, aber wie bei jeder Implementierung sind Kompromisse erforderlich. Nicht alle SoCs bieten die richtigen fest verdrahteten Funktionen. Selbstverständlich wird eine einzelne Anwendung kaum alle verfügbaren Merkmale nutzen, aber in manchen Fällen ist der finanzielle Aufwand für eine flexiblere Plattform möglicherweise nicht zu leisten.

Allerdings werden diese Kompromisse aufgrund des technischen Fortschritts seltener und die von ihnen bereitgestellte Flexibilität rechtfertigt ihre Nutzung in einem breiteren Anwendungsbereich.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.