Integrieren Sie RISC-V mit Hilfe von RVfpga in Ihren Computerarchitekturkurs

Liebe Professoren und Freunde,

Online ist bequem und hat uns während der Pandemie gerettet, aber es geht nichts über den persönlichen Kontakt. Das intensive Gefühl der Praxisnähe und die Teamarbeit mit Kollegen, die alle versuchen, dasselbe Thema zu meistern.

Wir befinden uns mitten in einer weltweiten Reihe von Workshops zur Schulung von Lehrern über die Verwendung von RISC-V in Kursen über Computerarchitektur und den Entwurf von Systemen auf Chips (SoCs). Wir haben letztes Jahr in den USA begonnen und auch in Europa mehrere Veranstaltungen durchgeführt. Besonders hervorzuheben ist der Workshop im Dezember im Silicon Valley, an dem fast 60 Lehrer und Ausbilder teilnahmen.

Jetzt geht es nach Osten: nach Israel, Japan, Taiwan, Korea und China.

RVfpga-Partner, darunter DigiKey, arbeiten mit uns zusammen, um dies zu ermöglichen.

Zu diesem Zweck bitten wir Sie um einen Tag Ihrer Zeit, damit Sie die nächste Generation von Informatik- und Ingenieurstudenten in die Lage versetzen können, reale Kenntnisse über Computerarchitekturen und die RISC-V-Befehlssatzarchitektur zu erwerben.

Was ist RVfpga?

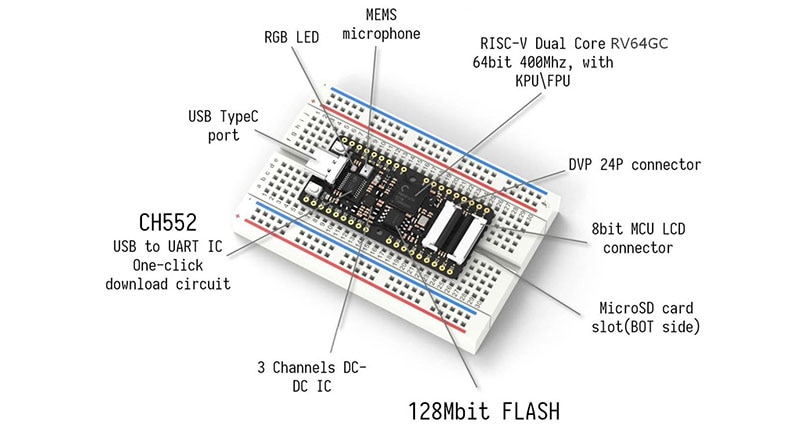

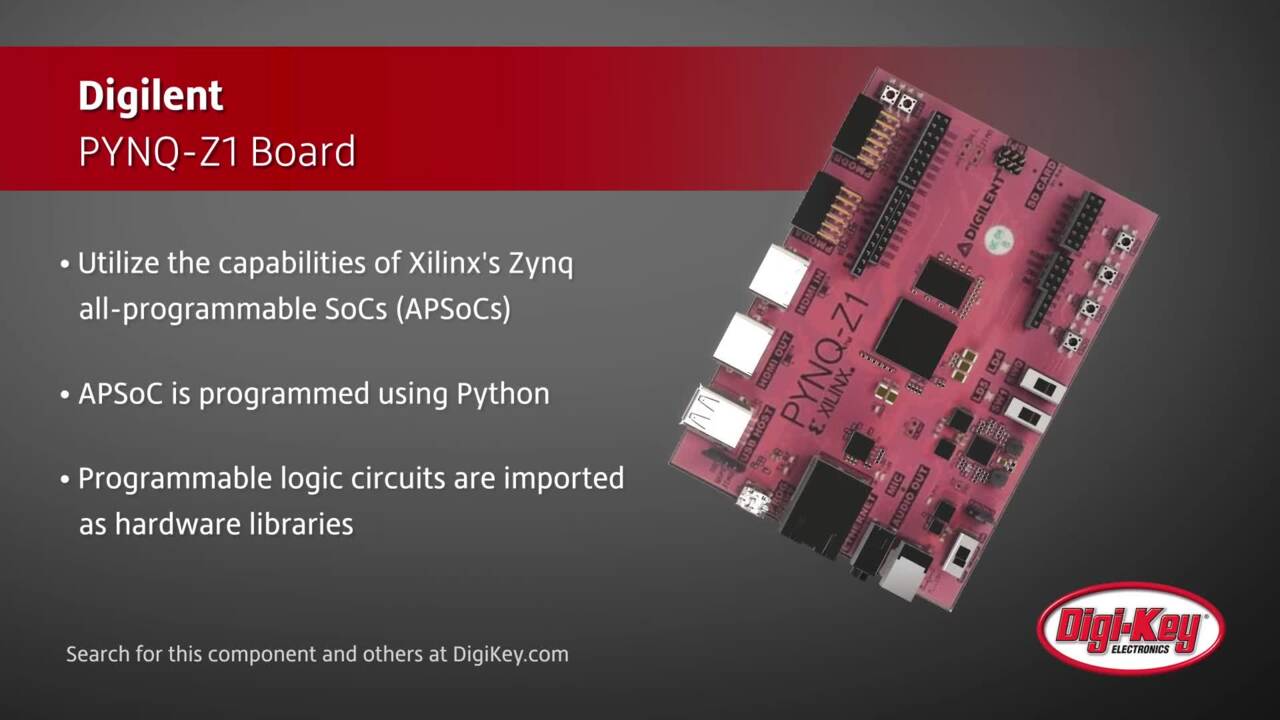

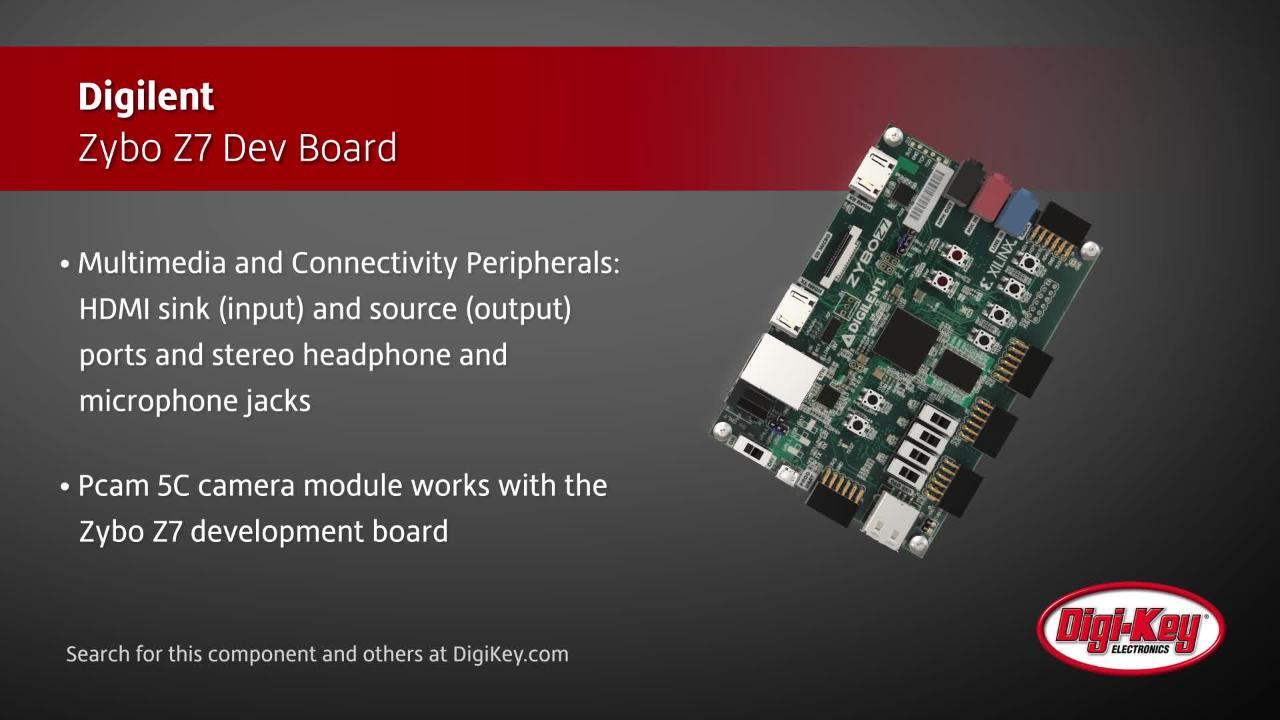

Dieser eintägige RVfpga-Workshop stellt ein kommerzielles auf ein FPGA ausgerichtetes RISC-V-System vor, erörtert die Theorie, die Architektur und die Kursstruktur und zeigt, wie man die praktischen Übungen als Teil des kompletten RVfpga-Kurses nutzen kann.Der Kurs erforscht die Grundlagen der Computerarchitektur unter Verwendung von Western Digitals vollständig verifiziertem, bereits in Silizium gepresstem Open-Source-EH1-RISC-V-Kern SweRV, der auf einen Xilinx-Artix-7-FPGA auf Digilents Entwicklungsboard Nexys A7 ausgerichtet ist. Jeder Teilnehmer wird praktische Erfahrungen mit der FPGA-Plattform und den Software-Tools sammeln, was einen schnellen Start nach der Rückkehr an die Universität ermöglicht.

Der SweRV ist kein „Ausbildungskern“. Er wird in der Praxis in den Grafikprozessoren von Imagination und den Halbleiterfestplatten von Western Digital eingesetzt.

Was werden Sie lernen?

- Der Workshop zeigt, wie man das RISC-V-FPGA-System und die RISC-V-Tools schnell zum Laufen bringt

- Wir beschreiben jedes der Labore und arbeiten eine Auswahl von ihnen praktisch durch

- Wir werden auch besprechen, wie Sie RVfpga in Ihren Lehrplan integrieren können

Zu den spezifischen Themen gehören:

- Installation der Tools (was wir vor dem Workshop empfehlen)

- Ausrichtung des EH1-RISC-V-Kerns und -SoC SweRV auf ein FPGA

- Programmierung des RISC-V-SoC

- Erweiterung des RISC-V-SoCs um weitere Funktionen

- Analyse und Änderung der RISC-V-Kern- und -Speicherhierarchie

Wer sollte teilnehmen?

- Es handelt sich in erster Linie um eine Veranstaltung für die Ausbildung von Lehrkräften, die vor allem für EE-, CS- und CE-Lehrkräfte interessant ist, die Computerarchitektur unterrichten möchten

- Ausbilder in Unternehmen und Hochschulabsolventen, die eine Karriere als Lehrkraft oder Chipdesigner in Erwägung ziehen, werden es ebenfalls nützlich finden

Vernetzung

Es ist eine großartige Gelegenheit, neue Kontakte zu knüpfen und bestehende Kontakte zu anderen Professoren aufzufrischen, die ihre Kurse auf dem neuesten Stand halten wollen. Helfen Sie uns, diese Informationen zu verbreiten und bringen Sie Ihre Kollegen mit.

Treffen Sie sich mit Innovatoren, die RISC-V für Start-up-Projekte evaluieren, und mit Ausbildern in Unternehmen, die gute Materialien für die Schulung neuer Mitarbeiter benötigen.

Unsere Ausbilder:

Durch die Zusammenarbeit mit qualifizierten Akademikern und Experten in anderen Unternehmen, die an RISC-V arbeiten, verfügen wir über einige der kompetentesten Ausbilder der Welt.

ASEE Baltimore & UCSC Santa Clara

Prof. Sarah Harris, Professorin für Elektrotechnik und Computertechnik an der Universität von Nevada, Las Vegas. Sarah Harris erwarb ihren M.S. und Ph.D. an der Stanford University. Sie ist Mitautorin von drei populären Lehrbüchern: Digital Design and Computer Architecture, 2. Auflage (2007), ARM Edition (2015) und RISC-V Edition (2021). Ihre Forschungsinteressen umfassen Computerarchitektur und Anwendungen von eingebetteten Systemen und maschinellem Lernen in der Biomedizintechnik und Robotik.

Taiwan

Michio Abe, anerkannter Experte für RISC-CPU-Architekturen. Er ist Direktor der Abteilung Sales & Solution bei MIPS LLC, Japan. Seine Karriere begann 1985 bei NEC und er war an der Entwicklung von MIPS-CPUs beteiligt, einschließlich der Entwicklung der ursprünglichen MIPS-CPUs von NEC im Jahr 1991. Es folgte die Entwicklung von SoCs für Fahrzeuge mit MIPS- und anderen Kernen und Architekturen. Seit 2015 ist er für die Förderung und Vermarktung der MIPS-CPUs in Japan zuständig, zunächst als Teil von Imagination Technologies und jetzt als eigenständiges Unternehmen.

Unser Gastgeber vor Ort ist Prof. Brian Lin vom NTUST Taipei.

FPL 2023 Göteborg

Daniel A. Chaver Martínez erwarb 1998 einen Abschluss in Physik an der Universität von Santiago de Compostela (USC) und 2000 einen Abschluss in Elektrotechnik an der Universität Complutense von Madrid (UCM). Seinen Doktortitel erwarb er von 2000 bis 2006 an der UCM. Seit dem Jahr 2000 hat er viele verschiedene Kurse zum Thema Computerarchitektur unterrichtet. Seine derzeitigen Forschungsinteressen umfassen: Architektonische Techniken für den Cache und für nichtflüchtige Speicher und OS Scheduling für asymmetrische Multiprozessoren. Seit 2015 arbeitet er mit Imagination Technologies bei der Entwicklung einiger ihrer Prozessoren und Unterrichtsmaterialien zusammen.

Workshop-Reihe (Datum und Ort)

| Datum | Ort/Veranstaltung | Stadt, Land | Format | Anmeldung |

|

25. bis 28. Juni |

ASEE Conference | Baltimore, USA |

Papier: RVfpga: Computerarchitekturkurs und MOOC unter Verwendung eines RISC-V SoC für ein FPGA und Simulation |

https://nemo.asee.org/public/conferences/327/registration |

| 5. und 6. Juli |

NTUST |

Taipeh, Taiwan |

ZWEI persönliche eintägige RVfpga-Workshops in englischer Sprache (mit Unterstützung in Mandarin und Japanisch) |

https://www.eventbrite.co.uk/e/549461984587 [eventbrite.co.uk] https://www.eventbrite.co.uk/e/602617443997 [eventbrite.co.uk] |

| Oktober, Datum TBC | Zhejiang Univ. |

Hangzhou, China |

Persönlicher halbtägiger RVfpga-Workshop auf Chinesisch. Ausbilder: Prof. Liu, Peng und Xi, Yuhao, Zhejiang University, Hangzhou |

Wird noch bekannt gegeben |

| 5. September, 9 Uhr bis 13 Uhr |

FPL 2023 |

Chalmers University, Göteborg, Schweden |

Persönlicher halbtägiger RVfpga-Workshop auf Englisch (Eine Anmeldung nur für den Workshop ist möglich etwa $120) |

https://2023.fpl.org/attend/registration |

| 9. November |

UCSC-Schulungszentrum im Silicon Valley |

Santa Clara, Kalifornien USA |

Persönlicher eintägiger RVfpga-Workshop auf Englisch |

https://www.eventbrite.co.uk/e/rvfpga-understanding-computer-architecture-in-person-workshop-nov-9th-tickets-654132025497 |

Weitere Informationen

- Über IUP und RVfpga: https://university.imgtec.com/teaching-download/

- RISC-V-Blog: https://blog.imaginationtech.com/how-rvfpga-understanding-computer-architecture-will-give-under-grads-real-world-skills

- Einführung in RISC-V: https://www.digikey.com/en/resources/risc-v

Wir freuen uns darauf, Sie persönlich kennenzulernen.

Mit freundlichen Grüßen,

Robert C.W. Owen

Principal Consultant: Worldwide University Programme

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum