Verwendung eines Multicore-Prozessors zum Bau von stromsparenden intelligenten Produkten mit umfassender Medienunterstützung

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-03-26

In intelligenten Produkten werden in zunehmendem Maße herkömmliche Embedded-Echtzeit-Designanforderungen mit anspruchsvollerer Software auf Anwendungsebene kombiniert. Neben einer größeren Rechenlast müssen diese Produkte Benutzerinteraktionen über moderne Mediendienste wie Touchscreens, hochauflösende 3D-Grafiken und Bildsensoren unterstützen.

Trotz der steigenden Anforderungen sind die Entwickler immer häufiger dazu angehalten, den Stromverbrauch und die Kosten zu senken und die Systeme zu verkleinern. Aus diesem Grund müssen sie nach einer effizienteren Alternative zu herkömmlichen Designs mit zahlreichen Subsystemen suchen.

Dieser Artikel behandelt die Entwicklung der Designanforderungen und die Art und Weise, wie aktuelle Prozessoren diese Anforderungen erfüllen. Anschließend stellt er neue Prozessoren von NXP Semiconductors vor und geht auf ihre Verwendung ein. Diese Prozessoren erleichtern es den Entwicklern, der steigenden Nachfrage nach Designs gerecht zu werden, die sowohl für Echtzeitanwendungen als auch für Anwendungen mit hohen Rechenanforderungen geeignet sind.

Prozessorskalierung zur Sicherung von Investitionen in Code

Früher war es üblich, dass die Entwickler die Rechenleistung ihrer Designs skalierten, indem sie Mikroprozessoren mit zusätzlichen Kernen verwendeten, die auf bestimmte Anforderungen auf die Anwendungsverarbeitung abgestimmt waren. Auf diese Weise konnten die Entwickler die Leistung steigern und dabei weiterhin die Kompatibilität mit der vorhandenen Codebasis und der verwendeten Komponentenfamilie gewährleisten.

Mit den Anwendungsprozessoren der Serie i.MX 6 von NXP etwa können die Entwickler die Kompatibilität zum Code erhalten und dabei mit einem Mikroprozessor i.MX 6Solo mit nur einem Arm®-Cortex®-A9-Anwendungsprozessorkern, einem i.MX 6Dual mit zwei Kernen oder einem i.MX 6Quad mit vier Kernen die Leistung skalieren.

Auch in Designs, die einstmals als traditionelle Embedded-Systeme angesehen wurden, nimmt die Nachfrage nach skalierbarer Anwendungsverarbeitung rapide zu. Bei diesen Designs verfolgen die Produkthersteller das Ziel, Haushaltsgeräte, Industriesteuerungen, medizinische Instrumente und viele weitere Produkte intelligent zu machen. Die Halbleiteranbieter haben darauf mit heterogenen Komponenten mit Multicore-Verarbeitung reagiert, die sowohl Anwendungsprozessorkerne als auch eingebettete Prozessorkerne enthalten. Die Familie i.MX 8M von NXP beispielsweise kombiniert bis zu vier Arm-Cortex-A53-Anwendungsprozessoren mit einem eingebetteten Arm-Cortex-M4-Prozessorkern.

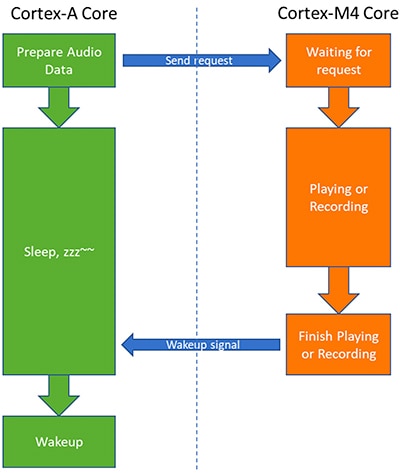

Mit dieser Einzelkomponente können die Entwickler intelligente Audioprodukte bauen. Diese nutzen in vollem Umfang den Anwendungsprozessor, um Audiodaten zu verbessern, zu filtern oder anderweitig zu bearbeiten. Bei der Ausführung der Echtzeitfunktionen für die Wiedergabe stützt sich das Audiosystem auf den eingebetteten Prozessorkern (Abbildung 1). Während auf dem eingebetteten Prozessor die Echtzeitvorgänge verarbeitet werden, kann der Anwendungsprozessor in einen Energiesparmodus versetzt werden, um den Gesamtstromverbrauch zu senken. Sobald die Echtzeitvorgänge abgeschlossen sind, sendet der eingebettete Prozessor einfach ein Aufwachsignal an den Anwendungsprozessor.

Abbildung 1: Heterogene Multicore-Prozessoren sind für intelligente Produktdesigns besonders effizient, da sie sowohl eine hohe Rechenleistung als auch Echtzeitfunktionen bieten, ohne dabei die knappen Energiebudgets zu sprengen. (Bildquelle: NXP Semiconductors)

Neben den heterogenen Kernen sind in die Familie i.MX 8M von NXP umfangreiche Multimedia-Ressourcen wie etwa ein 4K-Videoprozessor (VPU) und ein leistungsstarker 3D-Grafikprozessor (GPU) integriert. Somit stellt diese Produktfamilie eine effiziente Lösung für intelligente Produkte mit Video- und 3D-Grafikanwendungen dar, die immer häufiger anzutreffen sind.

Die Entwickler leistungsstarker Systeme stehen dennoch vor der Herausforderung, den Stromverbrauch von batterie- und netzbetriebenen Systemen kontinuierlich senken zu müssen. Um dem gerecht zu werden, kommt bei der Fertigung der Prozessorfamilie i.MX 8M Mini von NXP eine moderne Halbleiter-Prozesstechnologie zum Einsatz, mit der die gegensätzlichen Anforderungen von hoher Verarbeitungsleistung bei gemischten Lasten und geringem Stromverbrauch erfüllt werden können.

Hohe Rechenleistung mit niedriger Leistungsaufnahme

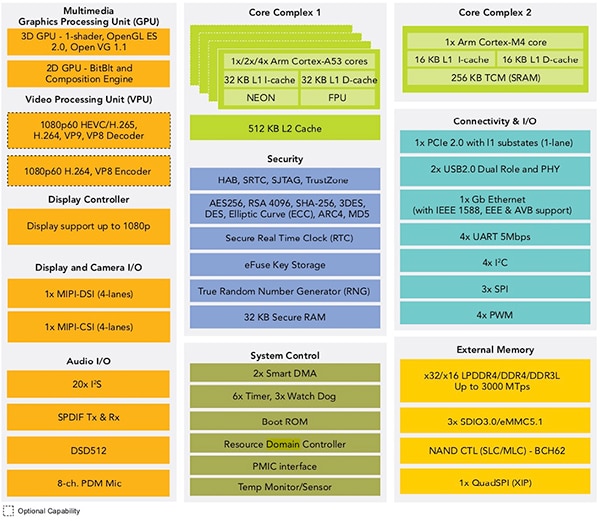

Als erste HMP-Familie von NXP, die in 14-nm-FinFET-Technologie gefertigt ist, sind die Prozessoren i.MX 8M Mini von NXP für Systeme für moderne Industrieanlagen und das Internet der Dinge (IoT) konzipiert, die hohe Leistung, zuverlässige Sicherheit und geringen Stromverbrauch erfordern. Ebenso wie die Familie i.MX 8M von NXP sind auch in die Prozessoren i.MX 8M Mini ein Arm-Cortex-M4 für die eingebettete Verarbeitung und bis zu vier Arm-Cortex-A53-Kerne zur Anwendungsverarbeitung integriert. Ebenfalls integriert sind ein umfassendes Sicherheits-Subsystem sowie mehrere Vernetzungs- und I/O-Optionen (Abbildung 2).

Abbildung 2: Der Prozessor i.MX 8M Mini kombiniert bis zu vier Arm-Cortex-A53-Anwendungsprozessorkerne und einen eingebetteten Arm-Cortex-M4-Prozessorkern mit einer Vielzahl von Sicherheits-, Multimedia-, System- und I/O-Schnittstellen, die für neue intelligente Produkte benötigt werden. (Bildquelle: NXP Semiconductors)

Um seiner Rolle in Embedded-Designs gerecht zu werden, verringert der i.MX 8M Mini im Vergleich zum i.MX 8M von NXP die Anzahl der I/O-Kanäle und die hochauflösenden Funktionen seines Multimedia-Subsystems. Beispielsweise bieten die Komponenten i.MX 8M Mini inklusive kommerzieller (MIMX8MM6DVTLZAA) und industrieller (MIMX8MM6CVTKZAAA) Versionen eine GPU mit nur einem Shader und eine 1080p-VPU für 60 Hertz (Hz), während der i.MX 8M von NXP eine GPU mit vier Shadern und eine 4K-VPU bot. Andere Produkte aus der Familie i.MX 8M Mini inklusive kommerzieller (MIMX8MM5DVTLZAA) und industrieller (MIMX8MM5CVTKZAA) Komponenten verzichten sogar völlig auf die VPU. Wie beim i.MX 8M von NXP auch können die Entwickler beim i.MX 8M Mini für mehr Ausgewogenheit zwischen Performance und Kosten sorgen, indem sie die Prozessorunterstützung für mehrere Speichertypen nutzen, inklusive DDR3L (Double Data Rate 3 Low), DDR4 und LPDDR4 (Low Power DDR4).

Reduzierte Leistungsaufnahme

Um die Leistung weiter zu optimieren und den Stromverbrauch zu senken, können Entwickler die Möglichkeit des NXP i.MX 8M Mini nutzen, automatisch oder programmgesteuert in Betriebsmodi mit geringerem Stromverbrauch zu schalten. Unter bestimmten Bedingungen können die Anwendungskerne automatisch in den Leerlaufmodus schalten. Dabei werden GPU, VPU und Anwendungskerne abgeschaltet, während für den Großteil der internen Logik Clock-Gating aktiviert ist und der L2-Daten-Cache weiterhin mit Strom versorgt wird. In diesem Modus kann der Arm-Cortex-M4-Kern weiterhin eher traditionelle Embedded-Verarbeitungsaufgaben wie die Erfassung von Sensordaten ausführen.

Der Suspend-Modus ist der sparsamste Modus, indem im Vergleich zum Leerlaufmodus zusätzlich auch noch der DDRC (Double Data Rate Controller) deaktiviert wird, der die Speicherschnittstellen verwaltet. Im SNVS-Modus (Secure Non-Volatile Storage, sicherer nichtflüchtiger Speicher) schließlich werden nur noch die SNVS-Logik und der Echtzeit-Taktgeber mit Strom versorgt.

Die Reduzierung der Leistungsaufnahme durch die für den i.MX 8M verwendeten 14-nm-FinFET-Technologie kommt besonders im Suspend- und im SNVS-Modus zum Tragen. Beim i.MX 8M Mini mit FinFET werden im Suspend-Modus lediglich 7,81 Milliwatt (mW) aufgenommen. Beim früheren i.MX 8M wurden im von der Funktion her vergleichbaren Modus (dem sogenannten Tiefschlafmodus) 197 mW aufgenommen. Eine ähnliche Verringerung gilt für den SNVS-Modus. Hier nimmt der i.MX 8M Mini etwa 0,11 mW auf, wohingegen es beim i.MX 8M etwa 17 mW waren.

Bei all den Funktionsblöcken und präzise abgestimmten Betriebsmodi in komplexen Komponenten wie dem i.MX 8M Mini müssen die Entwickler zahlreiche strenge Implementierungsanforderungen beachten. Wie bei anderen Komponenten dieser Klasse auch kommen beim i.MX 8M Mini mehrere Stromversorgungskreise zum Einsatz, um die Energieverwaltung und den Wirkungsgrad zu optimieren. Um diese Komponenten zu starten und zu stoppen, müssen beim Ein- und Ausschalten vorgeschriebene Reihenfolgen strikt eingehalten werden.

Um den i.MX 8M Mini einzuschalten, wird zuerst eine Spannung (üblicherweise 1,8 Volt) an den GPIO-Vortreiber in der SNVS-Bank angelegt. Innerhalb von 2 Millisekunden (ms) (max. 2,4 ms) muss dann eine Spannung von 0,8 Volt (typisch) an die SNVS-Kernlogik angelegt werden. Im weiteren Verlauf dieses Prozesses müssen an die Pins des iMX 8M Mini in 12 weiteren Schritten der Reihe nach bestimmte Signale gesendet und Spannungen angelegt werden. Dabei muss jeder einzelne dieser Schritte innerhalb eines bestimmten Zeitintervalls zwischen 0,015 ms und 20 ms ausgeführt werden.

Zum Ausschalten der Komponente müssen die Schritte in umgekehrter Reihenfolge ausgeführt werden, jedoch mit einer einheitlichen Verzögerung von 10 ms zwischen den einzelnen Schritten. Werden diese Richtlinien nicht eingehalten, kann es in beiden Fällen passieren, dass die Komponente nicht bootet, dass beim Einschalten ein übermäßig hoher Strom fließt oder dass die Komponente schlimmstenfalls irreparabel beschädigt wird.

Das physikalische Design einer Leiterplatte für den Prozessor bringt eigene strenge Anforderungen mit sich. Für das 486-polige Gehäuse (14 mm x 14 mm) des Prozessors empfiehlt NXP eine Leiterplatte mit einem Lagenaufbau aus mindestens acht Lagen, wobei genügend Lagen für die Stromschienen vorgesehen werden sollten, um innerhalb der Richtlinien für den Spannungsabfall (IR-Drop) zu bleiben. Gleichzeitig muss das Leiterplattenlayout minimales Übersprechen zwischen Hochgeschwindigkeitsleitungen gewährleisten, inklusive derer für unterstützte Speicherkomponenten, die mit 1,5 Gigahertz (GHz) getaktet sind und 3000 Megatransfers pro Sekunde (MT/s) bieten.

Schnelle Entwicklung

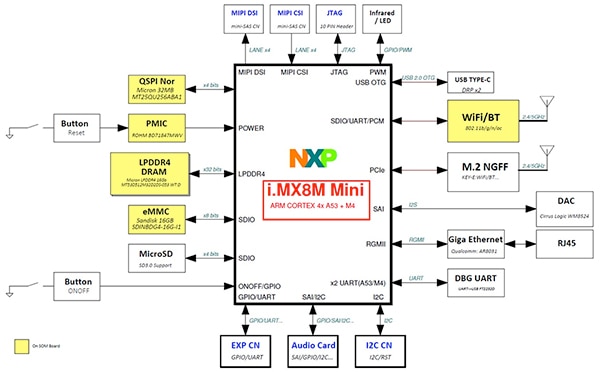

Damit Entwickler schnell mit der Anwendungsentwicklung beginnen oder die Entwicklung von kundenspezifischen Hardwaredesigns beschleunigen können, bietet NXP das NXP i.MX 8M Mini EVK (Evaluierungskit) und das zugehörige Referenzdesign an (Abbildung 3). Das als Grundplatine und System-on-Module (SOM) erhältliche Evaluierungskit bietet ein komplettes System inklusive externem LPDDR4-Speicher und Flash sowie USB- und weitere Schnittstellen.

Abbildung 3: Das Boardset i.MX 8M Mini EVK von NXP bietet eine komplette Systemplattform zur sofortigen Evaluierung der Prozessoren i.MX 8M Mini und zur schnellen Entwicklung von heterogenen Multicore-Prozessoranwendungen. (Bildquelle: NXP Semiconductors)

Neben Gigabit-Ethernet bietet das Kit Wi-Fi und Bluetooth als Netzwerkoptionen. Verfügbare Zusatzplatinen sind das Kameramodul MINISASTOCSI und der OLED-Touchscreen (Organic Light Emitting Diode) MX8-DSI-OLED1, die Video- und Anzeigeanwendungen ermöglichen.

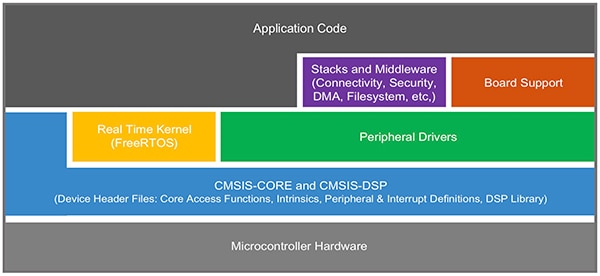

Mit vorgefertigten Images für die Betriebsumgebungen Embedded Linux® und Embedded Android® können die Entwickler das Kit sofort zur Evaluierung des Prozessors i.MX 8M Mini verwenden und Beispielanwendungen ausführen. Für Entwickler, die ihre eigenen Softwareanwendungen erstellen, bietet NXP das kostenlose MCUXpresso-SDK (Software Development Kit) an, das eine umfassende Auswahl an Softwarekomponenten zur Erstellung einer typischen eingebetteten Hochleistungsanwendung bietet (Abbildung 4).

Abbildung 4: Die Architektur des MCUXpresso-SDK (Software Development Kit) umfasst alle Softwareschichten inklusive Treibern, Board Support Package (BSP) und optionalen Komponenten, die zur Entwicklung der meisten eingebetteten Anwendungen erforderlich sind. (Bildquelle: NXP Semiconductors)

Über das MCUXpresso SDK Dashboard von NXP können Entwickler eine SDK-Konfiguration für die GCC Arm Embedded Toolchain oder die IAR Embedded Workbench für Arm zusammenstellen. Das Dashboard ermöglicht Entwicklern außerdem das Hinzufügen optionaler Middleware-Komponenten wie beispielsweise der DSP-Bibliothek des Arm CMSIS (Cortex Microcontroller Software Interface Standard) und Amazon FreeRTOS. Das konfigurierte SDK-Verteilungspaket enthält die Arm-Standardbibliotheken, Treiber für Peripheriebausteine sowie die Wrapper für FreeRTOS und eine große Auswahl an Softwarebeispielen. Unter den Softwarebeispielen im SDK-Verteilungspaket befinden sich einige Anwendungen mit einem wichtigen Designmuster für den Nachrichtenaustausch, das für heterogene Berechnungen unerlässlich ist.

In jeder Multicore-Computing-Umgebung erfordern separate Prozessoren effiziente Mechanismen zur Weiterleitung von Anfragen und für die gemeinsame Nutzung von Daten. Für die Anwendungen des i.MX 8M Mini EVK verwendet NXP RPMsg-Lite, eine abgespeckte Version des RPMsg-Protokolls (Remote Processor Messaging). Das RPMsg-Protokoll ist Bestandteil des OpenAMP-Frameworks (Open Asymmetric Multi Processing) zur Bereitstellung einer Standardschnittstelle für die Kommunikation zwischen mehreren Kernen in einem heterogenen Multicore-System. RPMsg-Lite von NXP ist für Ressourcenbeschränkungen in kleineren Embedded-Systemen konzipiert, indem es eine kompaktere Bauweise ermöglicht und Merkmale eliminiert, die nicht im Einklang mit diesen Systemen sind.

Im SDK-Verteilungspaket befindet sich die Beispielanwendung rpmsg_lite_pingpong_rtos. Sie demonstriert einen Barebone-Austausch, indem sie RPMsg-Lite verwendet, um eine einfache Ping-Pong-Interaktion zwischen verschiedenen Prozessoren zu implementieren (Listing 1). Nach dem Erstellen einer RPMsg-Warteschlange (my_queue) und einem Endpunkt (my_ept) für den anderen „Remote“-Prozessor, sendet der „Host“-Anwendungsprozessor ein Signal an den Remote-Kern. Nach dem Empfang der Handshake-Antwort vom Remote-Kern beginnt der Host mit einer Schleife, die eine blockierende Wartezeit für eine „Ping“-Meldung vom Remote-Kern verwendet, bevor er seine eigene „Pong“-Antwort sendet.

Kopieren

void app_task(void *param)

{

.

.

.

my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS);

while (!rpmsg_lite_is_link_up(my_rpmsg))

;

PRINTF("Link is up!\r\n");

my_queue = rpmsg_queue_create(my_rpmsg);

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue);

ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL);

rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE);

PRINTF("Nameservice announce sent.\r\n");

/* Wait Hello handshake message from Remote Core. */

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK);

while (msg.DATA <= 100)

{

PRINTF("Waiting for ping...\r\n");

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL,

RL_BLOCK);

msg.DATA++;

PRINTF("Sending pong...\r\n");

rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK);

}

PRINTF("Ping pong done, deinitializing...\r\n");

rpmsg_lite_destroy_ept(my_rpmsg, my_ept);

my_ept = NULL;

rpmsg_queue_destroy(my_rpmsg, my_queue);

my_queue = NULL;

rpmsg_ns_unbind(my_rpmsg, ns_handle);

rpmsg_lite_deinit(my_rpmsg);

msg.DATA = 0;

.

.

.

}

Listing 1: Dieses Snippet aus einem Beispielcode im MCUXpresso-SDK demonstriert das grundlegende Designmuster für Interaktionen zwischen verschiedenen Prozessoren in einem heterogenen Multicore-Prozessor. (Code-Quelle: NXP Semiconductors)

Entwickler können aufbauend auf diesem einfachen Austausch vollständige Vorgänge erstellen, um die Aufgabenausführung auf mehrere Prozessoren zu verteilen. Eine weitere Beispielanwendung, sai_low_power_audio, nutzt RPMsg-Lite im Wesentlichen als eine Low-Level-Datenverbindungsschicht für ein höherwertiges SRTM-Anwendungsprotokoll (Simplified Real Time Messaging). In dieser Anwendung verwendet ein Arm-Cortex-A53-Prozessor dieses SRTM-Protokoll, um den Arm-Cortex-M4-Prozessor aufzufordern, eine Audiodatei aus dem gemeinsamen Speicher wiederzugeben. Nachdem er die Kontrolle über den gemeinsam genutzten Puffer übernommen hat, führt der M4 mehrere Vorgänge durch. Dabei führt er letztlich eine SDMA-Transaktion (Smart Direct Memory Access) durch, um die Daten in den entsprechenden Code und schließlich für die Audioausgabe an die serielle Audioschnittstelle (SAI, Serial Audio Interface) überträgt. Während dieses Vorgangs kann der A53-Kern in einen Energiesparmodus wechseln. Obwohl ihr Design etwas komplexer als die Ping-Pong-Anwendung ist, demonstriert die Beispielanwendung sai_low_power_audio, wie Entwickler heterogene Multicore-Prozessoren nutzen können, um in intelligenten Produkten die Leistung zu maximieren und den Stromverbrauch zu minimieren.

Fazit

Intelligente Produkte kombinieren traditionelle eingebettete Echtzeitsysteme mit erheblicher Anwendungsverarbeitungsleistung. Die Entwickler müssen nun dafür Sorge tragen, dass diese Verarbeitungsanforderungen erfüllt werden. Außerdem wird von ihnen erwartet, dass die batterie- und netzbetriebenen Systeme immer weniger Strom verbrauchen.

Der mit einer modernen Halbleiter-Technologie gefertigte Anwendungsprozessor i.MX 8M Mini von NXP bietet die erforderliche Mischung aus geringem Stromverbrauch und hoher heterogener Multicore-Verarbeitungsleistung. Mit den Komponenten i.MX 8M Mini von NXP können die Entwickler effizienter auf neue Anforderungen hinsichtlich hoher Rechenleistung in Embedded-Systemen reagieren, die für immer ausgefeiltere intelligente Produkte erforderlich ist.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.