Warum und wie Efinix-FPGAs für KI/ML-Bildverarbeitung eingesetzt werden - Teil 2: Bilderfassung und -verarbeitung

Zur Verfügung gestellt von Europäische Fachredakteure von DigiKey

2023-05-05

Anmerkung des Herausgebers: Neue Ansätze für FPGA-Architekturen bieten eine feinere Steuerung und größere Flexibilität, um den Anforderungen des maschinellen Lernens (ML) und der künstlichen Intelligenz (KI) gerecht zu werden. Teil 1 dieser zweiteiligen Serie stellt eine solche Architektur von Efinix vor und zeigt, wie man sie mit Hilfe eines Entwicklungsboards einsetzen kann. Teil 2 befasst sich mit der Anbindung des Entwicklungsboards an externe Geräte und Peripheriegeräte wie z. B. eine Kamera und mit der Frage, wie der FPGA zur Beseitigung von Engpässen bei der Bildverarbeitung eingesetzt werden kann.

FPGAs spielen eine entscheidende Rolle in vielen Anwendungen, von der industriellen Steuerung und Sicherheit bis hin zur Robotik, Luft- und Raumfahrt und Automobiltechnik. Dank der flexiblen Natur des programmierbaren Logikkerns und ihrer umfangreichen Schnittstellenfähigkeiten liegt ein wachsender Anwendungsfall für FPGAs in der Bildverarbeitung, wo maschinelles Lernen (ML) eingesetzt werden kann. FPGAs sind dank ihrer parallelen Logikstruktur ideal für die Implementierung von Lösungen mit mehreren Highspeed-Kameraschnittstellen. Darüber hinaus ermöglichen FPGAs die Verwendung einer eigenen Verarbeitungspipeline in der Logik, wodurch Engpässe bei der gemeinsamen Nutzung von Ressourcen vermieden werden, die bei CPU- oder GPU-basierten Lösungen auftreten würden.

Dieser zweite Blick auf die Titanium-FPGAs von Efinix befasst sich mit der Referenzanwendung für die Bildverarbeitung, die mit dem Entwicklungsboard Ti180 M484 des FPGAs geliefert wird. Ziel ist es, die Bestandteile des Entwurfs zu verstehen und festzustellen, wo die FPGA-Technologie die Beseitigung von Engpässen ermöglicht oder andere Vorteile für die Entwickler bietet.

Das Ti180-M484-basierte Referenzdesign

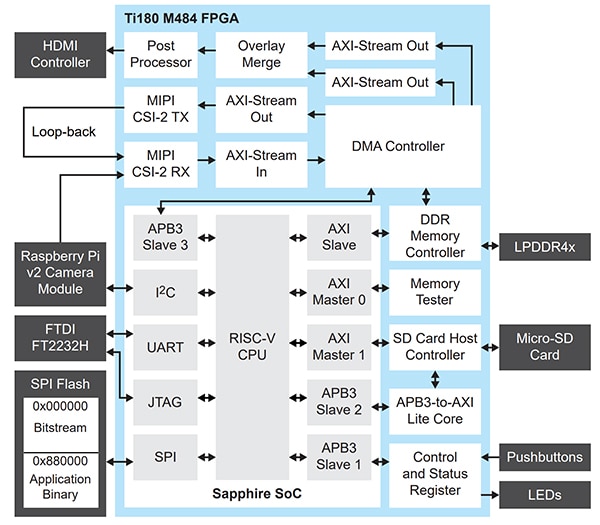

Das Referenzdesign (Abbildung 1) empfängt Bilder von mehreren MIPI-Kameras (Mobile Industry Processor Interface), führt eine Bildpufferung im LPDDR4x durch und gibt die Bilder dann an ein HDMI-Display (High Definition Multimedia Interface) aus. Eine FPGA-Mezzanine-Karte (FMC) und vier QSE-Schnittstellen von Samtec auf dem Board werden für die Kameraeingänge und den HDMI-Ausgang verwendet.

Abbildung 1: Das Ti180-M484-Referenzdesign empfängt Bilder von mehreren MIPI-Kameras, führt eine Bildpufferung im LPDDR4x durch und gibt die Bilder dann an ein HDMI-Display aus. (Bildquelle: Efinix)

Abbildung 1: Das Ti180-M484-Referenzdesign empfängt Bilder von mehreren MIPI-Kameras, führt eine Bildpufferung im LPDDR4x durch und gibt die Bilder dann an ein HDMI-Display aus. (Bildquelle: Efinix)

Die FMC-zu-QSE-Erweiterungskarte wird in Verbindung mit der HDMI-Tochterkarte verwendet, um den Ausgangsvideopfad bereitzustellen, während drei QSE-Anschlüsse für die Schnittstelle mit den MIPI-Kameras SEN0494 von DFRobot verwendet werden. Wenn nicht mehrere MIPI-Kameras zur Verfügung stehen, kann eine einzelne Kamera verwendet werden, indem der einzelne Kamerakanal zurückgeschleift wird, um zusätzliche Kameras zu simulieren.

Auf den ersten Blick scheint diese Anwendung einfach zu sein. Der Empfang mehrerer hochauflösender (HD) MIPI-Streams mit hoher Bildrate ist jedoch eine Herausforderung. Hier ist die FPGA-Technologie von Vorteil, da sie es den Entwicklern ermöglicht, mehrere MIPI-Streams parallel zu nutzen.

Die Architektur des Referenzdesigns nutzt sowohl parallele als auch sequentielle Verarbeitungsstrukturen mit dem FPGA. Die parallelen Strukturen werden zur Implementierung der Bildverarbeitungspipeline verwendet, während ein RISC-V-Prozessor die sequentielle Verarbeitung für die FPGA-Look-up-Tables (LUTs) übernimmt.

In vielen FPGA-basierten Bildverarbeitungssystemen kann die Bildverarbeitungspipeline in zwei Elemente unterteilt werden, nämlich in den Eingangs- und den Ausgangsstrom. Der Eingangsstrom wird an die Kamera-/Sensorschnittstelle angeschlossen, und die Verarbeitungsfunktionen werden auf den Sensorausgang angewendet. Diese Funktionen können Bayer-Konvertierung, automatischen Weißabgleich und andere Verbesserungen umfassen. Im Ausgabestrom wird das Bild für die Anzeige vorbereitet. Dazu gehören das Ändern des Farbraums (z. B. von RGB zu YUV) und die Nachbearbeitung für das gewünschte Ausgabeformat, wie z. B. HDMI.

Häufig arbeitet die Eingangsbildverarbeitungskette mit der Pixeltaktrate des Sensors. Diese hat ein anderes Timing als die Ausgangskette, die mit der Frequenz der Ausgangsanzeige verarbeitet wird.

Ein Bildpuffer wird verwendet, um die Eingabe mit der Ausgabeverarbeitungspipeline zu verbinden, die häufig in einem externen Hochleistungsspeicher, wie z. B. LPDDR4x, gespeichert ist. Dieser Bildpuffer entkoppelt die Eingangs- und Ausgangspipelines und ermöglicht den Zugriff auf den Bildpuffer über direkten Speicherzugriff mit der entsprechenden Taktfrequenz.

Das Ti180-Referenzdesign verwendet einen ähnlichen Ansatz wie die oben beschriebenen Konzepte. Die Eingangsbildverarbeitungspipeline implementiert einen MIPI-CSI-2-Receiver-IP-Kern (CSI-2: Camera Serial Interface 2, IP: Intellectual Property), der auf den MIPI-D-PHY-fähigen (PHY: Physical Layer) Ein-/Ausgängen (I/O) des Titanium-FPGAs aufgebaut ist. MIPI ist eine anspruchsvolle Schnittstelle, da sie sowohl referenzbezogene als auch Differenzsignale auf demselben Differenzpaar verwendet, zusätzlich zu Low-Speed- und High-Speed-Kommunikation. Durch die Integration des MIPI D-PHY in die FPGA-I/O wird die Komplexität des Leiterplattendesigns verringert und gleichzeitig die Stückliste reduziert.

Nach dem Empfang des Bildstroms von der Kamera wandelt das Referenzdesign den Ausgang des MIPI CSI-2 RX in einen AXI-Stream (AXI: Advanced eXtensible Interface) um. Ein AXI-Stream ist eine unidirektionale Highspeed-Schnittstelle, die einen Datenstrom von einem Master zu einem Slave liefert. Handshaking-Signale für die Übertragung zwischen einem Master und einem Slave werden zusammen mit Seitenbandsignalen bereitgestellt (tvalid und tready). Diese Seitenbandsignale können zur Übermittlung von Bildzeitinformationen wie Bildanfang und Zeilenende verwendet werden.

AXI Stream ist ideal für Bildverarbeitungsanwendungen und ermöglicht es Efinix, eine Reihe von Bildverarbeitungs-IPs bereitzustellen, die je nach Anforderung der Anwendung einfach in die Verarbeitungskette integriert werden können.

Nach dem Empfang werden die MIPI-CSI-2-Bilddaten und Timing-Signale in einen AXI-Stream umgewandelt und in ein DMA-Modul (Direct Memory Access) eingegeben, das den Bildrahmen in den LPDDR4x schreibt und als Bildpuffer dient.

Dieses DMA-Modul arbeitet unter der Kontrolle des RISC-V-Kerns im FPGA innerhalb eines Sapphire-SoC (SoC: System on Chip). Dieser SoC ermöglicht die Steuerung, z. B. das Stoppen und Starten von DMA-Schreibvorgängen, und versorgt den DMA-Schreibkanal mit den notwendigen Informationen, um die Bilddaten korrekt in den LPDDR4x zu schreiben. Dazu gehören Informationen über den Speicherort sowie die Breite und Höhe des Bildes in Bytes.

Der Ausgangskanal im Referenzdesign liest die Bildinformationen aus dem LPDDR4x-Bildpuffer unter der Kontrolle des RISC-V-SoC. Die Daten werden von der DMA-IP als AXI-Stream ausgegeben, der dann vom RAW-Format, das vom Sensor bereitgestellt wird, in das RGB-Format konvertiert wird (Abbildung 2) und über den integrierten HDMI-Sender ADV7511 von Analog Devices für die Ausgabe vorbereitet wird.

Abbildung 2: Beispielbildausgabe aus dem Referenzdesign. (Bildquelle: Adam Taylor)

Abbildung 2: Beispielbildausgabe aus dem Referenzdesign. (Bildquelle: Adam Taylor)

Die Verwendung des DMA ermöglicht dem Sapphire-SoC-RISC-V auch den Zugriff auf die im Bildpuffer gespeicherten Bilder sowie auf die abstrakten Statistiken und Bildinformationen. Der Sapphire-SoC ist auch in der Lage, Overlays in den LPDDR4x zu schreiben, so dass sie mit dem ausgegebenen Videostrom zusammengeführt werden können.

Moderne CMOS-Bildsensoren (CIS) verfügen über mehrere Betriebsmodi und können so konfiguriert werden, dass sie eine On-Chip-Verarbeitung sowie mehrere verschiedene Ausgabeformate und Taktschemata bieten. Diese Konfiguration wird normalerweise über eine I²C-Schnittstelle vorgenommen. Im Efinix-Referenzdesign wird diese I²C-Kommunikation zu den MIPI-Kameras durch den Sapphire-SoC-RISC-V-Prozessor bereitgestellt.

Durch die Integration des RISC-V-Prozessors in das Titanium-FPGA wird die Gesamtgröße der endgültigen Lösung reduziert, da die Notwendigkeit entfällt, sowohl komplexe FPGA-Zustandsmaschinen zu implementieren, die das Designrisiko erhöhen, als auch externe Prozessoren, die die Stückliste vergrößern.

Die Einbeziehung des Prozessors ermöglicht auch die Unterstützung mit zusätzlicher IP für die Kommunikation mit der MicroSD-Karte. Dies ermöglicht reale Anwendungen, bei denen die Bilder für eine spätere Analyse gespeichert werden müssen.

Insgesamt ist die Architektur des Ti180-Referenzdesigns so optimiert, dass eine kompakte, kostengünstige und dennoch leistungsstarke Lösung entsteht, die es Entwicklern ermöglicht, die Stücklistenkosten durch Systemintegration zu senken.

Einer der Hauptvorteile von Referenzdesigns besteht darin, dass sie als Starthilfe für die Entwicklung von Anwendungen auf kundenspezifischer Hardware verwendet werden können, so dass die Entwickler wichtige Elemente des Designs übernehmen und mit den erforderlichen Anpassungen darauf aufbauen können. Dazu gehört auch die Möglichkeit, den TinyML-Flow von Efinix zu nutzen, um bildverarbeitungsbasierte TinyML-Anwendungen auf dem FPGA zu implementieren. Dadurch können sowohl die Parallelität der FPGA-Logik als auch die Fähigkeit, benutzerdefinierte Befehle in RISC-V-Prozessoren einzufügen, genutzt werden, was die Erstellung von Beschleunigern innerhalb der FPGA-Logik ermöglicht.

Implementierung

Wie in Teil 1 beschrieben, ist die Efinix-Architektur insofern einzigartig, als sie austauschbare Logik- und Routing-Zellen (XLR) verwendet, um sowohl Routing- als auch Logikfunktionen bereitzustellen. Bei einem Videosystem wie dem Referenzdesign handelt es sich um ein gemischtes System, das sowohl logik- als auch routinglastig ist: Für die Implementierung der Bildverarbeitungsfunktionen ist eine umfangreiche Logik erforderlich, und für die Verbindung der IP-Zellen mit den erforderlichen Frequenzen ist ein umfangreiches Routing notwendig.

Das Referenzdesign nutzt ca. 42 % der XLR-Zellen innerhalb des Geräts und lässt reichlich Raum für Erweiterungen, einschließlich kundenspezifischer Anwendungen wie Edge ML.

Die Nutzung des Block-RAM und der digitalen Signalverarbeitungsblöcke (DSP) ist ebenfalls sehr effizient, da nur 4 der 640 DSP-Blöcke und 40 % der Speicherblöcke verwendet werden (Abbildung 3).

|

Abbildung 3: Die Ressourcenzuweisung auf der Efinix-Architektur zeigt, dass nur 42 % der XLR-Zellen genutzt werden, was reichlich Platz für zusätzliche Prozesse lässt. (Bildquelle: Adam Taylor)

Am Baustein-IO wird die DDR-Schnittstelle für LPDDR4x verwendet, um den Anwendungsspeicher für den Sapphire-SoC und die Bildrahmenpuffer bereitzustellen. Alle gerätespezifischen MIPI-Ressourcen werden zusammen mit 50 % der Phasenregelschleifen genutzt (Abbildung 4).

|

Abbildung 4: Momentaufnahme der Schnittstelle und der verwendeten I/O-Ressourcen. (Bildquelle: Adam Taylor)

Die Allzweck-I/O (GPIO) wird für die I²C-Kommunikation zusammen mit mehreren an den Sapphire-SoC angeschlossenen Schnittstellen verwendet, einschließlich NOR FLASH, USB UART und SD-Karte. Die HSIO wird verwendet, um die Highspeed-Videoausgabe an den HDMI-Sender ADC7511 zu leiten.

Eines der entscheidenden Elemente beim Design mit FPGAs ist nicht nur die Implementierung und Anpassung des Designs innerhalb des FPGAs, sondern auch die Fähigkeit, das Logikdesign innerhalb des FPGAs zu platzieren und die erforderliche Timing-Leistung beim Routing zu erreichen.

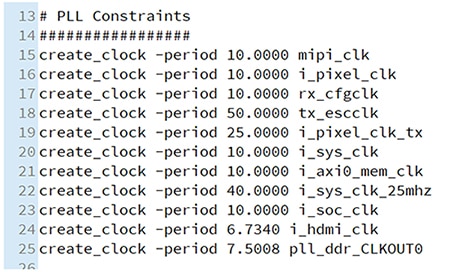

Die Zeiten der FPGA-Designs mit nur einer Taktdomäne sind längst vorbei. Im Ti180-Referenzdesign gibt es mehrere verschiedene Taktgeber, die alle mit hohen Frequenzen laufen. Die abschließende Timing-Tabelle zeigt die maximalen Frequenzen, die für die Takte innerhalb des Systems erreicht werden. Hier zeigt sich die geforderte Timing-Performance auch in den Constraints (Abbildung 5), die eine maximale Taktfrequenz von 148,5 Megahertz (MHz) für den HDMI-Ausgangstakt vorsehen.

Abbildung 5: Takteinschränkungen für das Referenzdesign. (Bildquelle: Adam Taylor)

Abbildung 5: Takteinschränkungen für das Referenzdesign. (Bildquelle: Adam Taylor)

Die Timing-Implementierung unter Berücksichtigung der Einschränkungen zeigt das Potenzial der XLR-Struktur des Titanium-FPGA, da sie die mögliche Routing-Verzögerung reduziert und dadurch die Designleistung erhöht (Abbildung 6).

|

Abbildung 6: Die Timing-Implementierung im Vergleich zu den Einschränkungen zeigt das Potenzial der XLR-Struktur des Titanium-FPGA zur Verringerung der möglichen Routing-Verzögerung und damit zur Steigerung der Designleistung. (Bildquelle: Adam Taylor)

Fazit

Das Ti180-M484-Referenzdesign zeigt deutlich die Fähigkeiten der Efinix-FPGAs und insbesondere des Ti180. Das Design nutzt mehrere der einzigartigen I/O-Strukturen zur Implementierung eines komplexen Bildverarbeitungspfads, der mehrere eingehende MIPI-Streams unterstützt. Dieses Bildverarbeitungssystem arbeitet unter der Kontrolle eines Soft-Core-Sapphire-SoCs, der die notwendigen sequentiellen Verarbeitungselemente der Anwendung implementiert.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.