Warum und wie Efinix-FPGAs für KI/ML-Bildverarbeitung eingesetzt werden - Teil 1: Einführung

Zur Verfügung gestellt von Europäische Fachredakteure von DigiKey

2023-04-20

Anmerkung des Herausgebers: Neue Ansätze für FPGA-Architekturen bieten eine feinere Steuerung und größere Flexibilität, um den Anforderungen des maschinellen Lernens (ML) und der künstlichen Intelligenz (KI) gerecht zu werden. Teil 1 dieser zweiteiligen Serie stellt eine solche Architektur von Efinix vor und zeigt, wie man sie mit Hilfe eines Entwicklungsboards einsetzen kann. Teil 2 befasst sich mit der Anbindung des Entwicklungsboards an externe Geräte und Peripheriegeräte, wie z. B. eine Kamera.

FPGAs spielen eine entscheidende Rolle in vielen Anwendungen, von der industriellen Steuerung und Sicherheit bis hin zur Robotik, Luft- und Raumfahrt und Automobiltechnik. Dank der flexiblen Natur des programmierbaren Logikkerns und ihrer umfangreichen Schnittstellenfähigkeiten liegt ein wachsender Anteil von Anwendungen für FPGAs in der Bildverarbeitung, wenn ML-Inferenz eingesetzt werden soll. FPGAs sind ideal für die Implementierung von Lösungen, die mehrere Highspeed-Kameraschnittstellen enthalten. Darüber hinaus ermöglichen FPGAs auch die Implementierung dedizierter Verarbeitungspipelines in der Logik, wodurch Engpässe, die bei CPU- oder GPU-basierten Lösungen auftreten würden, vermieden werden.

Viele Entwickler benötigen für ihre Anwendungen jedoch mehr ML/KI-Funktionen und eine feinere Steuerung oder ein feineres Routing und Logik, die über das hinausgehen, was klassische FPGA-Architekturen mit kombinatorischen Logikblöcken (CLBs) bieten können. Neuere Ansätze für FPGA-Architekturen gehen diese Probleme an. Die Quantum-Architektur von Efinix verwendet beispielsweise einen XLR-Block (eXchangeable Logic and Routing).

In diesem Artikel werden die wichtigsten Merkmale und Eigenschaften der Efinix-FPGA-Architektur erörtert, wobei die KI/ML-Fähigkeiten hervorgehoben und reale Implementierungen vorgestellt werden. Anschließend werden ein Entwicklungsboard und zugehörige Tools vorgestellt, mit denen Entwickler schnell mit ihrem nächsten Projekt zur KI/ML-Bildverarbeitung beginnen können.

FPGA-Komponenten von Efinix

Efinix bietet derzeit zwei Bauteilserien an. Das Unternehmen stellte zunächst die Trion-Familie vor, die Logikdichten von 4000 (4K) bis 120K Logikelementen (LEs) bietet und in einem SMIC-40LL-Prozess hergestellt wird. Die neueste Produktlinie, die Titanium-Familie, bietet Logikdichten von 35K bis 1 Million (1M) Logikelemente und wird auf dem sehr beliebten TSMC-16-Nanometer(nm)-Knoten gefertigt.

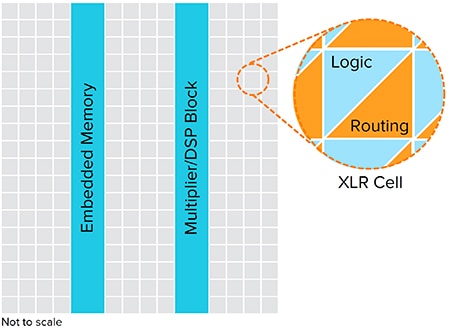

Beide Angebote basieren auf der Quantum-Architektur, die in der FPGA-Welt einzigartig ist. Die Standard-FPGA-Architektur basiert auf CLBs, die auf der einfachsten Ebene eine Look-up-Tabelle (LUT) und Flip-Flops enthalten. Die CLBs implementieren logische Gleichungen, die dann über Routing miteinander verbunden werden. Die Quantum-Architektur von Efinix löst sich mit dem XLR-Block von getrennten Logik- und Routing-Blöcken.

Das Besondere an einem XLR-Block ist, dass er als Logikzelle mit LUT, als Register und Addierer oder als Routing-Matrix konfiguriert werden kann. Dieser Ansatz bietet eine feinkörnige Architektur, die ein flexibles Routing ermöglicht, wodurch Implementierungen mit hohem Logik- oder Routing-Anteil die gewünschte Performance erreichen können.

Abbildung 1: Die Einzigartigkeit eines XLR-Blocks besteht darin, dass er so konfiguriert werden kann, dass er entweder als Logikzelle mit LUT, als Register und Addierer oder als Routing-Matrix funktioniert. (Bildquelle: Efinix)

Abbildung 1: Die Einzigartigkeit eines XLR-Blocks besteht darin, dass er so konfiguriert werden kann, dass er entweder als Logikzelle mit LUT, als Register und Addierer oder als Routing-Matrix funktioniert. (Bildquelle: Efinix)

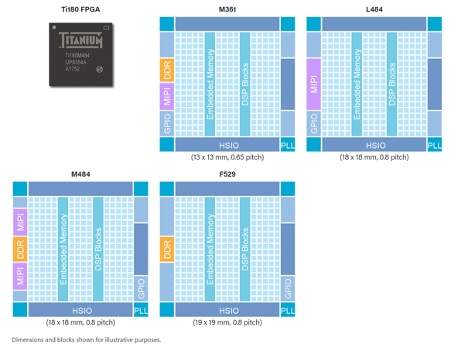

Als neueste Familie bieten die Titanium-Komponenten die modernsten Funktionen für den Entwickler (Abbildung 2). Zusammen mit dem XLR-Kern bieten sie serielle Multi-Gigabit-Verbindungen, die je nach gewählter Komponente entweder mit 16 Gigabit pro Sekunde (Gbit/s) oder 25,8 Gbit/s arbeiten. Diese Multi-Gigabit-Verbindungen sind für den Highspeed-Datentransfer auf und außerhalb des Chips entscheidend.

Abbildung 2: Das Titanium-FPGA Ti180 ist in einer Vielzahl von Optionen erhältlich, die von der Busbreite, den I/O- und Speicheranforderungen abhängen. (Bildquelle: Efinix)

Abbildung 2: Das Titanium-FPGA Ti180 ist in einer Vielzahl von Optionen erhältlich, die von der Busbreite, den I/O- und Speicheranforderungen abhängen. (Bildquelle: Efinix)

Titanium-Bausteine bieten außerdem eine breite Palette von Ein-/Ausgabe-Schnittstellen (I/O), die als allgemeine I/O (GPIO) gruppiert werden können und referenzbezogene I/O-Standards wie Niedrigspannungs-CMOS (LVCMOS) mit 3,3 Volt, 2,5 Volt und 1,8 Volt unterstützen.

Für Highspeed- und Differenzschnittstellen bieten die Titanium-Bausteine Highspeed-I/O (HSIO), die referenzbezogene I/O-Standards wie LVCMOS bei 1,2 Volt, 1,5 Volt sowie SSTL und HSTL unterstützen. Zu den von HSIO unterstützten differenziellen I/O-Standards gehören LVDS (Low-Voltage Differential Signaling), differentielle SSTL und HSTL.

Moderne FPGAs benötigen auch einen eng gekoppelten Speicher mit hoher Bandbreite, der zur Speicherung von Image-Frames für Bildverarbeitungsanwendungen, von Abtastdaten für die Signalverarbeitung und natürlich zur Ausführung von Betriebssystemen und Software für im FPGA implementierte Prozessoren verwendet wird. Die Titanium-Bausteine bieten Schnittstellen zu DDR4 (Dynamic Data Rate Four) und LPDDR4(x) (Low-Power DDR4(x)). Je nach ausgewählter Titanium-Komponente wird eine Busbreite von x32 (J) oder x16 (M) unterstützt, während einige Komponenten keine LPDDR4-Unterstützung bieten (L).

Titanium-FPGAs sind SRAM-basiert und benötigen einen Konfigurationsspeicher, wobei die Bauteilkonfiguration entweder über Master/Slave-SPI oder JTAG erfolgt. Um die Sicherheit dieser Konfigurationsmethode zu gewährleisten, verwendet der Titanium-FPGA eine AES-GCM-Verschlüsselung des Bitstreams sowie AES GCM und RSA-4096 zur Bitstream-Authentifizierung. Eine starke Sicherheit wie diese ist erforderlich, da FPGAs am Netzwerkrand (Edge) eingesetzt werden, wo böswillige Akteure auf sie zugreifen und ihr Verhalten manipulieren könnten.

Einführung von Entwicklungsbords

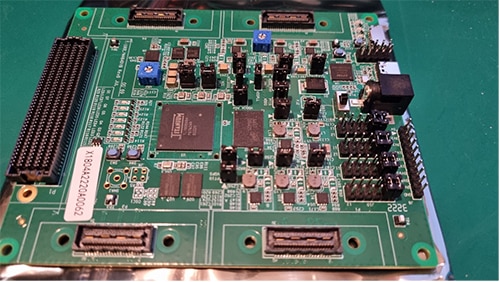

Entwicklungsboards sind ein entscheidendes Element des FPGA-Evaluierungsprozesses, da sie dazu verwendet werden können, die Fähigkeiten eines Bausteins und Prototypanwendungen zu erforschen und so das Gesamtrisiko zu verringern. Das erste Entwicklungsboard, das für die Evaluierung von Titanium-FPGAs und die Entwicklung von Prototyping-Anwendungen verfügbar ist, ist das Ti180 M484 (Abbildung 3). Das Board verfügt über einen Anschluss für eine FPGA Mezzanine Card (FMC) und vier Samtec-QSE-Anschlüsse.

Abbildung 3: Neben einem Titanium-FPGA verfügt das Entwicklungskit Ti180 M484 über einen FMC-Anschluss und vier Samtec-QSE-Anschlüsse. (Bildquelle: Adam Taylor)

Abbildung 3: Neben einem Titanium-FPGA verfügt das Entwicklungskit Ti180 M484 über einen FMC-Anschluss und vier Samtec-QSE-Anschlüsse. (Bildquelle: Adam Taylor)

Der Ti180-FPGA, mit dem dieses Entwicklungsboard ausgestattet ist, bietet 172K XLR-Zellen, 32 globale Taktgeber, 640 digitale Signalverarbeitungselemente (DSP) und 13 Megabit (Mbit) eingebetteten RAM. Die DSP-Elemente bieten die Möglichkeit, Festkomma-Multiplikationen mit 18x19- und 48-Bit-Multiplikationen durchzuführen. Dieser DSP kann auch für SIMD-Operationen (Single Instruction, Multiple Data) optimiert werden, die entweder in einer Dual- oder Quad-Konfiguration ausgeführt werden. DSP-Elemente können auch so konfiguriert werden, dass sie Gleitkommaoperationen durchführen.

Wie die meisten Entwicklungsboards verfügt auch das Ti180-Entwicklungsboard über einfache LEDs und Tasten. Seine wahre Stärke liegt jedoch in seinen Schnittstellen. Das Ti180-Entwicklungsboard verfügt über einen FMC-Anschluss mit geringer Pinzahl, an den eine Vielzahl von Peripheriekomponenten angeschlossen werden kann. Da es sich um einen weit verbreiteten Standard handelt, gibt es viele FMC-Karten, die die Anbindung von Highspeed-Analog/Digital-Wandlern (ADC), Digital/Analog-Wandlern (DAC), Netzwerken und Speicherlösungen ermöglichen.

Zusätzlich zum FMC-Anschluss verfügt das Board über vier Samtec-QSE-Anschlüsse, über die der Entwickler Erweiterungskarten hinzufügen kann. Diese QSE-Anschlüsse werden zur Bereitstellung von MIPI-Eingängen und -Ausgängen verwendet, wobei jeder QSE-Anschluss entweder einen MIPI-Eingang oder einen -Ausgang bereitstellt.

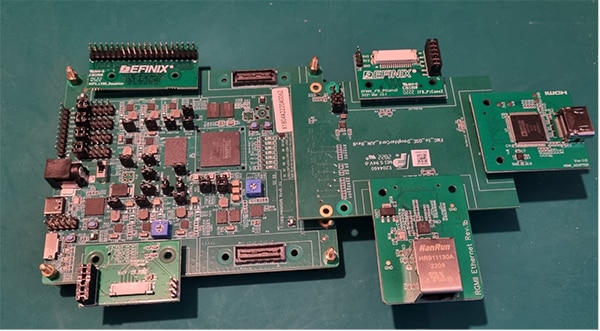

Abbildung 4: Das Entwicklungskit Ti180 M484 mit seinen vielseitigen Erweiterungsmöglichkeiten auf Basis von QSE- und FMC-Anschlüssen. (Bildquelle: Adam Taylor)

Abbildung 4: Das Entwicklungskit Ti180 M484 mit seinen vielseitigen Erweiterungsmöglichkeiten auf Basis von QSE- und FMC-Anschlüssen. (Bildquelle: Adam Taylor)

Das Ti180-Board bietet außerdem 256 MBit LPDDR4, um den Hochleistungsspeicher zu unterstützen, der für Bild- oder Signalverarbeitungsanwendungen erforderlich ist. Darüber hinaus bietet das Entwicklungsboard eine Reihe von Taktoptionen mit 25, 33,33, 50 und 74,25 Megahertz (MHz), die zusammen mit der Phasenregelschleife (PLL) des Bausteins verwendet werden können, um verschiedene interne Frequenzen zu erzeugen.

Die Möglichkeit zur Neuprogrammierung und zum Live-Debugging auf dem Board während der Entwicklung ist entscheidend und erfordert eine JTAG-Verbindung, die über eine USB-C-Schnittstelle auf dem Board bereitgestellt wird. Außerdem gibt es einen nichtflüchtigen Speicher in Form von zwei 256-Mbit-NOR-Flash-Bausteinen, die zur Demonstration der Konfigurationslösung verwendet werden können.

Das Board wird über ein 12-Volt-Universalnetzteil betrieben, das im Lieferumfang enthalten ist. Außerdem ist ein FMC-zu-QSE-Breakout-Board enthalten, zusammen mit QSE-basierten Erweiterungskarten für HDMI, Ethernet, MIPI und LVDS. Zur Veranschaulichung der Ti180-Bildverarbeitungsfähigkeiten werden auch eine Dual-RPI-Tochterkarte und zwei IMX477-Kamerakarten bereitgestellt.

Die Softwareumgebung

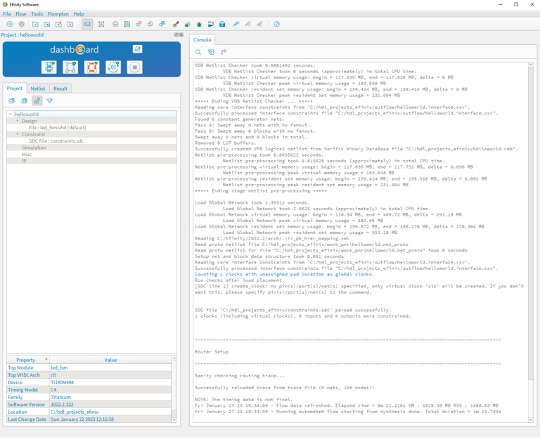

Zur Implementierung von Designs für das Ti180-Entwicklungsboard wird die Efinix-Software Efinity verwendet. Die Software ermöglicht die Erzeugung eines Bitstroms über Synthese und Place and Route. Außerdem bietet es Entwicklern IP-Blöcke (Intellectual Property), Timing-Analyse und On-Chip-Debugging.

Beachten Sie, dass für den Zugriff auf die Efinity-Software ein Entwicklungsboard erforderlich ist. Im Gegensatz zu anderen Anbietern gibt es jedoch keine verschiedenen Versionen des Tools, die eine zusätzliche Lizenzierung erfordern.

In Efinity werden neue Projekte erstellt, die auf die ausgewählte Komponente ausgerichtet sind. Anschließend können RTL-Dateien zum Projekt hinzugefügt und Einschränkungen für das Timing und das I/O-Design erstellt werden. Innerhalb von Efinity können Entwickler auch das I/O-Design implementieren und HSIO, GPIO und spezialisierte I/O nutzen.

Abbildung 5: In Efinity werden neue Projekte erstellt, die auf die ausgewählte Komponente ausgerichtet sind. (Bildquelle: Adam Taylor)

Abbildung 5: In Efinity werden neue Projekte erstellt, die auf die ausgewählte Komponente ausgerichtet sind. (Bildquelle: Adam Taylor)

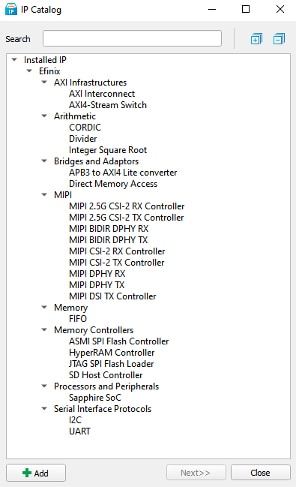

Ein entscheidendes Element des FPGA-Designs ist die Nutzung von IP, insbesondere für komplexe IP wie AXI-Verbindungen, Speicher-Controller und Softcore-Prozessoren. Efinity bietet Entwicklern eine Reihe von IP-Blöcken, die zur Beschleunigung des Designprozesses verwendet werden können.

Abbildung 6: Efinity stellt Entwicklern einen IP-Katalog zur Verfügung, mit dem sie den Designprozess beschleunigen können. (Bildquelle: Adam Taylor)

Abbildung 6: Efinity stellt Entwicklern einen IP-Katalog zur Verfügung, mit dem sie den Designprozess beschleunigen können. (Bildquelle: Adam Taylor)

FPGAs eignen sich zwar hervorragend zur Implementierung paralleler Verarbeitungsstrukturen, aber viele FPGA-Designs enthalten Softcore-Prozessoren. Diese bieten die Möglichkeit, sequentielle Verarbeitung, wie z. B. Netzwerkkommunikation, zu implementieren. Um den Einsatz der Softcore-Prozessoren in den Efinix-Komponenten zu ermöglichen, bietet Efinity das Sapphire-SoC-Konfigurationstool (SoC: System-on-Chip) an. Sapphire ermöglicht es dem Entwickler, ein Multiprozessorsystem zu definieren, das sowohl über Caches und Cache-Kohärenz über mehrere Prozessoren hinweg verfügt, als auch die Möglichkeit bietet, ein eingebettetes Linux-Betriebssystem auszuführen. Bei Sapphire kann der Entwickler zwischen einem und vier Softcore-Prozessoren wählen.

Bei dem implementierten Softcore-Prozessor handelt es sich um die VexRiscV-Soft-CPU, die auf der RISC-V-Befehlssatzarchitektur basiert. Der VexRiscV-Prozessor ist eine 32-Bit-Implementierung, die über Erweiterungen für Pipelining verfügt und einen konfigurierbaren Funktionssatz bietet, wodurch er sich ideal für die Implementierung in Efinix-Komponenten eignet. Zu den optionalen Konfigurationen gehören ein Multiplikator, atomare Anweisungen, Gleitkomma-Erweiterungen und komprimierte Anweisungen. Je nach Konfiguration des SoC-Systems liegt die Leistung zwischen 0,86 und 1,05 DMIPS/MHz.

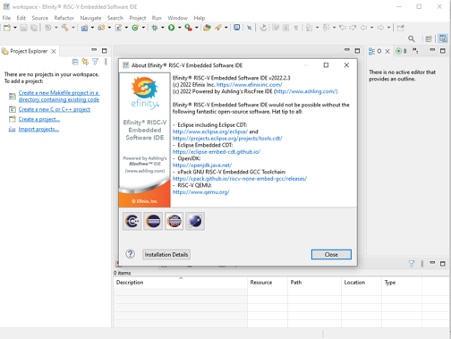

Sobald die Hardwareumgebung entworfen und im Efinix-Baustein implementiert wurde, kann die Anwendungssoftware mit der IDE Ashling RiscFree entwickelt werden. Ashling RiscFree ist eine auf Eclipse basierende IDE, die die Erstellung und Kompilierung von Anwendungssoftware sowie das Debugging auf dem Zielsystem zur Feinabstimmung der Anwendung vor der Bereitstellung ermöglicht.

Abbildung 7: Ashling RiscFree ist eine Eclipse-basierte IDE, die die Erstellung und Kompilierung von Anwendungssoftware sowie das Debugging auf dem Zielsystem ermöglicht. (Bildquelle: Adam Taylor)

Abbildung 7: Ashling RiscFree ist eine Eclipse-basierte IDE, die die Erstellung und Kompilierung von Anwendungssoftware sowie das Debugging auf dem Zielsystem ermöglicht. (Bildquelle: Adam Taylor)

Wenn eine eingebettete Linux-Lösung entwickelt wird, werden alle erforderlichen Boot-Artefakte bereitgestellt, einschließlich First Stage Boot Loader, OpenSBI, U-Boot und Linux mit Buildroot. Alternativ dazu kann der Entwickler FreeRTOS verwenden, wenn eine Echtzeitlösung erforderlich ist.

KI-Implementierung

Die KI-Implementierung von Efinix baut auf dem RISC-V-Softcore-Betrieb auf. Dies nutzt die Fähigkeit des RISC-V-Prozessors, benutzerdefinierte Befehle zu erteilen, um die Beschleunigung von TensorFlow-Lite-Lösungen zu ermöglichen. Die Verwendung des RISC-V-Prozessors ermöglicht es dem Benutzer außerdem, benutzerdefinierte Befehle zu erstellen, die als Teil der Vor- oder Nachverarbeitung im Anschluss an die KI-Inferenz verwendet werden können, wodurch eine reaktionsschnellere und deterministischere Lösung entsteht.

Um mit einer KI-Implementierung zu beginnen, ist der erste Schritt die Erkundung des Efinix-Modellzoos, einer Bibliothek von KI/ML-Modellen, die für die jeweilige Endtechnologie optimiert sind. Entwickler, die mit den Efinix-Komponenten arbeiten, können auf den Modell-Zoo zugreifen und das Netzwerk mit Jupyter Notebooks oder Google Colab trainieren. Sobald das Netz trainiert wurde, kann es mit dem TensorFlow-Lite-Konverter von einem Gleitkommamodell in ein quantisiertes Modell umgewandelt werden.

Sobald das TensorFlow-Lite-Format vorliegt, kann der tinyML-Beschleuniger von Efinix verwendet werden, um eine einsatzfähige Lösung auf der RISC-V-Lösung zu erstellen. Der tinyML-Generator ermöglicht es dem Entwickler, die Beschleunigerimplementierung anzupassen und die Projektdateien zu erzeugen. Bei dieser Art des Einsatzes kann die Beschleunigung je nach gewählter Architektur und Anpassung zwischen dem 4- und 200-fachen liegen.

Fazit

Die Komponenten von Efinix bieten Entwicklern dank ihrer einzigartigen XLR-Architektur eine hohe Flexibilität. Die Toolchain bietet die Möglichkeit, nicht nur RTL-Designs zu implementieren, sondern auch komplexe SoC-Lösungen mit Softcore-RISC-V-Prozessoren zu realisieren. Auf dem Softcore-SoC baut eine KI/ML-Lösung auf, die den Einsatz von ML-Inferenz ermöglicht.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.