Implementierung von Low-Power, High-Performance Edge-Computing unter Verwendung von Efinix' quantenfähigen FPGAs

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-03-17

Klassisches Cloud-Computing hat Probleme mit Latenzzeiten, Datensicherheit, Datenschutz für Endbenutzer, verfügbarer Bandbreite und zuverlässiger Konnektivität. Um diese Probleme anzugehen, gehen Designer und Systemarchitekten in Richtung Edge-Computing. Allerdings stellt das Edge-Computing eine Reihe eigener Herausforderungen dar, die von Kosten, Größe, Leistung und Energieverbrauch bis hin zu Fragen der Skalierbarkeit, Flexibilität und Aufrüstbarkeit reichen. Dies ist insbesondere dann der Fall, wenn Designer mehr Bildverarbeitung betreiben und mehr Algorithmen der künstlichen Intelligenz (KI) und des maschinellen Lernens (ML) näher an der Datenquelle implementieren wollen.

Folglich schauen die Designer über die traditionellen Mikrocontroller (MCUs) oder Anwendungsprozessoren (APs) hinaus und ziehen feldprogrammierbare Gate-Arrays (FPGAs) mit ihren Parallelverarbeitungsmöglichkeiten in Betracht. Dank kontinuierlicher Verbesserungen beim Design und der Implementierung von FPGAs können diese nun viele oder alle diese Anforderungen erfüllen - entweder als eigenständige Geräte oder in Verbindung mit MCUs und APs. Dennoch sind viele Designer mit FPGAs nicht vertraut und sind besorgt über die Lernkurve.

In diesem Artikel wird kurz die Migration von Cloud- zu Edge-Computing diskutiert und warum traditionelle Verarbeitungsarchitekturen bei der Bildverarbeitung sowie bei AI und ML versagen. Anschließend wird ein kurzer Blick auf FPGAs geworfen und erläutert, warum sie einen architektonischen Vorteil für diese datenintensiven Randanwendungen haben. Schließlich wird ein neuer Ansatz für FPGAs - die Quantum-Technologie von Finix - und ihre Anwendung vorgestellt.

Warum Edge-Computing?

Beim traditionellen Cloud-Computing werden Daten von unzähligen entfernten Standorten gesammelt und zur Speicherung und Analyse in ein Cloud-basiertes System eingespeist. Dieser Ansatz hat jedoch viele Nachteile. Dazu gehören die Kosten für die Übertragung großer Mengen von Rohdaten, die Aufrechterhaltung der Integrität und Sicherheit dieser Daten während der Übertragung, Antwortlatenzzeiten, Datenschutzbedenken der Endbenutzer und oft unzuverlässige Verbindungen zum Internet und eine suboptimale Nutzung der verfügbaren Bandbreite.

Wie der Name schon sagt, bedeutet Edge-Computing, die Verarbeitung - Berechnung und Analyse - näher an den Rand des Internets zu verlagern, genau dorthin, wo die Daten erzeugt, analysiert, gesammelt und angewendet werden. Der Begriff Edge-Computing ist nicht anwendungs- oder gerätespezifisch, und Designer können je nach Bedarf eine reine Edge-Verarbeitung oder ein Gleichgewicht zwischen Cloud und Edge wählen.

Zu den Randanwendungen gehören intelligente Fabriken, intelligente Städte, intelligente Häuser und intelligente Verkehrsmittel, um nur einige zu nennen. Außerdem können Edge-Geräte von großen High-End-Edge-Servern bis hin zu relativ kleinen Sensor- und Aktuatorsystemen reichen, die sich am äußersten Rand des Internets befinden - am Punkt der Datenerzeugung.

Der Vorteil von FPGAs

Wenn es um die Berechnung geht, sind traditionelle Prozessoren äußerst effizient, wenn es um die Entscheidungsfindung und sequentielle Aufgaben geht, aber schrecklich ineffizient im Hinblick auf viele Datenverarbeitungsalgorithmen, wie z.B. die für die Bildverarbeitung, KI und ML verwendeten. Diese Aufgaben können oft in massiv parallele (im Gegensatz zu sequentiellen) Verarbeitungspipelines unterteilt werden. Zufällig sind es genau diese Anwendungen, die an den Rand und ins Extreme abwandern.

Die Tatsache, dass FPGAs so programmiert (konfiguriert) werden können, dass sie jede beliebige Kombination von Funktionen implementieren können, ermöglicht es ihnen, Bildverarbeitungs-, AI- und ML-Algorithmen massiv parallel auszuführen, wodurch die Latenzzeit minimiert und gleichzeitig der Stromverbrauch gesenkt wird. Zusätzlich zu ihrer programmierbaren Hauptstruktur sind FPGAs mit On-Chip-Blöcken für die digitale Signalverarbeitung (DSP) ausgestattet, die spezielle Multiplikatoren enthalten, die DSP-intensive Anwendungen drastisch beschleunigen. FPGAs verfügen auch über On-Chip-Speicherblöcke, die die On-Chip-Verarbeitung erleichtern, die viel schneller ist als die Off-Chip-Verarbeitung.

Es gibt eine Reihe von FPGA-Anbietern, jeder mit seinem eigenen einzigartigen Angebot. Ein solcher Anbieter, Efinix, hat eine spezielle FPGA-Architektur namens Quantum entwickelt, die sich in einzigartiger Weise für Edge-Computing im Allgemeinen und Bildverarbeitung im Besonderen eignet. Um diese Technologie herum hat sie ihre Serie von Trion-FPGAs (und Quanten-ASICs) entwickelt, um einen 4-fachen Vorteil im Leistungsbereich gegenüber herkömmlichen FPGA-Technologien zu erzielen (Abbildung 1). Die integrierte Entwicklungsumgebung (IDE) von Efinity bildet die Brücke zwischen den Bereichen FPGA und ASIC.

Abbildung 1: Mit ihrem Vorteil im Leistungsbereich adressieren Trion-FPGAs Anwendungen wie kundenspezifische Logik, Rechenbeschleunigung, ML, tiefes Lernen und Bildverarbeitung. Mit der Efinity IDE können Anwender nahtlos von einem Trion-FPGA auf einen Quantum-ASIC für die Ultrahochvolumenproduktion migrieren. (Bildquelle: Efinix)

Abbildung 1: Mit ihrem Vorteil im Leistungsbereich adressieren Trion-FPGAs Anwendungen wie kundenspezifische Logik, Rechenbeschleunigung, ML, tiefes Lernen und Bildverarbeitung. Mit der Efinity IDE können Anwender nahtlos von einem Trion-FPGA auf einen Quantum-ASIC für die Ultrahochvolumenproduktion migrieren. (Bildquelle: Efinix)

Was ist Quantentechnologie?

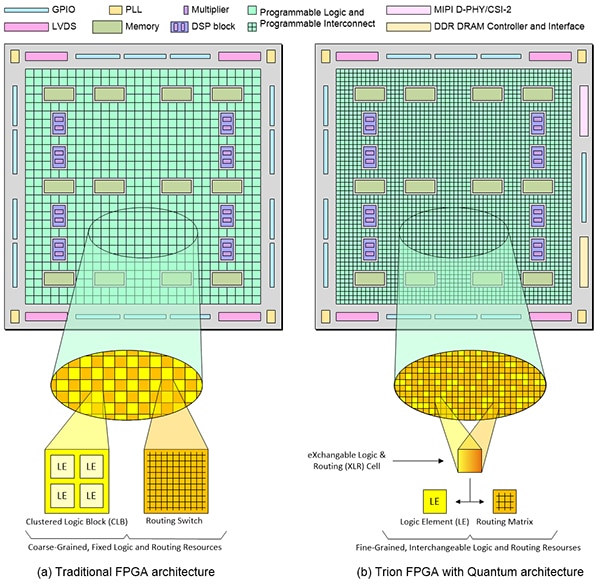

Wie traditionelle FPGAs enthalten Trion-FPGAs Speicher- und DSP-Blöcke. Der Unterschied liegt in der programmierbaren Struktur (Abbildung 2). Das Herzstück der programmierbaren Logik ist das Logikelement (LE). Jede LE enthält eine Nachschlagetabelle (LUT), einen Multiplexer und ein Register, die alle nach Bedarf konfiguriert werden können. Im Falle traditioneller FPGAs kann ihr programmierbares Fabric als "grobkörnig" bezeichnet werden.

Abbildung 2: Eine traditionelle FPGA-Architektur (a) ist grobkörnig, und obwohl die Logik und die Verbindung programmierbar sind, handelt es sich dabei immer noch um feste Ressourcen. Im Vergleich dazu sind Trion-FPGAs (b), die auf der Quantenarchitektur basieren, feinkörnig und ihre Logik- und Routing-Ressourcen austauschbar (Bildquelle: Max Maxfield)

Abbildung 2: Eine traditionelle FPGA-Architektur (a) ist grobkörnig, und obwohl die Logik und die Verbindung programmierbar sind, handelt es sich dabei immer noch um feste Ressourcen. Im Vergleich dazu sind Trion-FPGAs (b), die auf der Quantenarchitektur basieren, feinkörnig und ihre Logik- und Routing-Ressourcen austauschbar (Bildquelle: Max Maxfield)

Bei grobkörnigen Geweben werden mehrere LEs zu einem größeren Clustered Logic Block (CLB) zusammengefasst. Beachten Sie, dass einige Anbieter den Begriff "konfigurierbarer Logikblock" (CLB) verwenden, während andere den Begriff "Logic Array Block" (LAB) verwenden, die aber alle dasselbe bedeuten.

Es ist wichtig zu beachten, dass diese Illustration eine Abstraktion ist. Die CLBs und Routing-Schalter (programmierbare Verbindungen) in traditionellen FPGAs sind nicht wirklich in einem Schachbrettmuster dargestellt, wie hier gezeigt. Sie sind jedoch insofern fest und unveränderlich, als programmierbare Logik immer programmierbare Logik sein wird, und programmierbare Verbindungen werden immer programmierbare Verbindungen sein.

Im Vergleich zu traditionellen Architekturen sind Trion-FPGAs viel feiner körnig, bis hin zur Auflösung eines einzelnen Logikelements. Darüber hinaus kann jede austauschbare Logik- und Routing (XLR)-Zelle so konfiguriert werden, dass sie als LE oder als Teil der Routing-Matrix fungiert.

Die in der Quantum-Architektur verwendeten Konfigurationszellen basieren auf SRAM, was bedeutet, dass diese Technologie "silizium-agnostisch" ist. Sie können mit jedem Standard-CMOS-Prozess hergestellt werden, ohne dass spezielle Verarbeitungsschritte erforderlich sind, wie sie bei alternativen Konfigurationstechnologien wie Flash und Antifuse, die in einigen FPGAs der mittleren Preisklasse verwendet werden, erforderlich sind.

Es ist diese softwarekonfigurierbare Logik und das Routing und die hochleistungsfähige adaptive Verbindung, die dem Quantum-basierten Ansatz eine 4-fache Verbesserung in Bezug auf den Leistungsbereich (PPA) im Vergleich zu traditionellen SRAM-basierten FPGAs, die am gleichen Prozesstechnologie-Knotenpunkt erstellt wurden, verleiht.

Außerdem benötigen FPGAs, die mit der Quantum-Architektur erstellt wurden, nur sieben Metallisierungsschichten, im Gegensatz zu den 12+, die von traditionellen FPGAs verlangt werden. Da jede zusätzliche Metallschicht mehrere Masken- und Prozessschritte erfordert, reduziert die Verwendung von nur sieben Schichten die Design- und Herstellungskosten und erhöht die Ausbeute.

All diese Eigenschaften und Merkmale sind sehr nützlich für Designer, die nach Kosten-, Größen-, Leistungs- und Flexibilitätsvorteilen bei der Kantenverarbeitung und Bildverarbeitung suchen. Als solche eignen sich Trion-FPGAs sowohl für traditionelle FPGA-Anwendungen als auch für neu aufkommende Edge-Computing und Bildverarbeitungsanwendungen. Zu letzteren gehören Mobilgeräte, Internet der Dinge (IoT), Automatisierung, Robotik, Sensorfusion, Computer Vision, KI und ML.

Die Struktur der Trion-FPGAs

Trion-FPGAs werden in einem 40 Nanometer (nm) langen Low-Power-Siliziumprozess mit zwischen viertausend (K) und 200K LEs hergestellt, wobei der Prozess auf viel größere Bauelemente skalierbar ist. Alle Trion-FPGAs enthalten Speicher- und DSP-Blöcke, aber ihre Kapazität und Anzahl variieren je nach Größe des Bausteins. Kleinere Geräte wie der T4F81C2 sind in ihren Merkmalen minimalistischer (d.h. 3.888 LEs, 78.848 Speicherbits, 59 GPIOs) und zielen auf die Funktionen der Steuerungsebene ab.

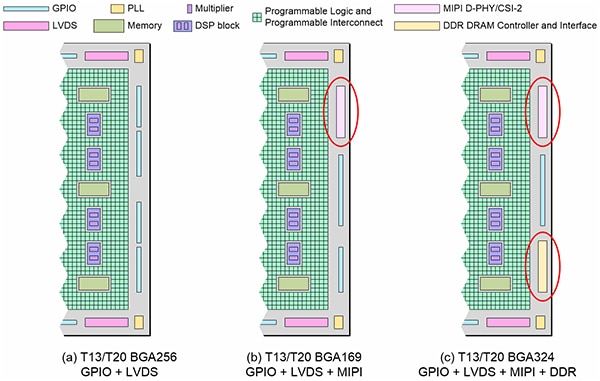

Höhere Endgeräte wie der T20F256C3 enthalten entsprechend mehr Ressourcen (d.h. 19.728 LEs, 1.069.548 Speicherbits, 195 GPIOs). Der T13F256C3 ist dem T20F256C3 ähnlich, hat aber 12.828 LEs. Außerdem gibt es Geräte wie den T13/T20 in verschiedenen Versionen (Abbildung 3).

Abbildung 3: Die Efinix T13/T20 BGA256s (a) sind ein generischer FPGA, der eine gute Wahl für Designs mit I/O-intensiven Anforderungen ist; die T13/T20 BGA169s (b) enthalten zwei MIPI D-PHY/CSI-2 Hardcore-Blöcke für Designs, die die MIPI-Kameraschnittstelle unterstützen müssen; und die T13/T20 BGA324s (c) erweitern die MIPI-Schnittstellen um eine Hardcore-DDRAM-Schnittstelle mit x16-Bit doppelter Datenrate (DDR) und Controller für Designs mit speicherbandbreitenintensiven Anforderungen. (Bildquelle: Max Maxfield)

Abbildung 3: Die Efinix T13/T20 BGA256s (a) sind ein generischer FPGA, der eine gute Wahl für Designs mit I/O-intensiven Anforderungen ist; die T13/T20 BGA169s (b) enthalten zwei MIPI D-PHY/CSI-2 Hardcore-Blöcke für Designs, die die MIPI-Kameraschnittstelle unterstützen müssen; und die T13/T20 BGA324s (c) erweitern die MIPI-Schnittstellen um eine Hardcore-DDRAM-Schnittstelle mit x16-Bit doppelter Datenrate (DDR) und Controller für Designs mit speicherbandbreitenintensiven Anforderungen. (Bildquelle: Max Maxfield)

MIPI CSI-2 ist die am häufigsten verwendete Kameraschnittstelle in mobilen und anderen Märkten aufgrund des geringen Stromverbrauchs, der geringen Latenzzeit und der kostengünstigen Chip-zu-Chip-Konnektivität. Außerdem unterstützt es eine breite Palette von Hochleistungsformaten, einschließlich 1080p, 4K, 8K (und höher) Video sowie hochauflösende Bilder. Von besonderem Interesse ist dabei die Tatsache, dass MIPI CSI-2 die vorherrschende Schnittstelle für Vision-Sensoren in Kantenanwendungen ist. Zur Unterstützung von Designs für diese Anwendungen enthalten die T13/T20 BGA169s-FPGAs zwei MIPI D-PHY/CSI-2-Hartkern-Blöcke (Abbildung 3).

DDR-Speicher unterstützt Datenübertragungen mit hoher Bandbreite, erfordert aber auch die Einhaltung eines strengen Zeitprotokolls. Zusätzlich zu den gehärteten MIPI D-PHY/CSI-2-Schnittstellen enthalten die Trion T13/T20 BGA324s (Abbildung 3) auch eine gehärtete x16-Bit-DDR-DRAM-Schnittstelle und einen Controller für Designs mit hohem Bedarf an Speicherbandbreite.

Quanten-ASICs

Wie bereits erwähnt, sind die in Trion-FPGAs verwendeten Konfigurationszellen SRAM-basiert. Folglich müssen die Konfigurationsdaten von Trion-FPGAs beim ersten Einschalten des Systems geladen werden, entweder von einem externen Speichergerät oder durch "Bit-Banging" über den Host-Prozessor. Um dies in ultrahohen Stückzahlen zu erreichen, bietet Efinix auch quantenbeschleunigte eingebettete FPGA (eFPGA) Lösungen in Form von Quanten-ASICs an. In diesem Fall kann Efinix T4-, T8-, T13- oder T20-Designs nehmen und maskenprogrammierte Quantum-ASIC-Versionen erstellen, die intern booten, ohne dass ein externes Konfigurationsgerät erforderlich ist.

Design und Entwicklung mit Trion-FPGAs

Efinix bietet eine Vielzahl von Evaluierungsboards und Entwicklungskits an, die es Benutzern ermöglichen, sich mit Trion-FPGAs vertraut zu machen. Dazu gehören das Trion T8F81C-DK T8 Trion FPGA-Entwicklungskit, das Trion T20F256C-DK T20 Trion FPGA-Evaluierungsboard und das Trion T20MIPI-DK T20 MIPI D-PHY/CSI-2 Entwicklungskit.

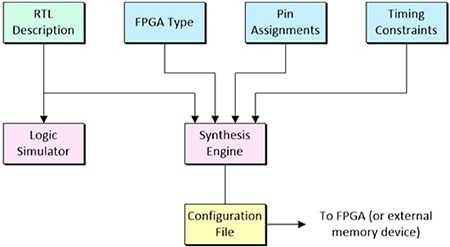

Eine der häufigsten Techniken, die bei der Entwicklung mit FPGAs eingesetzt werden, ist das sogenannte sprachgesteuerte Design (LDD). Dazu gehört die Erfassung der Entwurfsabsicht auf einer Abstraktionsebene, der so genannten Register-Transfer-Ebene (RTL), unter Verwendung einer Hardware-Beschreibungssprache (HDL) wie Verilog oder VHDL. Nach der Verifizierung durch Logiksimulation wird diese Darstellung dann zusammen mit zusätzlichen Informationen wie dem Ziel-FPGA-Typ, Pin-Zuweisungen und Zeitbeschränkungen, wie z.B. maximale Verzögerungen von Eingang zu Ausgang, in eine Synthese-Engine eingespeist. Die Ausgabe der Synthese-Engine ist eine Konfigurationsdatei, die direkt in den FPGA oder in einen externen Speicherbaustein geladen wird (Abbildung 4).

Abbildung 4: Nach der Verifikation mittels Logiksimulation wird die RTL-Designbeschreibung zusammen mit zusätzlichen Designdetails wie dem FPGA-Typ, den Pin-Zuweisungen und den Timing-Bedingungen in eine Synthese-Engine eingespeist. Die Ausgabe der Synthese-Engine ist eine Konfigurationsdatei, die in den FPGA geladen wird. (Bildquelle: Max Maxfield)

Abbildung 4: Nach der Verifikation mittels Logiksimulation wird die RTL-Designbeschreibung zusammen mit zusätzlichen Designdetails wie dem FPGA-Typ, den Pin-Zuweisungen und den Timing-Bedingungen in eine Synthese-Engine eingespeist. Die Ausgabe der Synthese-Engine ist eine Konfigurationsdatei, die in den FPGA geladen wird. (Bildquelle: Max Maxfield)

Die Efinity IDE von Efinix fällt in diese Klasse von Werkzeugen. Diese Software bietet einen vollständigen RTL-zu-Bitstream-Fluss mit einer einfachen, leicht zu bedienenden grafischen Benutzeroberfläche (GUI) und Befehlszeilen-Scripting-Unterstützung. Ein intuitives Dashboard führt den Entwickler durch den Ablauf (d.h. Synthese, Platzierung, Routing, Bitstromerzeugung), wobei jede Stufe automatisch oder manuell gesteuert werden kann. Entwickler können die Synthese-Engine von Efinity nutzen, um die in Trion-FPGAs enthaltene Quantum-Architektur voll auszunutzen und Bausteine mit den versprochenen 4-fachen PPA-Verbesserungen zu generieren.

Neben der Unterstützung von Simulationsabläufen mit den Simulatoren ModelSim, NCSim oder dem freien IVerilog bietet die Efinity IDE auch einen Interface-Designer zur Beschränkung der Logik und zur Zuweisung von Pins an Blöcke in der Geräteperipherie, einen Floorplan-Editor zum Durchsuchen der Logik und der Routing-Platzierung eines Designs, einen Timing-Browser und eine statische Timing-Analyse zur Messung der Leistung eines Designs sowie einen integrierten Hardware-Debugger mit Logikanalysator und virtuellen E/A-Debug-Kernen.

Fazit

Wenn Designer mehr Bild-, KI- und ML-Verarbeitung am Rand statt oder zur Ergänzung eines Cloud-basierten Ansatzes durchführen, müssen sie FPGAs als Teil ihrer Verarbeitungsarchitektur betrachten, um Probleme wie Kosten, Leistung, Stromverbrauch, Größe, Skalierbarkeit, Flexibilität und Erweiterbarkeit besser zu lösen.

Für einige Designer mag dies eine Lernkurve bedeuten; wie jedoch gezeigt wurde, können Fortschritte bei FPGAs wie die Quantum-Technologie von Efinix die Investition durch niedrigere Kosten, kleinere Formfaktoren, höhere Leistung und größere Flexibilität schnell lohnenswert machen.

Daher eignen sich FPGAs heute sowohl für traditionelle FPGA-Anwendungen als auch für neu aufkommende Edge-Computing-Anwendungen in den Bereichen Mobile, IoT, Automatisierung, Robotik, Sensor-Fusion, Computer Vision, AI und ML.

Zusätzliche Ressourcen

- Grundlagen: Das IoT, IIoT, AIoT und warum sie die Zukunft der industriellen Automatisierung sind

- Grundlagen von FPGAs: Was sind FPGAs und warum werden sie benötigt?

- Grundlagen von FPGAs - Teil 2: Erste Schritte mit FPGAs von Lattice Semiconductor

- Grundlagen von FPGAs - Teil 3: Erste Schritte mit den FPGAs von Microchip Technology

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.