Einsatz von FPGA-SoCs für sichere und vernetzte Echtzeitsysteme

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2023-02-16

FPGAs (Field Programmable Gate Arrays), Linux-fähige RISC-V-Subsysteme für Mikrocontroller-Einheiten (MCUs), fortschrittliche Speicherarchitekturen und leistungsstarke Kommunikationsschnittstellen sind wichtige Werkzeuge für Entwickler. Dies gilt insbesondere für Entwickler von sicheren vernetzten Systemen, sicherheitskritischen Systemen und einer breiten Palette von deterministischen Systemen in harter Echtzeit wie künstliche Intelligenz (KI) und maschinelles Lernen (ML).

Die Integration dieser verschiedenen Elemente in ein sicheres, vernetztes und deterministisches System kann jedoch eine anspruchsvolle und zeitaufwändige Aufgabe sein, ebenso wie die Auslegung der Highspeed-Verbindungen für die verschiedenen Systemelemente. Die Entwickler müssen eine Speicherverwaltungseinheit, eine Speicherschutzeinheit, eine sichere Boot-Funktion und Transceiver der Gigabit-Klasse für Hochgeschwindigkeitsverbindungen vorsehen. Das Design erfordert ein aktives und statisches Leistungsmanagement und eine Steuerung der Einschaltströme. Einige Designs erfordern den Betrieb im erweiterten kommerziellen Temperaturbereich von 0°C bis +100°C Sperrschichttemperatur (TJ), während Systeme in industriellen Umgebungen mit einer TJ von -40°C bis +100°C arbeiten müssen.

Um diese und andere Herausforderungen zu meistern, können Entwickler auf FPGA-System-on-Chip(SoC)-Bausteine zurückgreifen, die einen niedrigen Stromverbrauch, thermische Effizienz und Sicherheit in Verteidigungsqualität für intelligente, vernetzte und deterministische Systeme bieten.

Dieser Artikel beschreibt die Architektur eines solchen FPGA-SoCs und wie es den effizienten Entwurf von vernetzten und deterministischen Systemen unterstützt. Anschließend wird kurz der Benchmark EEMBC CoreMark-Pro zur Gegenüberstellung von Verarbeitungsleistung und Stromverbrauch vorgestellt, zusammen mit einem Überblick über die Benchmark-Leistung eines repräsentativen FPGA-SoC. Es wird untersucht, wie Sicherheit in diese FPGA-SoCs integriert ist, und es werden beispielhafte FPGA-SoCs von Microchip Technology sowie eine Entwicklungsplattform zur Beschleunigung des Designprozesses vorgestellt. Es schließt mit einer kurzen Auflistung von Erweiterungsboards von MikroElektronika, mit denen eine Reihe von Kommunikationsschnittstellen sowie GNSS-Ortungsfunktionen (Global Navigation Satellite System) implementiert werden können.

SoCs, die mit einer FPGA-Struktur aufgebaut sind

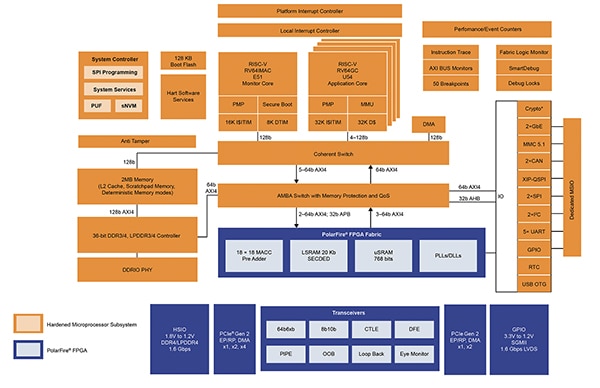

Der „Chip“ für diesen SoC ist eine FPGA-Struktur, die die Systemelemente enthält, vom FPGA bis zum RISC-V-MCU-Subsystem, das mit gehärteter FPGA-Logik aufgebaut ist. Das MCU-Subsystem umfasst einen Quad-Core-RISC-V-MCU-Cluster, einen RISC-V-Monitor-Kern, einen Systemcontroller und ein deterministisches Level-2-Speicher-Subsystem (L2). Das FPGA in diesen SoCs enthält bis zu 460K Logikelemente, Transceiver für bis zu 12,7 Gigabit pro Sekunde (Gbit/s) und andere Input/Output(I/O)-Blöcke, einschließlich allgemeine I/O (GPIO) und PCIe 2 (Peripheral Component Interconnect Express). Die gesamte Architektur ist auf Zuverlässigkeit ausgelegt. Sie umfasst eine Einzelfehlerkorrektur und Doppelfehlererkennung (SECDED) für alle Speicher, eine differenzielle Leistungsanalyse (DPA), einen physischen Speicherschutz und einen 128 Kilobit großen Flash-Boot-Speicher (Abbildung 1).

Abbildung 1: Alle Elemente in diesem FPGA-SoC, einschließlich der RISC-V-Subsysteme, sind auf der FPGA-Struktur implementiert. (Bildquelle: Mikrochip-Technologie)

Abbildung 1: Alle Elemente in diesem FPGA-SoC, einschließlich der RISC-V-Subsysteme, sind auf der FPGA-Struktur implementiert. (Bildquelle: Mikrochip-Technologie)

Microchip bietet mit Mi-V (ausgesprochen „My five“) ein Ökosystem von Tools und Design-Ressourcen von Drittanbietern zur Unterstützung der Implementierung von RISC-V-Systemen. Es wurde entwickelt, um die Einführung der RISC-V-Befehlssatzarchitektur (ISA) für gehärtete RISC-V-Kerne und für RISC-V-Soft-Cores zu beschleunigen. Elemente des Mi-V-Ökosystems umfassen den Zugang zu:

- Lizenzen für geistiges Eigentum (IP)

- Hardware

- Betriebssysteme und Middleware

- Debugger, Compiler und Entwicklungsdienste

Die gehärteten RISC-V-MCUs im FPGA-SoC verfügen über verschiedene Debugging-Funktionen wie die zur Laufzeit passiv konfigurierbare erweiterbare Schnittstelle (AXI) und die Befehlsverfolgung. AXI ermöglicht es Entwicklern, Daten zu überwachen, die in verschiedene Speicher geschrieben oder aus ihnen gelesen werden, und zu wissen, wann sie geschrieben oder gelesen werden.

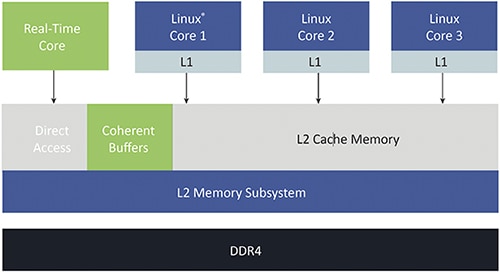

Das RISC-V-MCU-Subsystem verwendet eine fünfstufige Single-Issue-In-Order-Pipeline. Sie ist nicht anfällig für Spectre- oder Meltdown-Exploits, die Out-of-Order-Architekturen befallen können. Alle fünf MCUs sind mit dem Speichersubsystem kohärent und unterstützen eine Mischung aus deterministischen Echtzeitsystemen im asymmetrischen Multiprocessing-Modus (AMP) und Linux. Das RISC-V-Subsystem verfügt über folgende Funktionen (Abbildung 2):

- Ausführen von Linux und harten Echtzeitoperationen

- Konfigurieren von L1 und L2 als deterministischen Speicher

- DDR4-Speicher-Subsystem

- Verzweigungsvorhersagen deaktivieren/aktivieren

- Betrieb der In-Order-Pipeline

Abbildung 2: Das RISC-V-Subsystem umfasst mehrere Prozessor- und Speicherelemente. (Bildquelle: Microchip Technology)

Abbildung 2: Das RISC-V-Subsystem umfasst mehrere Prozessor- und Speicherelemente. (Bildquelle: Microchip Technology)

Mehr Verarbeitung mit weniger Energie

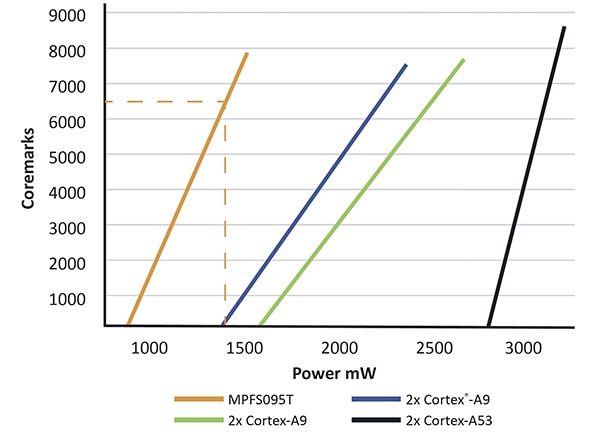

Zusätzlich zu ihren Vorteilen im Systembetrieb, einschließlich der Unterstützung für harte Echtzeitverarbeitung, sind diese FPGA-SoCs äußerst energieeffizient. Der Benchmark EEMBC CoreMark-PRO ist ein Industriestandard für den Vergleich der Effizienz und Leistung von MCUs in eingebetteten Systemen. Er wurde speziell für den Leistungsvergleich von Hardware entwickelt und soll den Dhrystone-Benchmark ersetzen.

Die CoreMark-PRO-Arbeitslasten umfassen eine Vielzahl von Leistungsmerkmalen, Parallelität auf Befehlsebene und Speichernutzung auf der Grundlage von vier Gleitkomma-Arbeitslasten und fünf gängigen Integer-Arbeitslasten. Zu den Gleitkomma-Arbeitslasten gehören eine von LINPACK abgeleitete lineare Algebra-Routine, eine schnelle Fourier-Transformation, ein neuronaler Netzalgorithmus zur Musterauswertung und eine verbesserte Version des Livermore-Loops-Benchmarks. JPEG-Komprimierung, ein XML-Parser, ZIP-Komprimierung und ein sicherer 256-Bit-Hash-Algorithmus (SHA-256) bilden die Grundlage für die Integer-Arbeitslasten.

Die MPFSO95T-Modelle dieser SoC-FPGAs, wie der MPFS095TL-FCSG536E, können bis zu 6500 Coremarks bei 1,3 Watt liefern (Abbildung 3).

Abbildung 3: Der FPGA-SoC MPFS095T (orangefarbene Linie) liefert 6500 Coremarks bei 1,3 Watt. (Bildquelle: Microchip Technology)

Abbildung 3: Der FPGA-SoC MPFS095T (orangefarbene Linie) liefert 6500 Coremarks bei 1,3 Watt. (Bildquelle: Microchip Technology)

Überlegungen zur Sicherheit

Die sicherheitskritischen und harten Echtzeitanwendungen für diese FPGA-SoCs erfordern neben einer hohen Energieeffizienz und leistungsstarken Verarbeitungsfunktionen auch eine hohe Sicherheit. Zu den grundlegenden Sicherheitsfunktionen dieser FPGA-SoCs gehören eine gegen die differenzielle Leistungsanalyse (DPA) resistente Bitstream-Programmierung, ein echter Zufallszahlengenerator (TRNG) und eine physikalisch nicht klonierbare Funktion (PUF). Dazu gehören auch ein standardmäßiges und benutzerdefiniertes sicheres Booten, physischer Speicherschutz, der Speicherzugriffsbeschränkungen in Bezug auf den Privilegstatus des Rechners bietet, einschließlich Rechner-, Supervisor- oder Benutzermodus, und Immunität gegen Meltdown- und Spectre-Angriffe.

Sicherheit beginnt mit einem sicheren Management der Lieferkette, einschließlich der Verwendung von Hardware-Sicherheitsmodulen (HSM) bei der Prüfung und Verpackung von Wafern. Die Verwendung eines 768 Byte großen, digital signierten x.509-FPGA-Zertifikats, das in jedes FPGA-SoC eingebettet ist, erhöht die Sicherheit der Lieferkette.

Diese FPGA-SoCs sind mit zahlreichen On-Chip-Manipulationsdetektoren ausgestattet, um einen sicheren und zuverlässigen Betrieb zu gewährleisten. Wenn eine Manipulation festgestellt wird, wird ein Manipulationsflag ausgegeben, das es dem System ermöglicht, entsprechend zu reagieren. Einige der verfügbaren Manipulationsdetektoren sind:

- Spannungswächter

- Temperatursensoren

- Taktstörungs- und Taktfrequenzdetektoren

- JTAG-Aktiv-Detektor

- Mesh-Aktiv-Detektor

Die Sicherheit wird außerdem durch AES-256 (256-Bit Advanced Encryption Standard), symmetrische Blockchiffre-CPA-Gegenmaßnahmen (Correlation Power Attack), integrierte kryptografische Digest-Funktionen zur Gewährleistung der Datenintegrität, integrierte PUF für die Schlüsselspeicherung und Zeroization-Funktionen für die FPGA-Struktur und alle On-Chip-Speicher gewährleistet.

FPGA-SoC-Beispiele

Microchip Technology kombiniert diese Fähigkeiten und Technologien in seinen PolarFire-FPGA-SoCs mit verschiedenen Geschwindigkeitsstufen, Temperaturklassen und unterschiedlichen Gehäusegrößen, um die Anforderungen von Entwicklern für ein breites Spektrum von Lösungen mit 25K bis 460K Logikelementen zu erfüllen. Es sind vier Temperaturklassen erhältlich (alle für TJ ausgelegt): 0°C bis +100°C im erweiterten kommerziellen Bereich, -40°C bis +100°C im industriellen Bereich, -40°C bis +125°C im Automobilbereich und -55°C bis +125°C im militärischen Bereich.

Entwickler haben die Wahl zwischen Komponenten mit Standardgeschwindigkeit und Komponenten mit der Geschwindigkeitsklasse -1, die 15 % schneller sind. Diese FPGA-SoCs können bei 1,0 Volt für den stromsparenden Betrieb oder bei 1,05 Volt für höhere Leistung betrieben werden. Sie sind in einer Reihe von Gehäusegrößen erhältlich, darunter 11 x 11 Millimeter (mm), 16 x 16 mm und 19 x 19 mm.

Für Anwendungen, die einen erweiterten kommerziellen Temperaturbetrieb, einen Standard-Geschwindigkeitsbetrieb und 254K-Logikelemente in einem 19 x 19 mm-Gehäuse benötigen, kann der MPFS250T-FCVG484EES verwendet werden. Für einfachere Lösungen, die 23K-Logikelemente benötigen, kann der MPFS025T-FCVG484E verwendet werden, der ebenfalls über einen erweiterten kommerziellen Temperaturbetrieb und eine Standard-Geschwindigkeitsklasse in einem 19 x 19 mm großen Gehäuse verfügt. Der MPFS250T-1FCSG536T2 mit 254K Logikelementen wurde für Hochleistungssysteme im Automobilbereich entwickelt und verfügt über einen Betriebstemperaturbereich von -40 bis 125°C und eine Geschwindigkeitsklasse von -1 für einen 15 % schnelleren Takt in einem kompakten 16 x 16 mm-Gehäuse mit 536 Kugeln im 0,5mm-Raster (Abbildung 4).

Abbildung 4: Der MPFS250T-1FCSG536T2 für Automobiltemperaturen wird in einem 16 x 16 mm großen Gehäuse mit einer Kugelanzahl von 536 und einem Raster von 0,5 mm geliefert. (Bildquelle: Microchip Technology)

Abbildung 4: Der MPFS250T-1FCSG536T2 für Automobiltemperaturen wird in einem 16 x 16 mm großen Gehäuse mit einer Kugelanzahl von 536 und einem Raster von 0,5 mm geliefert. (Bildquelle: Microchip Technology)

FPGA-SoC-Entwicklungsplattform

Um das Design von Systemen mit dem PolarFire-FPGA-SoC zu beschleunigen, bietet Microchip das PolarFire-SoC-Icicle-Kit MPFS-ICICLE-KIT-ES an, das die Erforschung des fünfkernigen Linux-fähigen RISC-V-Mikroprozessor-Subsystems mit stromsparender Echtzeitausführung ermöglicht. Das Kit enthält eine kostenlose Libero Silver Lizenz, die für die Evaluierung von Designs benötigt wird. Sie unterstützt Programmier- und Debugging-Funktionen in einer einzigen Sprache.

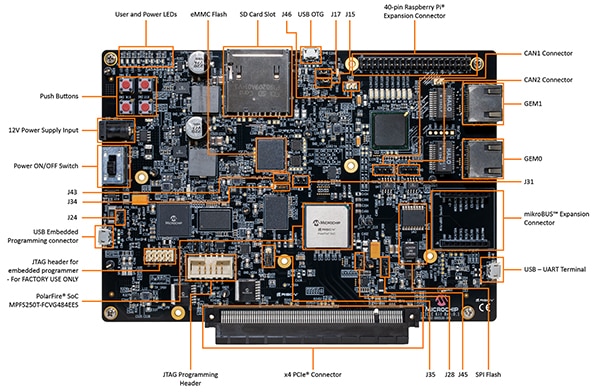

Diese FPGA-SoCs werden durch das VectorBlox-Beschleuniger-SDK (Software Development Kit) unterstützt, das stromsparende AI/ML-Anwendungen mit kleinem Formfaktor ermöglicht. Der Schwerpunkt liegt auf der Vereinfachung des Entwurfsprozesses, so dass die Entwickler keine Erfahrung im FPGA-Design haben müssen. Das VectorBlox-Beschleuniger-SDK ermöglicht es Entwicklern, energieeffiziente neuronale Netze mit C/C++ zu programmieren. Das Icicle-Kit verfügt über zahlreiche Funktionen, um eine umfassende Entwicklungsumgebung bereitzustellen, darunter ein Multi-Rail-Energiesensorsystem zur Überwachung der verschiedenen Stromversorgungsbereiche, ein PCIe-Root-Port und On-Board-Speicher - einschließlich LPDDR4, QSPI und eMMC Flash - zur Ausführung von Linux und Raspberry Pi sowie mikroBUS-Erweiterungsports für eine Vielzahl von kabelgebundenen und drahtlosen Verbindungsoptionen sowie funktionale Erweiterungen wie GNSS-Ortungsfunktionen (Abbildung 5).

Abbildung 5: Diese umfassende FPGA-SoC-Entwicklungsumgebung enthält Anschlüsse für Raspberry-Pi- (oben rechts) und mikroBUS-Erweiterungskarten (unten rechts). (Bildquelle: Mikrochip-Technologie)

Abbildung 5: Diese umfassende FPGA-SoC-Entwicklungsumgebung enthält Anschlüsse für Raspberry-Pi- (oben rechts) und mikroBUS-Erweiterungskarten (unten rechts). (Bildquelle: Mikrochip-Technologie)

Erweiterungsboards

Einige Beispiele für mikroBUS-Erweiterungskarten sind:

MIKROE-986, zum Hinzufügen von CAN-Bus-Vernetzung über eine serielle Peripherieschnittstelle (SPI).

MIKROE-1582, für eine Schnittstelle zwischen der MCU und einem RS-232-Bus.

MIKROE-989, zum Anschluss an einen RS422/485-Kommunikationsbus.

MIKROE-3144, zur Unterstützung der Technologien LTE Cat M1 und NB1 und für eine zuverlässige und einfache Verbindung mit 3GPP-IoT-Geräten.

MIKROE-2670, ermöglicht GNSS-Funktionalität mit gleichzeitigem Empfang von GPS- und Galileo-Konstellationen plus entweder BeiDou oder GLONASS, was zu einer hohen Positionsgenauigkeit in Situationen mit schwachen Signalen oder Störungen in Straßenschluchten führt.

Fazit

Entwickler können auf FPGA-SoCs zurückgreifen, wenn sie vernetzte, sicherheitskritische und harte deterministische Echtzeitsysteme entwickeln. FPGA-SoCs bieten eine breite Palette von Systemelementen, darunter eine FPGA-Struktur, ein RISC-V-MCU-Subsystem mit Hochleistungsspeichern, Highspeed-Kommunikationsschnittstellen und zahlreiche Sicherheitsfunktionen. Um Entwicklern den Einstieg zu erleichtern, sind Entwicklungsboards und -umgebungen erhältlich, die alle erforderlichen Elemente enthalten, einschließlich Erweiterungsplatinen, mit denen sich eine Vielzahl von Kommunikations- und Ortungsfunktionen implementieren lassen.

Empfohlene Lektüre

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.