Wie die RISC-V-Atomic-Erweiterung überragende Bitmanipulationsfähigkeiten bietet

Die Verbreitung der RISC-V-Architektur nimmt rasant zu, und aus gutem Grund wächst ihr Einfluss in der Branche.

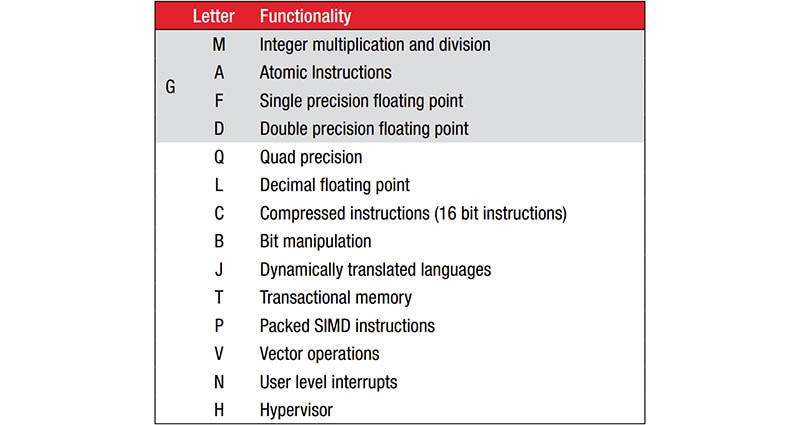

Neben der Kernarchitektur und ihrer echten reduzierten Befehlssatzarchitektur (instruction set architecture, ISA) wird sie durch eine Reihe von standardisierten Erweiterungen ergänzt (Abbildung 1). So würde beispielsweise ein 32-Bit-RISC-V-Kern (RV32), der Gleitkomma-Befehle einfacher Genauigkeit und auch komprimierte Befehle unterstützt, gemäß der gezeigten Erweiterungsliste als RV32FC bezeichnet.

Abbildung 1: Die RISC-V-ISA wird durch eine Reihe von standardisierten Befehlserweiterungen ergänzt, die durch einen Buchstaben hinter dem Kernnamen gekennzeichnet sind. (Bildquelle: RISC-V.org)

Abbildung 1: Die RISC-V-ISA wird durch eine Reihe von standardisierten Befehlserweiterungen ergänzt, die durch einen Buchstaben hinter dem Kernnamen gekennzeichnet sind. (Bildquelle: RISC-V.org)

Für viele Anwendungen der künstlichen Intelligenz (AI) und des maschinellen Lernens (ML) sowie für hochentwickelte eingebettete Systeme sind die vier notwendigsten Erweiterungen die Ganzzahlmultiplikation und -division (M), atomare Befehle (A), Gleitkomma-Befehle einfacher Genauigkeit (F) und Gleitkomma-Befehle doppelter Genauigkeit (D). Anstatt einen Kern als RV32MAFD zu bezeichnen, werden diese jedoch alle unter dem Suffix G zusammengefasst, wie bei RV32G.

Weitere Informationen zu den verschiedenen Erweiterungen und zu RISC-V im Allgemeinen finden Sie im RISC-V-E-Book von DigiKey auf der EDU-Website.

Da ich meine ersten Erfahrungen mit Prozessoren in tief eingebetteten Systemen gemacht habe, neige ich dazu, mir die Unterstützung der Bitmanipulation zum Lesen, Ändern und Schreiben im Datenspeicher einer Architektur genau anzusehen. Bei diesen Anwendungen ist das Setzen und Löschen von Bits für periphere Register und Semaphoren sehr üblich. Ohne systemeigene Bitmanipulationsbefehle müsste ein Kern den Inhalt der Datenspeicherplätze in ein Kern-Register kopieren, das bzw. die Bit(s) mit OR-, AND- oder XOR-Befehlen setzen, löschen oder umschalten und dann das Ergebnis zurück in den Datenspeicherplatz speichern. Das kostet nicht nur zusätzliche Zeit, sondern in einigen Fällen habe ich bei einigen eingebetteten Steueranwendungen eine Aufblähung des Codes um bis zu 20 % festgestellt.

Für einige Anwendungen können die Aufblähung des Codes und die Leistungseinbußen akzeptabel sein. Während diese drei Befehle abgearbeitet werden, kann jedoch eine Unterbrechung die Programmsteuerung aus dem Vorgang herausreißen, oder noch schlimmer, in einem Mehrprozessorsystem könnte ein anderer Kern aus demselben Speicherplatz lesen. Die Deaktivierung von Interrupts oder das Sperren von Speicher, um sicherzustellen, dass diese Ereignisse den Datenspeicher nicht beschädigen, erfordert zusätzliche Befehle und Komplikationen, die zu Leistungsproblemen führen können.

Arm hat versucht, diese Probleme durch die Implementierung von Bit-Banding zu lösen, was bei einfachen Bit-Operationen funktioniert. Meiner Meinung nach hat RISC-V jedoch eine elegantere und flexiblere Lösung implementiert.

Warum die Atomic-Erweiterung so elegant ist

Die RISC-V-A-(Atomic)-Erweiterung unterstützt zwei Operationen, einen Load-Reserved/Store-Conditional-Befehl, auf den hier nicht näher eingegangen werden soll, und einen binären/bitweisen Befehl, der eine einfache Bitmanipulation im Datenspeicher ermöglicht. Während die B-Bitmanipulationserweiterung von RISC-V eine Reihe komplexer Bitsteuerbefehle unterstützt, ist die Atomic-Erweiterung nicht nur für Mehrprozessorsysteme gedacht. Sie hilft auch bei kleineren eingebetteten Systemen, bei denen der Bedarf an Bitmanipulationen geringer ist. Ein Beispiel für ein solches System ist das 64-Bit-Dual-Core-RISC-V-Modul 114991684 von Seeed Technology. Es besitzt zwei RV64GC-Kerne, die zusammenarbeiten und mit ihrem gemeinsamen Daten-SRAM gut zusammenspielen müssen.

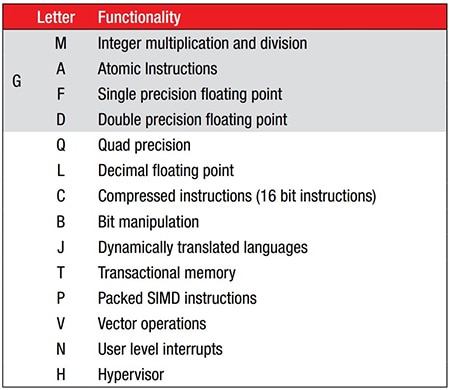

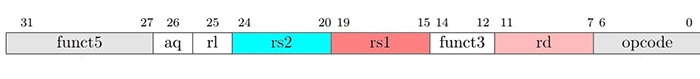

Das Format der atomaren Speicheroperation (atomic memory operation, AMO) der A-Erweiterung von RISC-V ist in Abbildung 2 dargestellt.

Abbildung 2: Das AMO-Befehlsformat von RISC-V unterstützt atomare Binäroperationen auf Datenspeicher mit nur einem Befehl. (Bildquelle: RISC-V.org (erweitert von Bill Giovino))

Abbildung 2: Das AMO-Befehlsformat von RISC-V unterstützt atomare Binäroperationen auf Datenspeicher mit nur einem Befehl. (Bildquelle: RISC-V.org (erweitert von Bill Giovino))

AMO ist ein leistungsfähiger Lese-, Änderungs- und Schreibbefehl, der mit nur einem Befehl verschiedene Binäroperationen direkt auf dem in rs1 angegebenen Datenspeicher unterstützt. Wie in Abbildung 2 dargestellt, wird der Inhalt der Datenspeicheradresse in rs1 geladen und der Wert im Register rd gespeichert. Dann wird eine Binäroperation mit dem Wert von rd und dem Wert in rs2 durchgeführt und das Ergebnis wieder in rd und an der Datenspeicheradresse in rs1 gespeichert.

Unterstützt werden die bitweisen Operationen OR (Bit setzen), AND (Bit löschen) und XOR (Bit umschalten). Das ermöglicht eine atomare Bitmanipulation von einem oder mehreren Bits direkt im Datenspeicher. Außerdem werden Speicherkonflikte verhindert, wenn die beiden RV64GC-Kerne gleichzeitig dieselbe Speicheradresse verwenden. Das ist äußerst nützlich für kleine eingebettete Anwendungen bei der Konfiguration von Peripherieregistern im Speicher sowie zur Vereinfachung von Semaphorenoperationen.

Weitere von der RISC-V AMO unterstützte Operationen sind Integer-Maximum, Integer-Minimum und Austausch. Binäres Addieren wird ebenfalls unterstützt und ermöglicht die direkte binäre Addition, einschließlich der direkten Inkrementierung eines Zählers im Datenspeicher.

Der RV64-Kern unterstützt sowohl 32-Bit- als auch 64-Bit-Operationen. Bei der Bitmanipulation mit dem RV64 ist es wichtig, dass nur 64-Bit-Daten verarbeitet werden, da die Operation 32-Bit-Daten in rd vorzeichenerweitern wird.

Fazit

Die RISC-V-ISA ist der erste ernstzunehmende Konkurrent, der die ISA von Arm herausfordert. Die ISA-Erweiterungen bieten eine standardisierte Methode zur Erweiterung des Kerns um Anweisungen, die die Leistung einer Anwendung kostengünstig verbessern können. Besonders begeistert bin ich von der optionalen Atomic-Erweiterung.

Die Atomic-Erweiterung ist nicht nur nützlich und für Mehrprozessorsysteme fast schon notwendig, sondern auch ein effizienter Weg, die Bitmanipulationen direkt im Datenspeicher zu steuern. Das bietet einen erheblichen Vorteil gegenüber vielen bestehenden Architekturen, da die Codegröße reduziert und die Leistung verbessert wird.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum