Entschlüsselung der RISC-V-Namenskonvention

Die RISC-V-Befehlssatzarchitektur (instruction set architecture, ISA) bietet eine einzigartige Gelegenheit. Ihr Aufbau ermöglicht es Entwicklern, Prozessoren mit einer großen Bandbreite an Größen und Leistungen zu verwenden, die eine beispiellose Softwarekompatibilität bieten. Der Schlüssel zur Nutzung dieser Kompatibilität ist das Verständnis der Namenskonvention für RISC-V-Kerne.

Im Gegensatz zu den meisten Prozessorarchitekturen ist RISC-V quelloffen, d. h. für Entwickler ohne Lizenz- oder Nutzungsgebühren verfügbar. Darüber hinaus ist die ISA so konzipiert, dass sie flexibel ist und es Entwicklern ermöglicht, die Befehlsblöcke auszuwählen, die sie implementieren möchten, und nicht benötigte Befehle wegzulassen und bei Bedarf sogar eigene Befehle hinzuzufügen. Damit soll die Entwicklung mehrerer Prozessorkerne mit unterschiedlichen Größen und Leistungsmerkmalen, aber gemeinsamer Basis gefördert werden.

Diese gemeinsame Basis sorgt für ein hohes Maß an Softwarekompatibilität zwischen den Prozessoren, unabhängig von ihrem Funktionsumfang. Der Code für einen RISC-V-Prozessor mit minimalem Funktionsumfang, der nur den Integer-Befehlssatz implementiert, läuft beispielsweise unverändert auf einem leistungsfähigeren Prozessor, der sowohl Integer- als auch Gleitkommafunktionen besitzt. Code, der die Fließkomma-Befehle verwendet, läuft natürlich nicht auf dem reinen Integer-Prozessor, wird aber auch nicht zum Absturz des Prozessors führen. Nicht implementierte Befehle erzeugt einfach einen Trap für unzulässige Befehle.

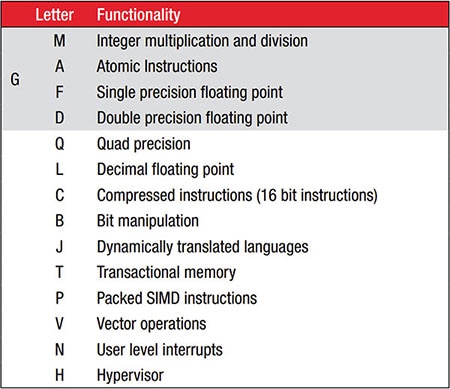

Die RISC-V-ISA erreicht diese Flexibilität durch die Aufteilung ihrer Befehle in im Wesentlichen unabhängige Gruppen mit Maschinencodes, die sich nicht überschneiden. Diese Befehlsgruppen werden als „Standarderweiterungen“ bezeichnet, und die ISA hat zahlreiche solcher Standarderweiterungen definiert, die die meisten der von Entwicklern benötigten Funktionen bieten. Jede Standarderweiterung ist durch einen Buchstabencode gekennzeichnet. Die „M“-Standarderweiterung bietet beispielsweise Anweisungen zum Multiplizieren oder Dividieren von zwei in Registern gespeicherten Ganzzahlen. In ähnlicher Weise bietet die „F“-Standarderweiterung Anweisungen für Gleitkommaoperationen mit einfacher Genauigkeit.

Da die Entwickler von Prozessoren bei der Implementierung eines RISC-V-Kerns Standarderweiterungen mischen und anpassen können, sollte man meinen, dass die Benutzer die technischen Datenblätter und Programmierhandbücher sorgfältig lesen müssen, um festzustellen, was der Prozessor, für den sie nutzen wollen, tatsächlich kann. Aber es gibt eine einfachere Lösung. RISC-V verwendet eine Kernnummerierungskonvention, die dem Benutzer sofort die Fähigkeiten des Kerns anzeigt.

Die Nummerierungskonvention beginnt mit der Basisangabe. Für RISC-V gibt es vier definierte Basisangaben:

- RV32I nutzt einen 32-Bit-Integer-Befehlssatz und bietet 32 Allzweckregister.

- RV32E verwendet einen 32-Bit-Befehlssatz für eingebettete Anwendungen mit 16 Registern.

- RV64I greift auf einen 64-Bit-Integer-Befehlssatz mit 32 Registern zurück.

- RV128I basiert auf einem 128-Bit-Integer-Befehlssatz mit 32 Registern.

Diese Basisangaben definieren einen voll funktionsfähigen, wenn auch einfachen Prozessor. Die meisten Entwickler werden sich jedoch dafür entscheiden, eine oder mehrere Standard-Befehlssatzerweiterungen in ihr Design aufzunehmen. Diese Standarderweiterungen und ihre Kennbuchstaben sind in Abbildung 1 aufgeführt.

Abbildung 1: Die Standard-Befehlssatzerweiterungen für RISC-V-Prozessoren verwenden Buchstabencodes, um ihr Vorhandensein in der Nummerierungskonvention eines Kerns zu kennzeichnen. (Bildquelle: DigiKey)

Abbildung 1: Die Standard-Befehlssatzerweiterungen für RISC-V-Prozessoren verwenden Buchstabencodes, um ihr Vorhandensein in der Nummerierungskonvention eines Kerns zu kennzeichnen. (Bildquelle: DigiKey)

Eine vollständige RISC-V-Kernbezeichnung enthält die Basisangabe, an die die Buchstaben der implementierten Standarderweiterungen angehängt sind, in der in Abbildung 1 aufgeführten Reihenfolge. Ein kleines SoC, das nur minimale Ressourcen benötigt, könnte also die Bezeichnung RV32EMAB tragen. Das bedeutet, dass der Kern den 32-Bit-Integer-Befehlssatz für eingebettete Geräte implementiert, über 16 Register verfügt und Integer-Multiplikation und -Division sowie unteilbare Befehle ausführt. Er verfügt nicht über Fließkommamathematik, unterstützt aber Bitmanipulation.

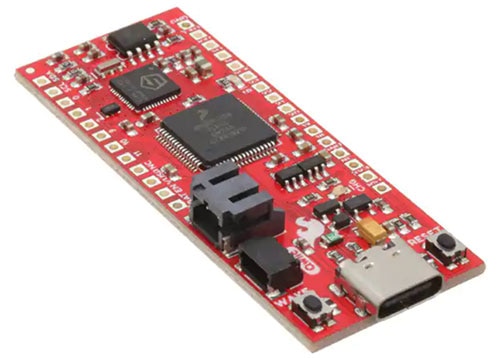

Bei der Auswahl eines RISC-V-Chips für ihren Entwurf müssen Benutzer also nur auf die Kernbezeichnung achten, um zu verstehen, welche Funktionen enthalten sind. Der im Thing Plus RISC-V-Evaluierungsboard DEV-15799 FE310 von SparkFun Electronics enthaltene Prozessor ist beispielsweise als RV32IMAC-Kern aufgeführt (Abbildung 2).

Abbildung 2: Der RISC-V-Prozessor des DEV-15799-Boards trägt die Bezeichnung RV32IMAC, was unter anderem bedeutet, dass er einen 32-Bit-Integer-Befehlssatz und 32 Register sowie unteilbare Befehle bietet. (Bildquelle: SparkFun Electronics)

Abbildung 2: Der RISC-V-Prozessor des DEV-15799-Boards trägt die Bezeichnung RV32IMAC, was unter anderem bedeutet, dass er einen 32-Bit-Integer-Befehlssatz und 32 Register sowie unteilbare Befehle bietet. (Bildquelle: SparkFun Electronics)

Das bedeutet, dass er über einen 32-Bit-Integer-Befehlssatz und 32 Register verfügt, Integer-Multiplikation und -Division implementiert, unteilbare Befehle bietet und komprimierte (16-Bit-)Befehle unterstützt, um den für den Code benötigten Speicherplatz zu minimieren. Jeder Code, der auf diesem Board entwickelt wird, kann auch auf jedem anderen RV32I-Kern mit MAC-Standarderweiterungen (Multiply and Accumulate) ausgeführt werden.

Ein weiteres Beispiel ist das MAXIX-I-RISC-V-SoC-Modul Sipeed 114991684 von Seeed Technology, dessen RISC-V-Kern als RV64IMAFDC aufgeführt ist. Er verfügt über einen 64-Bit-Befehlssatz mit Integer-Multiplikation und -Division, unteilbaren Befehlen, einfach- und doppeltgenauer Gleitkommaberechnung und komprimierten Befehlen. Code, der für diesen Prozessor entwickelt wurde, sollte auf jedem RISC-V-Prozessor mit denselben Kernbezeichnungen laufen, obwohl die Speicherzuordnung von Peripheriegeräten usw. möglicherweise angepasst werden muss.

Fazit

Mit der RISC-V-Namenskonvention sind Benutzer gut gerüstet, um mit dieser leistungsstarken Architektur zu experimentieren. Durch den Abgleich der Kern-Codes können Benutzer sicher sein, dass ihre Programmierarbeit mit einem Prozessor in hohem Maße auf andere RISC-V-Prozessoren übertragbar ist.

Ein guter Ausgangspunkt für diese Experimente ist der Guide to RISC-V, der die anfängliche Einrichtung und Verwendung verschiedener RISC-V-Evaluierungsboards erläutert.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum