Tutorial ADC/DAC

Contributo di DigiKey

2017-09-13

Il mondo di oggi è disseminato di segnali analogici e digitali. Se da un lato questi segnali hanno un comportamento differente, vengono spesso usati entrambi per conseguire un obiettivo più ampio. Immaginiamo un ingegnere che ha il compito di controllare un gruppo HVAC. Se si intende utilizzare un microcontroller o un microprocessore, sarà necessario poter leggere una temperatura analogica (che può essere espressa in molti valori diversi) e convertirla in una rappresentazione binaria disposta in passi discreti. Questa rappresentazione binaria del valore analogico verrà quindi elaborata dal microcontroller o microprocessore. I dati verranno utilizzati per l'esecuzione di un processo da parte del gruppo HVAC al fine di contribuire a mantenere un ambiente stabile. Quando un valore analogico deve essere elaborato da un sistema digitale, è essenziale prevedere un convertitore analogico/digitale (ADC). Lo stesso si applica all'inverso, quando un segnale digitale deve essere convertito in un segnale analogico. Lo streaming di una canzone online comprende alcuni passaggi che utilizzano la conversione di segnali digitali in segnali analogici. Il segnale che il dispositivo host riceve dal server sarà una rappresentazione binaria del segnale analogico originale. La risposta udibile da questi dati binari è inintelligibile per chi ascolta. Dato che il segnale originale era analogico, anche la rappresentazione finale di esso dovrà essere analogica. Questo problema viene risolto utilizzando il convertitore digitale/analogico (DAC). Questo tipo di dispositivo prende un codice binario che potrebbe essere stato codificato da un convertitore analogico/digitale e lo ritrasforma in una tensione analogica.

Convertire segnali da analogico a digitale o da digitale ad analogico è un compito inevitabile per gli ingegneri di oggi. Esistono diversi tipi di convertitore analogico/digitale e digitale/analogico. Se l'architettura può essere diversa, tutti operano per ottenere uno scopo simile. Il segnale digitale non può essere elaborato con valori analogici, è come se una persona che parla francese cercasse di parlare con una persona che parla tedesco. Senza un traduttore non sarebbe possibile. I dispositivi ADC e DAC fungono da traduttore. Quando un dispositivo ADC vede una tensione analogica, il suo compito consiste nel trasformare la tensione analogica in un codice binario in un determinato periodo di tempo. Questo significa che il dispositivo ADC campiona la tensione analogica in un istante, poi determina quale valore è in binario sul lato di uscita del dispositivo ADC. La quantità di campioni presa dal dispositivo ogni secondo viene indicata nella documentazione. Un esempio è rappresentato dal modello MAX1118EKA+T di Maxim Integrated. Questo dispositivo ha una frequenza di campionamento di 100 kHz, è in grado di campionare cioè la tensione analogica sul suo lato di ingresso 100.000 volte al secondo. Data la grande quantità di campioni al secondo, è possibile registrare con precisione la tensione analogica utilizzando una interpretazione binaria. Talvolta la frequenza di campionamento di un dispositivo ADC non è sufficientemente elevata per ricreare in modo preciso il suo ingresso, causando un aliasing. I segnali iniziano a essere non distinguibili l'uno dall'altro o uno un alias dell'altro. Immaginiamo una videocamera in grado di registrare a 24 fotogrammi al secondo. Questo può andar bene per la maggior parte delle applicazioni; se tuttavia si sta tentando di vedere qualcosa che si muove molto velocemente, l'immagine può risultare distorta. Pensiamo all'effetto di guardare alla tivù una registrazione della fine degli anni novanta. L'immagine mostra uno sfarfallio. Questo perché la frequenza di aggiornamento del televisore stesso è molto più veloce di quanto la registrazione possa catturare ai suoi fotogrammi al secondo definiti. L'immagine appare distorta perché il video in realtà è una successione di immagini. Tra ogni immagine avviene molto di più di quanto venga effettivamente rappresentato nel video. Lo stesso tipo di effetto si può avere con un dispositivo ADC. Per evitare ciò è importante assicurarsi che la frequenza di campionamento sia almeno due volte superiore alla frequenza massima da trasmettere. Questa viene detta "frequenza di Nyquist".

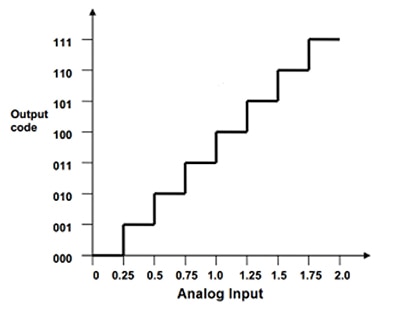

Una frequenza di campionamento maggiore consente al dispositivo di essere più preciso, tuttavia questo non è l'unico modo per controllare la precisione. Dato che si tratta della conversione di un segnale analogico in un codice binario, vi sarà un numero finito di incrementi discreti utilizzabile per rappresentare la tensione in un determinato momento. Il numero di bit che può essere utilizzato per rappresentare questo numero costituisce la risoluzione. Maggiore la risoluzione per il dispositivo ADC, più incrementi discreti esso può avere. Per illustrare più in dettaglio questo concetto è importante capire come determinare il numero di incrementi eseguibili da un dispositivo ADC. Un dispositivo ADC ha una uscita binaria rappresentativa della tensione di alimentazione. Se la tensione di alimentazione è 10 V e abbiamo un dispositivo ADC a 8 bit, allora sono possibili 256 incrementi. Per determinare la risoluzione utilizziamo l'equazione 2n. "2" è costante e N è il numero di bit presenti. Considerando 28 abbiamo 256 incrementi. Con 256 incrementi e una alimentazione di 10 V, ogni incremento sarà di 39,0625 mV. Per ognuno di questi vi sarà un codice binario diverso. Se si esaminano tutte le possibili opzioni di ingresso su un dispositivo ADC partendo da quella più bassa fino a quella più alta, appare il profilo di una scala. La scala è la funzione di trasferimento del dispositivo ADC. La Figura 1 illustra il trasferimento utilizzando un dispositivo ADC a 3 bit con un riferimento di 2 V.

Figura 1: Funzione di trasferimento di un dispositivo ADC a 3 bit con un riferimento di 2 V. (Per gentile concessione di Microchip Technology)

Poiché vi sono tre bit, è possibile calcolare il numero totale di incrementi tramite l'equazione 2n come segue:

![]()

Come si vede nella Figura 1, vi sono otto incrementi tra 000 e 111. Ogni incremento salirà di un bit LSB.

Come indicato in precedenza, vi sono diversi tipi di architetture ADC. Le tre architetture ADC più diffuse sono i registri ad approssimazione successiva (SAR), l'architettura Delta-Sigma (∆∑) e l'architettura a pipeline. Ognuna di esse converte un segnale analogico in una uscita digitale, tuttavia il processo varia leggermente. I SAR campionano un ingresso analogico e lo mantengono, lo trasformano in un segnale digitale e poi lo rilasciano. I convertitori Delta-Sigma eseguono la media del campione nel tempo necessario per convertirlo in un segnale digitale. I convertitori a pipeline dividono la conversione in diversi stadi consentendo velocità di conversione molto rapide. Ognuno di essi presenta aspetti positivi e negativi. L'architettura SAR è di facile impiego, utilizza tipicamente una potenza minore con basso tempo di latenza e alta precisione. L'architettura Sigma-Delta è caratterizzata da risoluzione molto elevata, stabilità elevata, bassa potenza e basso costo; tuttavia opera a velocità molto inferiori rispetto alle architetture SAR e pipeline. Il dispositivo ADC a pipeline opera a velocità più elevate e a una larghezza di banda superiore rispetto agli esempi precedenti, tuttavia ha una risoluzione inferiore e richiede più potenza per funzionare.

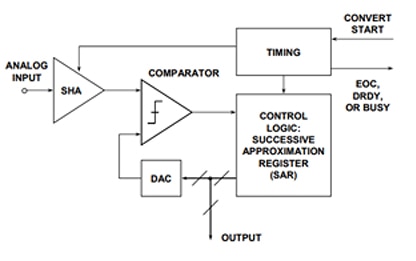

Registri ad approssimazione successiva

I registri ad approssimazione successiva sono i dispositivi ADC più diffusi. Spesso sono dotati di un'interfaccia I2C o SPI, talvolta però è presente una uscita parallela. Per elaborare il segnale analogico i dispositivi ADC SAR hanno un sample-and-hold (S/H) al fine di cercare di mantenere il segnale costante. Un comparatore misura l'ingresso analogico rispetto a un DAC interno. Tale DAC viene impostato a ½ della sua tensione potenziale in quel punto. Se l'ingresso è superiore al DAC, il comparatore emette un 1 da memorizzare nel bit MSB nel "registro ad approssimazione successiva". Dopo di ciò il DAC viene impostato a ¼ della sua tensione potenziale e il processo si ripete. Il valore successivo per il DAC sarà 1/8, poi 1/16 e così via, fino a quando tutti i bit sono stati caricati nel registro. Questo concetto può essere spiegato con un processo simile, cioè l'aggiunta o meno di pesi in successione per vedere quanto pesa qualcos'altro. La Figura 2 sotto illustra questo punto.

Figura 2: Questa analogia illustra come un dispositivo ADC ad approssimazione successiva ottiene un valore digitale da un valore analogico. (Per gentile concessione di Analog Devices)

Il blocco è pari a 45 unità; la prima prova consiste nell'utilizzare 32 blocchi piccoli dove ciascuno è una unità di 1. Il blocco è ancora più pesante dei blocchi più piccoli. Per questo motivo i blocchi più piccoli rimangono. Successivamente si aggiungono altri 16 blocchi piccoli. Abbiamo 32 + 16 uguale a 48; il blocco è troppo pesante. I 16 blocchi quindi vengono scartati. Poi si aggiungono altri 8 blocchi sulla bilancia; dato che 32 + 8 è uguale a 40, questa quantità viene aggiunta. Da qui è possibile aggiungere altri 4 blocchi per un totale di 44 blocchi. Successivamente si aggiungono altri due blocchi, ma questo dà un totale di 46 unità; essendo superiore a 45, i blocchi vengono rimossi. Infine si aggiunge un blocco, in modo che il peso dei blocchi sia pari su entrambi i lati. Ogni volta che sono stati aggiunti dei blocchi, il numero aggiunto è stato diviso per due. Questo è rappresentativo del valore dato dal DAC nel registro SAR. La Figura 3 illustra un diagramma a blocchi di un dispositivo ADC con registro ad approssimazione successiva.

Figura 3: Diagramma a blocchi funzionali di un dispositivo ADC ad approssimazione successiva. (Per gentile concessione di Analog Devices)

Un esempio di un dispositivo ADC SAR è rappresentato dal modello ADS7886SDBVT di Texas Instruments. Si tratta di un dispositivo ADC a 12 bit, quindi può avere 4096 incrementi tra 0 V e la tensione di alimentazione. La frequenza di campionamento è 1 MHz, il che significa che guarda il suo ingresso un milione di volte al secondo. Poiché le prestazioni del dispositivo ADC dovrebbero essere testate prima dell'implementazione in un prodotto finito, spesso i produttori realizzano uno strumento di valutazione che aiuti nel test. Il modello ADS7886SDBVT presenta uno strumento di valutazione di questo tipo, si tratta della scheda ADS7886EVM. Questo facilita molto il test, in quanto vi è già una scheda strutturata con tutti i componenti passivi necessari per testare la funzionalità del dispositivo ADC.

Sigma-Delta ∆∑

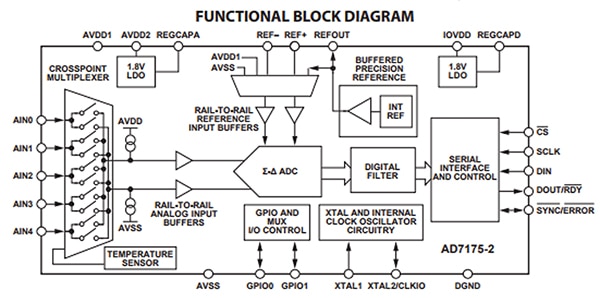

I convertitori Sigma-Delta rappresentano una scelta molto diffusa per tutto quello che richiede risoluzione e precisione elevate. La registrazione audio è un buon esempio di applicazione per un convertitore Sigma-Delta. I convertitori Sigma-Delta devono sovracampionare gli ingressi. La frequenza di Nyquist non è importante nei convertitori Sigma-Delta, in quanto essi operano in modo ottimale quando la frequenza di campionamento è circa 20 volte superiore alla frequenza massima da campionare. L'uscita del convertitore Sigma-Delta viene alimentata in un filtro decimatore digitale che elabora il flusso di bit per realizzare l'uscita finale. Spesso è presente una interfaccia seriale tra il filtro digitale e l'uscita. Un esempio di un ADC Sigma-Delta è rappresentato dal modello AD7175-2BRUZ di Analog Devices, Inc. La Figura 4 illustra il "diagramma a blocchi funzionali" del convertitore AD7175-2BRUZ.

Figura 4: Diagramma a blocchi funzionali del convertitore ADC Sigma-Delta AD7175-2BRUZ di Analog Devices. (Per gentile concessione di Analog Devices)

Il convertitore ADC Sigma-Delta ha una risoluzione a 24 bit e una frequenza di campionamento di 250 kHz. Si ha quindi un potenziale di max. 16.777.216 incrementi. Ciò significa che la risoluzione è molto più alta rispetto all'esempio precedente, ma con circa ¼ della frequenza di campionamento. Come nell'esempio precedente, anche il convertitore AD7175-2BRUZ dispone di una scheda di valutazione per fini di test. La scheda è il modello EVAL-AD7175-2SDZ e consente di valutare con facilità il convertitore ADC.

A pipeline

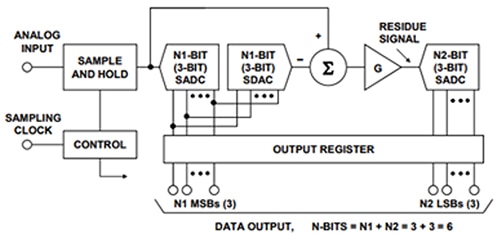

Il convertitore ADC a pipeline è il più veloce. Un esempio tratto da "Architetture ADC V: ADC a pipeline" aiuta a illustrare questo concetto tramite l'utilizzo di un dispositivo ADC a pipeline a 6 bit. Il sample-and-hold (S/H) è uguale al dispositivo SAR, tuttavia subito dopo è presente un sotto-convertitore flash ADC a 3 bit che digitalizza il segnale. La conversione a 3 bit è per i 3 bit più significativi. La riconversione in un segnale analogico avviene tramite un sotto-convertitore DAC. Questa uscita viene sottratta dall'uscita sample-and-hold, amplificata, poi inviata nuovamente al sotto-convertitore ADC a 3 bit di secondo stadio per i tre bit meno significativi rimanenti. La Figura 5 illustra questo punto con un diagramma a blocchi.

Figura 5: Diagramma a blocchi funzionali di un ADC a pipeline. (Per gentile concessione di Analog Devices)

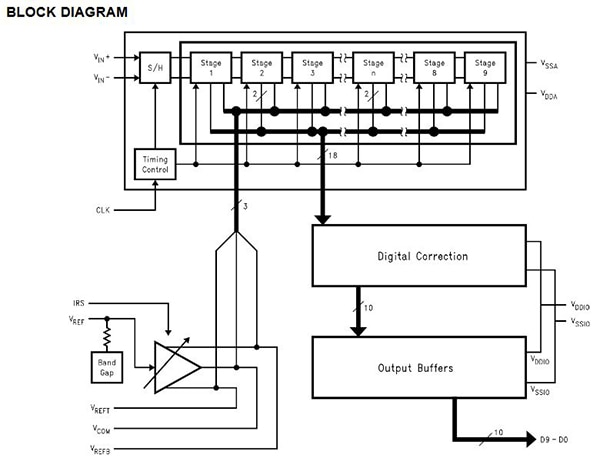

Un esempio di un ADC a pipeline è rappresentato dal modello ADC10080CIMT/NOPB di Texas Instruments. Si tratta di un dispositivo ADC a 10 bit, quindi con un potenziale di 1024 incrementi e in grado di convertire 80 megacampioni al secondo. Le applicazioni per questo dispositivo comprendono ultrasuoni e imaging, strumentazione, sistemi di acquisizione dati o semplicemente tutto ciò che richiede una conversione rapida. Guardando il diagramma a blocchi del dispositivo ADC10080CIMT/NOPB possiamo vedere come esso è configurato secondo quanto descritto sopra. La Figura 6 illustra un diagramma a blocchi tratto dalla scheda tecnica del dispositivo ADC1008CIMT/NOPB.

Figura 6: Diagramma a blocchi funzionali del dispositivo ADC10080CIMT/NOPB di Texas Instruments. (Per gentile concessione di Texas Instruments)

DAC pesato binario

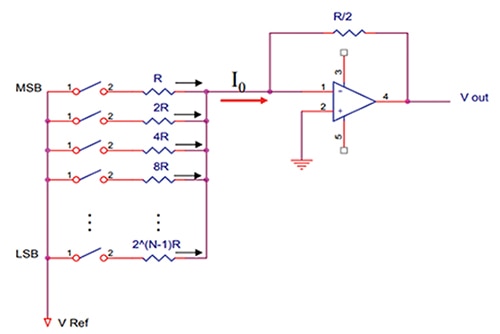

Fino ad ora l'articolo si è concentrato sull'aspetto ADC della conversione dei dati, ma questa è solo metà dell'opera. Spesso infatti è necessario riconvertire i dati binari in un segnale analogico. Ecco dove trova impiego il convertitore digitale/analogico. Di norma il primo tipo di convertitore DAC che si insegna a scuola è il DAC pesato binario. Esso comporta l'utilizzo di un sistema di resistori le cui uscite si incontrano tutte nello stesso resistore sommatorio. I bit più significativi emettono più corrente rispetto ai bit meno significativi. Questo si ottiene creando una rete resistiva inversamente proporzionale. Poiché ogni bit binario del codice digitale ha lo stesso valore di tensione, utilizzando resistori inversamente proporzionali su ogni bit i bit più grandi consentono il passaggio di una corrente maggiore attraverso di essi. Questo particolare metodo di conversione non è più molto diffuso, dati i metodi più semplici in uso oggi; tuttavia rappresenta un buon punto di partenza per descrivere il funzionamento dei convertitori DAC. La difficoltà maggiore che si incontra con questo metodo è trovare resistori di livello diverso che operano insieme. La tolleranza deve essere incredibilmente stringente ed è più facile trovare resistori di valore simile piuttosto che con molti valori diversi come quelli utilizzati dal metodo pesato binario. La Figura 7 illustra questa architettura tramite lo schema di una rete di resistori pesati binari.

Figura 7: Rappresentazione schematica di una rete a registro pesato binario. (Per gentile concessione del Georgia Institute of Technology)

DAC in stringa

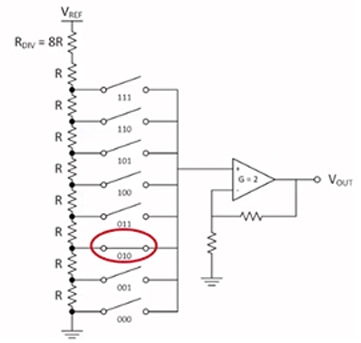

Un'altra architettura diffusa per i dispositivi DAC è il DAC in stringa. Rappresenta l'architettura più semplice ma anche quella meno lineare; talvolta viene anche chiamata divisore Kelvin. Corrisponde a una stringa di resistori di uguale valore in serie. La stringa ha una tensione di riferimento in alto e un resistore ad alta impedenza prima della stringa; inoltre ogni nodo ha un interruttore dedicato a un codice binario che si chiude quando il codice viene letto dal dispositivo. Questo consente di utilizzare un valore di tensione analogica che dipende dall'ingresso binario. La Figura 8 è tratta da un video di Texas Instruments dal titolo "Cos'è un DAC in stringa?". Il codice 010 viene scelto per il valore decimale di 2. L'interruttore su 010 ora è chiuso, consentendo il passaggio della tensione c.c. in quel nodo all'amplificatore sommatorio.

Figura 8: Rappresentazione schematica di un dispositivo DAC in stringa. (Per gentile concessione di Texas Instruments)

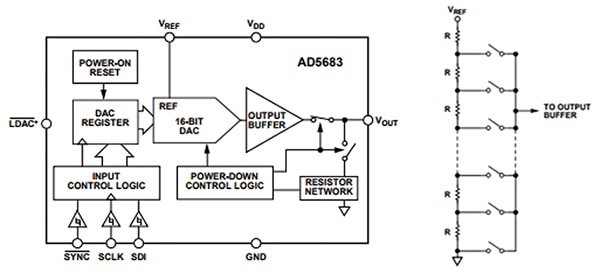

I dispositivi DAC in stringa sono facili da produrre perché utilizzano un resistore di uguale valore per ogni parte della stringa (meno il resistore ad alta impedenza). Un esempio di un dispositivo DAC in stringa è rappresentato dal modello AD5683RBRMZ di Analog Devices Inc. Si tratta di un DAC in stringa a 16 bit che opera con interfaccia SPI. La Figura 9 mostra il diagramma a blocchi funzionali di questo dispositivo, mentre la Figura 10 mostra il divisore resistivo. Anche questo prodotto è dotato di una scheda di valutazione, il modello EVAL-AD5683RSDZ

Figura 9 e 10: Diagramma a blocchi funzionali del dispositivo AD5683RBRMZ di Analog Devices (a sinistra) e della rete di divisori resistivi (a destra). (Per gentile concessione di Analog Devices)

R-2R

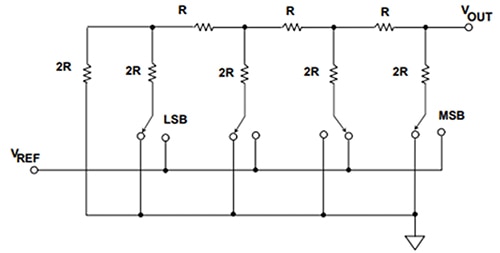

La rete R-2R è una architettura DAC molto diffusa. Utilizza solo due valori resistivi, che non sono importanti purché il valore 2R sia il doppio del valore R. Questo rende i dispositivi DAC R-2R molto scalabili. Indipendentemente dal numero di bit del DAC, sono sempre necessari solo due valori resistivi. La Figura 11 mostra una rete a scala R-2R a 4 bit.

Figura 11: Rappresentazione schematica di un dispositivo DAC R-2R. (Per gentile concessione di Analog Devices)

Questa rete di divisori utilizza il teorema di Thevenin per ottenere la resistenza equivalente di Thevenin per l'intera rete di "R". Ogni stadio consente il doppio di tensione del precedente. In questo esempio, con Vref 5 V lo stadio di sinistra più lontano per il bit LSB sarà in grado di produrre solo 0,3125 V. Spostandosi da sinistra verso destra, l'uscita di tensione proporzionale sarà:

![]()

Questo è rappresentativo di tutti gli ingressi digitali, dove X0 è il bit LSB e X3 è il bit MSB. Utilizzando un riferimento di 5 V, avremo:

![]()

Secondo la stessa logica, per trovare la tensione analogica per il bit più significativo si può considerare quanto segue:

![]()

Con un ingresso binario di 1111, l'uscita non sarà pari a 5 V. Ricordiamo quando discusso in precedenza in merito alla risoluzione. Con un convertitore DAC a 4 bit vi possono essere 16 incrementi. Questo perché 24 consente 16 incrementi. Il bit LSB è a 0,3125 V; moltiplicando 0,3125 x 16 arriviamo a 5. Ciò è ingannevole, in quanto uno degli incrementi comprende una massa di 0 V per rappresentare il binario 0000. La tensione più elevata che può essere ottenuta quindi è la tensione di alimentazione meno una tensione LSB. Abbiamo perciò 4,6875 V.

![]()

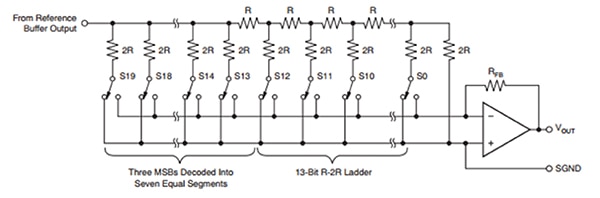

Un esempio di un dispositivo DAC R-2R è rappresentato dal modello DAC8734SPFB di Texas Instruments. Si tratta di un convertitore a 16 bit che mostra la scalabilità di questi dispositivi. Il layout utilizzato per la rete R-2R è molto simile a quanto descritto sopra. La Figura 12 mostra la rete R-2R per il dispositivo DAC8734SPFB. Anche il dispositivo Per DAC8734SPFB presenta una scheda di valutazione, il modello DAC8734EVM.

Figura 12: Rappresentazione schematica del dispositivo DAC R-2R DAC8734SPFB di Texas Instruments. (Per gentile concessione di Texas Instruments)

Esistono diversi altri tipi di architetture ADC/DAC, tuttavia questo articolo illustra solo alcune tra le più diffuse. Questi dispositivi sono necessari nel mondo dell'elaborazione dei segnali digitali di oggi. Senza i dispositivi ADC/DAC non sarebbe possibile integrare una uscita analogica in nessun tipo di elaborazione di segnali digitali o viceversa. Per un profano è facile darlo per scontato, ma per un ingegnere che ha il compito di collegare componenti analogici fino a un sistema digitale si tratta di uno dei passaggi più importanti da considerare. Quando pensiamo alla conversione da analogico a digitale, ricordiamo l'analogia con due persone che parlano lingue diverse. Senza un traduttore, non sarebbero in grado di comunicare una con l'altra. Se non si utilizzano dispositivi ADC/DAC in modo appropriato, un dispositivo sarebbe costretto a utilizzare segnali strettamente analogici o digitali. I dispositivi ADC/DAC rappresentano una grande stretta di mano tra due mondi.

Risorse

- "AVR127: Capire i parametri ADC". Maggio 2016.

- "Scegliere il convertitore A/D giusto per la propria applicazione". Reperito 8 maggio 2017.

- Kester, Walt. "Architetture ADC II: ADC ad approssimazione successiva". Ottobre 2008.

- Kester, Walt. "Architetture ADC III: Principi base degli ADC Sigma-Delta". Ottobre 2008.

- Kester, Walt. "Architetture ADC IV: Concetti e applicazioni avanzate degli ADC Sigma-Delta". Ottobre 2008.

- Kester, Walt. "Architetture ADC V: ADC a pipeline" Ottobre 2008.

- Kester, Walt. "Nozioni fondamentali sull'interfaccia DAC". Ottobre 2008.

- Kester, Walt. "Architetture DAC base II: DAC binari". Ottobre 2008.

- Lee, J., Jeelani K., Beckwith, J. "Convertitore digitale/analogico". Reperito 8 maggio 2017

- Poole, Matt. "Cos'è un DAC in stringa?". 4 aprile 2016

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.