Scelta e utilizzo della tecnologia più appropriata per la memoria flash in applicazioni che richiedono una memoria di programma IoT

Contributo di Editori nordamericani di DigiKey

2018-05-23

Appurato che i nodi IoT diventano sempre più potenti, i requisiti di elaborazione possono raggiungere un livello tale da richiede un sistema operativo completo come Linux per gestire correttamente la complessità di tutte le attività in esecuzione. Benché sia pratico memorizzare il codice su una scheda microSDHC flash, la maggior parte delle schede flash microSDHC sono progettate solo per l'archiviazione dei dati e non per l'archiviazione del sistema operativo, sebbene i fornitori abbiano escogitato alcune soluzioni innovative.

Questo articolo descrive il ruolo di un sistema operativo embedded e perché è spesso consigliabile memorizzare sia il sistema operativo che il codice dell'applicazione su una scheda flash microSDHC in un nodo IoT. Quindi spiega la modalità di deterioramento delle schede flash e come i sistemi operativi possono essere particolarmente colpiti da questo fenomeno di deterioramento. Infine mostra come i progettisti possono utilizzare nuove implementazioni di memorie flash per superare il deterioramento per implementazioni di nodi IoT efficienti e affidabili.

Perché usare un sistema operativo embedded

Per alcune applicazioni IoT, maggiore è la pre-elaborazione che può essere eseguita sul nodo IoT remoto, minori sono i dati che questo deve restituire all'hub centrale, liberando larghezza di banda sulla rete. Un sistema operativo embedded pre-testato può supportare la pre-elaborazione complessa gestendo molte singole attività in modo efficiente e può effettuare il multitasking in modo prevedibile (deterministico). Ovviamente, ciò richiederà ulteriori requisiti per il microcontroller, ovvero una maggiore velocità di clock e, cosa ancora più importante, più memoria di programma.

Un SO embedded open-source commerciale o di serie può anche avere il vantaggio di un codice solido e pre-testato che raramente richiede aggiornamenti. Ad esempio, i sistemi operativi Linux embedded disponibili possono essere aggiornati anche solo trimestralmente o solo per le patch di sicurezza di emergenza. Un sistema operativo e il codice dell'applicazione embedded necessari possono richiedere 8 Gbyte o più e, poiché il sistema operativo viene raramente aggiornato, può essere più conveniente memorizzarlo su una scheda di memoria flash microSDHC che viene manualmente (fisicamente) aggiornata da un tecnico. Questa soluzione inoltre agevola una futura espansione di memoria, in quanto una scheda flash da 4 Gbyte esistente può essere facilmente sostituita con una scheda da 8 Gbyte o più, se necessario, alla successiva visita di un tecnico (Figura 1).

Figura 1: Una scheda di memoria microSDHC Classe 10 S-140u di Swissbit che supporta velocità fino a 104 Mbps, abbastanza veloce per l'accesso alla memoria del programma ad alta velocità. (Immagine per gentile concessione di Swissbit)

La memorizzazione dei gigabyte di un sistema operativo embedded su una scheda flash NAND microSDHC aggiornabile fisicamente presenta numerosi vantaggi rispetto alla memoria flash aggiornata su una rete wireless. In una rete wireless, in base allo schema di arbitraggio utilizzato, l'aggiornamento di un sistema operativo da 4 Gbyte o più potrebbe rubare la larghezza di banda wireless alle comunicazioni operative. L'aggiornamento su una rete richiede anche una scheda microSDHC di dimensioni doppie rispetto al normale, in quanto ha bisogno di spazio sufficiente sia per eseguire il sistema operativo che per accogliere l'aggiornamento in arrivo.

L'aggiornamento wireless del codice riduce anche la durata della batteria a causa dell'attività radio, delle tensioni di scrittura e dei requisiti di alimentazione più elevati.

Un sistema operativo embedded eseguito in memoria flash pone alle celle di memoria richieste diverse rispetto all'archiviazione dei dati. La maggior parte delle schede flash microSDHC commerciali sono progettate dal produttore solo per la memorizzazione dei dati. L'uso commerciale più comune è l'archiviazione multimediale per dispositivi mobili. Mentre errori di bit, anche numerosi, in un video, un'immagine o un file audio possono passare inosservati all'utente finale, un singolo errore in un file SO embedded critico può causare un errore totale del sistema.

La memoria flash non ha una durata illimitata. Ogni operazione di scrittura su una matrice della memoria flash diminuisce la durata della matrice stessa. Le specifiche di tutte le memorie flash a semiconduttori indicano un numero limitato di cicli di cancellazione/scrittura. Quando la cella si avvicina al limite specificato, la sua usura diventa sempre più probabile e non accetta un nuovo stato di programmazione.

Un approccio comune per prevenire il deterioramento della matrice a causa delle operazioni di scrittura è chiamato livellamento dell'usura. Invece di scrivere nella stessa posizione della memoria, le scritture vengono distribuite uniformemente sull'intero array, garantendo uniformità di scritture sull'intera matrice della memoria flash. Con il livellamento dell'usura, mentre il microcontroller scrive su una singola posizione nella memoria fisica, il controller della memoria può mappare la stessa posizione in diverse posizioni nell'array.

Come si verificano gli errori di disturbo di lettura

L'accesso ai file del sistema operativo è molto più frequente rispetto a quello ai file di dati, quindi tali errori possono rivelarsi spiacevoli se relativi ai bit dei file. In alcuni casi, i file del sistema operativo principale potrebbero essere letti costantemente e questo può introdurre errori di bit nell'array della memoria.

La memoria flash è disposta in blocchi e ogni blocco contiene un numero di pagine. I blocchi sono le parti più piccole della memoria che possono essere cancellate, mentre le pagine sono le parti più piccole della memoria che possono essere lette o programmate. Una dimensione comune per un blocco è 256 kB, che può contenere 64 pagine di 4 kB ciascuna. Ogni pagina include inoltre 64 byte aggiuntivi utilizzati per il codice di correzione degli errori (ECC), i conteggi delle cancellazioni e le informazioni di conversione da logica a fisica.

Durante un'operazione di lettura di una pagina di dati, viene applicata una piccola tensione all'intero blocco a cui appartiene la pagina, anche se la lettura riguarda un solo byte nella pagina. A causa della tecnologia delle celle delle memorie flash, ciò induce anche una piccola tensione nelle pagine del blocco circostanti. Questo evento può iniettare elettroni negli strati isolanti delle celle, come avviene per la programmazione della cella, motivo per cui viene indicato come "programmazione soft". L'applicazione ripetuta di quella piccola tensione di lettura allo stesso blocco può alla fine disturbare e impedire la lettura delle programmazioni delle pagine. Nel tempo, ciò può comportare la modifica dello stato delle celle adiacenti su un valore diverso.

Mentre la maggior parte delle schede flash NAND microSDHC ha una qualche forma di correzione degli errori per correggere gli errori delle celle, il numero di errori causati dalla "programmazione soft" può essere così numeroso da raggiungere un livello critico che non può essere corretto, con la conseguenza che il microcontroller legge un valore diverso dalla posizione del bit, causando un errore di file deteriorato. Questi errori di bit sono indicati come errori di disturbo di lettura.

Una scheda flash NAND microSDHC utilizzata per l'archiviazione dei dati raramente rileva errori di disturbo di lettura. A causa delle operazioni di scrittura eseguite sull'array, dopo un'operazione di livellamento dell'usura, le posizioni vengono riprogrammate, eliminando eventuali effetti di "programmazione soft". Tuttavia, un array utilizzato per un sistema operativo embedded viene programmato così raramente che un errore di disturbo di lettura può diventare realtà.

Le schede flash SLC (a cella singola) sono classificate per un milione di letture e le schede flash MLC (multicella) sono classificate per 100.000 letture prima che si verifichino errori di disturbo di lettura. Per le memorie flash di dati, un errore di disturbo di lettura è considerato così raro che questi valori spesso non sono riportati nelle specifiche.

Utilizzare l'RDM per prevenire errori di disturbo di lettura

Per prevenire errori di disturbo di lettura, Swissbit ha sviluppato una funzionalità chiamata Read Disturb Management (RDM). Nell'RDM di Swissbit, il controller della scheda flash tiene traccia del numero di operazioni di lettura per ogni singolo blocco. Quando un blocco raggiunge un numero definito internamente, il controller sposta i dati in un nuovo blocco, in modo simile al livellamento dell'usura utilizzato per le operazioni di scrittura. Se necessario, durante l'operazione di scrittura su un nuovo blocco, il codice di correzione degli errori del controller SD (ECC) corregge tutti i dati danneggiati.

L'RDM è stato implementato nella scheda flash microSDHC SFSD8192N1BM1MT-I-QG-221-STD 8 Gbyte S-450u UHS-I Classe 10 di di Swissbit. Progettata specificamente per applicazioni industriali che utilizzano sistemi operativi embedded, l'S-450u ha spazio sufficiente per un sistema operativo Linux e un codice applicativo per molti nodi IoT complessi. In modalità SDR104, l'S-104u può supportare fino a 104 Mbps di accesso ai dati.

Utilizzo di una scheda microSDHC per l'esecuzione del programma in memoria

Come spiegato in precedenza, le schede microSDHC vengono solitamente utilizzate solo come memoria dati, quindi le periferiche sulla maggior parte dei microcontroller con architettura Harvard supportano l'accesso alle schede microSDHC solo in questo ruolo. Questo limita le opzioni disponibili.

Le soluzioni esistenti leggono la scheda microSDHC e caricano il programma nella RAM, quindi lo eseguono da quest'ultima. Il chip RAM non solo aggiunge costi supplementari alla scheda, ma l'espansione del programma è limitata alla quantità di RAM disponibile sulla scheda.

Le schede MicroSDHC sono in grado di interfacciarsi in modalità SD o SPI.

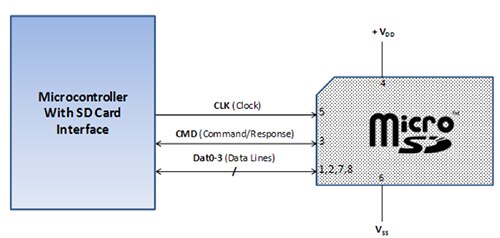

Per interfacciare il microcontroller alla scheda microSDHC S-450u come memoria di programma, il microcontroller selezionato dovrà supportare uno dei due protocolli di bus microSDHC:

- Un controller in modalità SD su scheda SDHC mappato alla memoria del programma (Figura 2). Può essere una periferica esterna o un microcontroller interno. L'interfaccia è composta da sei segnali: quattro bit di dati (DAT[0-3]), un segnale di clock (CLK) e uno di comando/risposta bidirezionale (CMD). I dati vengono trasferiti quattro bit alla volta e garantiscono la massima velocità di esecuzione del programma. Il controller host o il microcontroller fornisce il clock alla scheda microSDHC.

- Un'interfaccia SPI configurabile con supporto XIP (eXecute In Place). Questa soluzione può eseguire il codice dalla scheda accedendo alla scheda microSDHC in modalità SPI, fornendo un trasferimento veloce dei dati, ma non quanto una modalità scheda SDHC. La memoria XIP mappa la memoria della scheda nello spazio di memoria del programma del microcontroller, rendendo l'accesso alla scheda microSDHC trasparente al firmware dell'host.

Figura 2: L'interfaccia con una scheda microSDHC utilizzando la modalità SD adotta una semplice interfaccia a sei segnali per fornire l'accesso più veloce possibile alla memoria. (Immagine per gentile concessione di DigiKey)

Una scheda microSDHC si attiva in modalità scheda SD. Per selezionare la modalità SPI a singolo bit, sui primi sei clock dopo l'avvio, il segnale DAT3 deve essere portato a VDD, mentre allo stesso tempo viene inviato un comando RESET (000000b) alla scheda abbassando il CMD a VSS. Effettuata questa operazione, la scheda rimane in modalità SPI fino a quando non viene disattivata.

Il microcontroller MAX32652 Arm® Cortex®-M4F di Maxim Integrated è un dispositivo a basso consumo progettato per nodi IoT. È dotato di un'interfaccia XIP QSPI su chip che, se correttamente configurata, è in grado di eseguire il codice da una scheda microSDHC.

Il microcontroller MAX32652 dispone anche di un'interfaccia SDHC completa, principalmente usata per lo storage di dati in memoria.

È importante notare che queste interfacce verso il microcontroller devono essere interfacce di memoria del programma. Indipendentemente dal protocollo bus o dall'interfaccia utilizzata, il microcontroller dovrebbe contenere un codice di boot flash su chip per inizializzare l'interfaccia sulla scheda microSDHC.

Sicurezza a livello di zoccolo

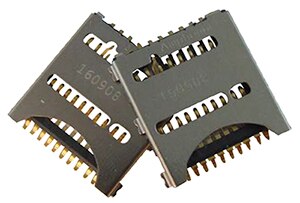

Lo zoccolo per una scheda microSDHC per applicazioni industriali viene spesso trascurato. Per applicazioni gravose, con il tempo lo stagno o materiali di contatto simili possono veder scadere o perdere la loro resistenza alla trazione. I contatti dorati, pur costando un po' di più, valgono il costo fornendo una solida connessione di contatto che mantiene la sua resistenza alla trazione nel tempo.

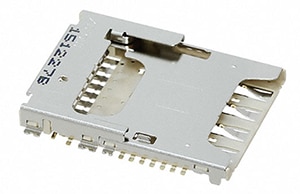

Il connettore/lo zoccolo per microSDHC e per Universal Flash Storage (UFS) 10101704J6#2A di Amphenol ICC garantisce una connessione affidabile e robusta per qualsiasi scheda compatibile microSDHC (Figura 3). Questo zoccolo è dotato di contatti anti-strappo che impediscono l'aderenza delle schede di memoria durante l'inserimento e l'estrazione.

Figura 3: Il connettore/lo zoccolo per scheda UFS e microSDHC 10101704J6#2A supporta sia le microSDHC attuali che le schede UFS di nuova generazione con velocità di trasferimento dati fino a 6 Gbps. (Immagine per gentile concessione di Amphenol)

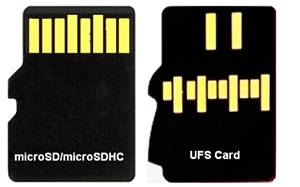

Questo zoccolo Amphenol supporta anche evoluzioni future grazie alla compatibilità con il nuovo formato Universal Flash Storage (UFS) che ha un fattore di forma simile alla microSDHC, ma con un footprint di contatto diverso (Figura 4). La scheda UFS supporta il doppio della velocità della microSDHC con trasferimento dati bidirezionale differenziale.

Figura 4: Una scheda microSDHC a sinistra e la nuova scheda UFS a destra. La scheda UFS supporta il doppio della velocità della microSDHC con trasferimento dati bidirezionale differenziale. (Immagine per gentile concessione di DigiKey)

Alcuni nodi IoT collegati in rete potrebbero trovarsi in località remote in cui il Wi-Fi non è disponibile o non è pratico. Per queste situazioni, la rete può essere implementata tramite una connessione dati cellulare wireless. Ciò richiede l'utilizzo di una scheda SIM dell'abbonato, che deve essere anch'essa montata in uno zoccolo.

Un modo semplice per risparmiare spazio su scheda consiste nell'utilizzare uno zoccolo combinato per scheda microSDHC e per scheda SIM come il 1041681620 di Molex (Figura 5). Questo zoccolo è dotato di contatti dorati e anti-strappo per una connessione sicura in ambienti difficili.

Figura 5: Lo zoccolo combinato 1041681620 per scheda SIM e microSDHC riduce significativamente lo spazio sulla scheda e fornisce contatti anti-strappo per evitare errori di inserimento e di estrazione. (Immagine per gentile concessione di Molex)

Conclusione

Le schede flash microSDHC sono nate e sono principalmente utilizzate per l'archiviazione dei dati. Ora però stanno migliorando per supportare le esigenze specifiche derivanti dall'esecuzione della memoria del programma per i sistemi operativi embedded. Parte di questa evoluzione include lo sviluppo di memorie flash più veloci che possono supportare richieste di lettura costanti. Inoltre, i microcontroller si stanno evolvendo per supportare nuove interfacce di memoria che possono eseguire in modo affidabile il codice da una scheda microSDHC esterna, riducendo o eliminando gli errori tipici delle flash.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.