Nozioni di base sugli FPGA - Parte 4: Introduzione agli FPGA di Xilinx

Contributo di Editori nordamericani di DigiKey

2020-04-01

Nota del redattore: spesso le migliori soluzioni di progettazione sono date da combinazioni di processori RISC, CISC, grafici e FPGA, da soli FPGA o da FPGA dotati di hard core di processore integrati. Tuttavia, molti progettisti non conoscono le capacità degli FPGA, come si sono evoluti e come utilizzarli.La Parte 1 di questo articolo ha offerto un'introduzione avanzata agli FPGA; la Parte 2 era dedicata alle offerte di FPGA di Lattice Semiconductor, mentre nella Parte 3 l'attenzione era rivolta alle famiglie di dispositivi FPGA e agli strumenti di progettazione offerti da Microchip Technology (tramite la sua consociata Microsemi Corporation). Qui, nella Parte 4, vengono presi in esame i componenti e gli strumenti di Xilinx. Nella Parte 5 infine saranno illustrate le offerte di Altera.

Come discusso nella Parte 1, gli FPGA (gate array programmabili sul campo) hanno molte caratteristiche che li rendono una risorsa di calcolo inestimabile, sia da soli che inseriti in un'architettura eterogenea. Molti progettisti, tuttavia, non hanno familiarità con questi dispositivi e con il modo di incorporarli nei loro progetti.

Per superare questo ostacolo possiamo esaminare più a fondo le architetture degli FPGA e i relativi strumenti dei principali fornitori. Questo articolo si occupa della linea di Xilinx.

Panoramica delle opzioni FPGA di alto livello

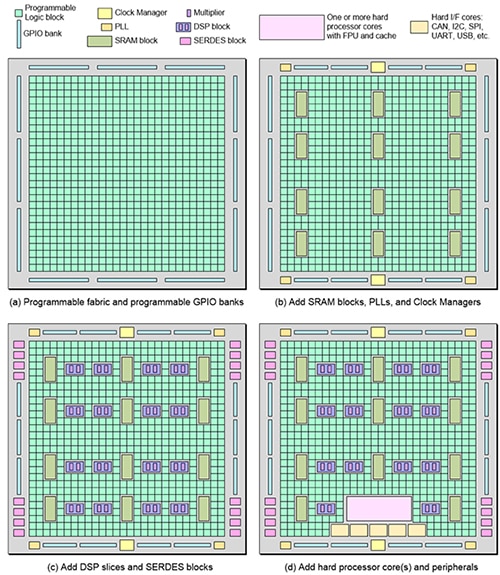

Esistono molti tipi di FPGA, ognuno con diverse combinazioni di capacità e funzioni. Il cuore di ogni FPGA è la sua struttura che si presenta come una serie di blocchi a logica programmabile, conosciuti anche come elementi logici (LE) (Figura 1a). Il livello successivo della struttura dell'FPGA include blocchi di SRAM, chiamati RAM di blocco (BRAM), circuiti ad aggancio di fase (PLL) e gestore di clock (Figura 1b). Possono essere inclusi anche blocchi processore di segnali digitali (DSP) (slice DSP) e blocchi serializzatori/deserializzatori (SERDES) ad alta velocità (Figura 1c).

Figura 1: Gli FPGA più semplici contengono solo struttura programmabile e GPIO per uso generale configurabili (a). Architetture diverse potenziano questa struttura fondamentale con blocchi SRAM, PLL e gestori di clock (b), blocchi DSP e interfacce SERDES (c), hard core di processore e periferiche (d). (Immagine per gentile concessione di Max Maxfield)

Figura 1: Gli FPGA più semplici contengono solo struttura programmabile e GPIO per uso generale configurabili (a). Architetture diverse potenziano questa struttura fondamentale con blocchi SRAM, PLL e gestori di clock (b), blocchi DSP e interfacce SERDES (c), hard core di processore e periferiche (d). (Immagine per gentile concessione di Max Maxfield)

Funzioni dell'interfaccia periferica come CAN, I2C, SPI, UART e USB possono essere implementate come soft core nella struttura programmabile, ma molti FPGA le includono come hard core nel chip. Allo stesso modo, i microprocessori possono essere implementati come soft core nella struttura programmabile o come hard core nel chip (Figura 1d). Gli FPGA con hard core di processore sono detti FPGA System-on-Chip (SoC). I vari FPGA offrono set di funzionalità, caratteristiche e capacità diverse mirate a specifici settori e applicazioni.

Esistono diversi fornitori di FPGA, tra cui Altera (acquisita da Intel), Atmel (acquisita da Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (anch'essa acquisita da Microchip Technology) e Xilinx.

Tutti questi fornitori mettono a disposizione diverse famiglie di FPGA; alcuni offrono FPGA SoC, altri dispositivi per applicazioni di intelligenza artificiale (IA) e apprendimento automatico (ML) e altri ancora offrono dispositivi che tollerano le radiazioni, studiati appositamente per ambienti ad alta radiazione come lo spazio. Data la grande varietà di famiglie, ognuna con risorse diverse, scegliere il dispositivo migliore per il compito da svolgere può essere difficile.

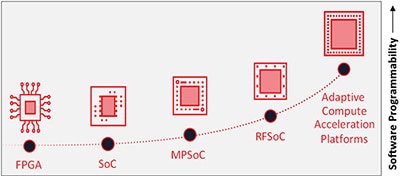

Presentazione di FPGA, SoC, MPSoC, RFSoC e ACAP di Xilinx

Xilinx offre dispositivi programmabili con prestazioni e capacità da basiche a estremamente elevate. Da FPGA tradizionali a SoC (struttura programmabile degli FPGA con un unico processore hard core), MPSoC (struttura programmabile degli FPGA con più hard core di processore), RFSoC (MPSoC con capacità RF) e ACAP (piattaforma di accelerazione del calcolo adattiva) (Figura 2).

Figura 2: Nel corso del tempo, il portafoglio delle architetture di Xilinx si è evoluto, passando da semplici FPGA contenenti solo struttura programmabile, a dispositivi SoC in cui tale struttura viene potenziata con un hard core di processore, a MPSoC con più processori, a RFSoC con capacità RF, fino all'ultima generazione di ACAP, pensata per applicazioni come quelle IA. (Immagine per gentile concessione di Max Maxfield)

Figura 2: Nel corso del tempo, il portafoglio delle architetture di Xilinx si è evoluto, passando da semplici FPGA contenenti solo struttura programmabile, a dispositivi SoC in cui tale struttura viene potenziata con un hard core di processore, a MPSoC con più processori, a RFSoC con capacità RF, fino all'ultima generazione di ACAP, pensata per applicazioni come quelle IA. (Immagine per gentile concessione di Max Maxfield)

Il portafoglio di Xilinx è talmente ampio, si rivolge a così tanti segmenti di mercato e offre una gamma così estesa di metodi di implementazione che chi non è esperto di FPGA potrebbe far fatica a orientarsi.

Per i mercati Xilinx si rivolge, ma non solo, a quello dei data center (calcolo, rete, storage); delle comunicazioni (cablate, wireless); aerospaziale e difesa; industriale, scientifico e medico (ISM); dei test, misurazione ed emulazione (TME); a quello automotive, broadcast e consumer.

Per i metodi di implementazione, vi sono quelli che Xilinx chiama Dispositivi Hardware Adattabili, che comprendono chip, schede di valutazione e kit di sviluppo; sistemi finali implementabili, che comprendono schede acceleratore System-on-Module (SoM) e PCIe; e FPGA come servizio (FAAS), che comprendono la valutazione e lo sfruttamento delle tecnologie di Xilinx attraverso i principali fornitori di cloud, tra cui Amazon Web Services (AWS), Alibaba.com e Nimbix.net.

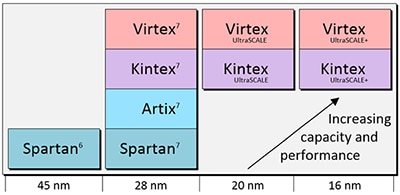

Per quanto riguarda le offerte di FPGA di Xilinx, un modo per classificarle è il nodo della tecnologia di processo (Figura 3).

Figura 3: Le offerte di FPGA di Xilinx offrono un ampio portafoglio multinodo per soddisfare le esigenze di numerose applicazioni. (Immagine per gentile concessione di Max Maxfield)

Figura 3: Le offerte di FPGA di Xilinx offrono un ampio portafoglio multinodo per soddisfare le esigenze di numerose applicazioni. (Immagine per gentile concessione di Max Maxfield)

A seconda dell'applicazione di destinazione, i progettisti possono optare per un FPGA a basso costo e con un ingombro compatto implementato in un vecchio nodo tecnologico o, nel caso di un'applicazione di connettività di rete di ultima generazione, ad esempio, possono scegliere un dispositivo ad alta capacità, elevata larghezza di banda e alte prestazioni implementato in un nodo tecnologico più recente.

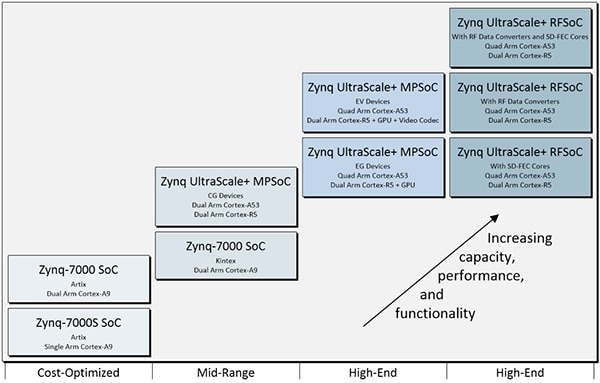

Nel caso di progetti che richiedono uno o più hard core di processore (e altre funzioni integrate nell'hardware come GPU, codec e decisioni software, core di rilevazione e correzione degli errori a valle (FEC)), Xilinx offre un portafoglio di dispositivi sotto il nome generale di Zynq. La Figura 4 mostra un riepilogo delle offerte di SoC, MPSoC e RFSoC Zynq. Questa suite di soluzioni fornisce ai progettisti un'ampia gamma di funzionalità per facilitare l'ottimizzazione di potenza, prestazioni, costi e time-to-market.

Figura 4: Le offerte di SoC, MPSoC e RFSoC di Xilinx integrano la programmabilità software di un processore con quella hardware di un FPGA, offrendo ai progettisti prestazioni, flessibilità e scalabilità del sistema. (Immagine per gentile concessione di Max Maxfield)

Figura 4: Le offerte di SoC, MPSoC e RFSoC di Xilinx integrano la programmabilità software di un processore con quella hardware di un FPGA, offrendo ai progettisti prestazioni, flessibilità e scalabilità del sistema. (Immagine per gentile concessione di Max Maxfield)

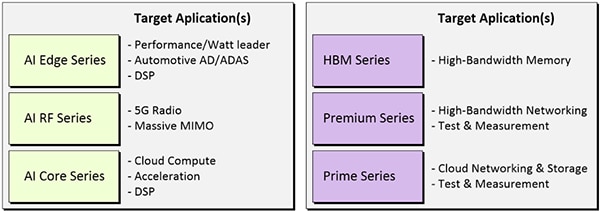

Le offerte più recenti di Xilinx sono i dispositivi ACAP (piattaforma di accelerazione del calcolo adattiva) Versal, tutti implementati nel nodo della tecnologia di processo a 7 nanometri (nm). Gli ACAP sono piattaforme di calcolo multicore altamente integrate, in grado di adattarsi ad algoritmi evolutivi e diversificati. Sono personalizzabili in modo dinamico a livello sia hardware che software per adattarsi a un'ampia gamma di applicazioni e carichi di lavoro. Gli ACAP architettati attorno a un NoC (Network-on-Chip) programmabile, possono essere facilmente programmati sia dai progettisti hardware che dagli sviluppatori software.

Le nuove caratteristiche dei dispositivi Versal includono motori intelligenti (una vasta gamma di processori vettoriali per carichi di lavoro ML e DSP); un NoC programmabile ad alta larghezza di banda, bassa latenza e bassa potenza in grado di spostare terabyte di dati; e una shell integrata che assicura migliori prestazioni, uso e produttività con un'infrastruttura di core pre-costruita e connettività di sistema.

La Figura 5 presenta una panoramica del portafoglio di ACAP Versal.

Figura 5: Gli ACAP Versal di Xilinx sono piattaforme di calcolo multicore altamente integrate, in grado di adattarsi ad algoritmi evolutivi e diversificati. Gli ACAP sono personalizzabili in modo dinamico a livello sia hardware che software per adattarsi a un'ampia gamma di applicazioni e carichi di lavoro. (Immagine per gentile concessione di Max Maxfield)

Figura 5: Gli ACAP Versal di Xilinx sono piattaforme di calcolo multicore altamente integrate, in grado di adattarsi ad algoritmi evolutivi e diversificati. Gli ACAP sono personalizzabili in modo dinamico a livello sia hardware che software per adattarsi a un'ampia gamma di applicazioni e carichi di lavoro. (Immagine per gentile concessione di Max Maxfield)

Come verrà discusso nella sezione sugli strumenti di progettazione, un elemento chiave di differenziazione associato ai dispositivi Versal è il nuovo stack software pensato per i data scientist e gli ingegneri software, oltre che per i progettisti di hardware tradizionale.

Xilinx mette a disposizione una miriade di dispositivi, ad esempio un FPGA Artix-7, un FPGA Kintex UltraScale, un FPGA Kintex UltraScale+, un modulo SoC Zynq-7000 di Trenz Electronic GmbH e un MPSoC Zynq UltraScale+.

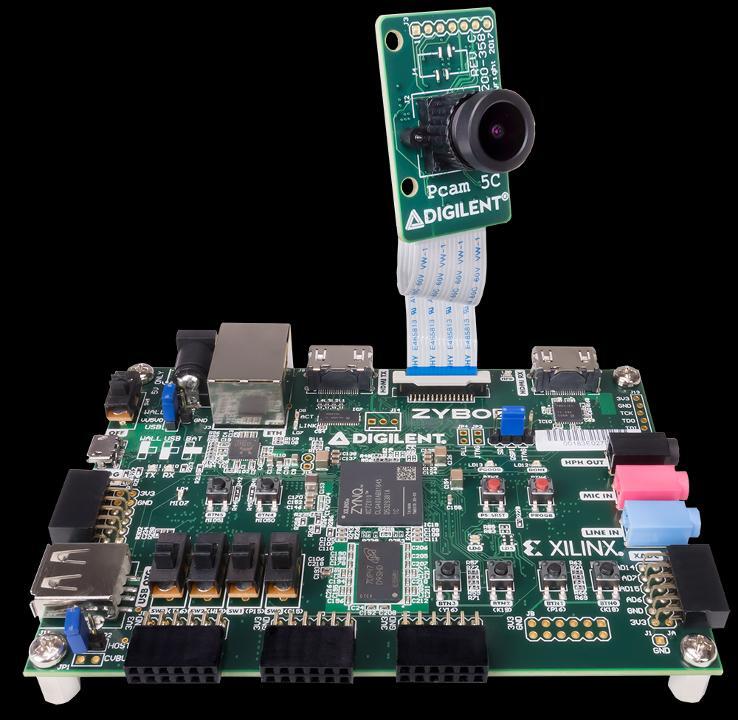

Inoltre, è fornita un'ampia gamma di schede di valutazione e di sviluppo, fra cui una numerose schede di valutazione: FPGA Artix-7 di Digilent, FPGA Kintex UltraScale di Analog Devices, FPGA Kintex UltraScale+ di Xilinx, FPGA SoC Zynq-7000 di Digilent e FPGA MPSoC Zynq UltraScale+, sempre di Xilinx.

Progettazione e sviluppo con gli FPGA, i SoC e gli ACAP di Xilinx

Rispetto alla concorrenza, Xilinx si differenzia per l'ampiezza e la profondità dei suoi flussi e strumenti di progettazione.

Nella Parte 1 di questa serie sugli FPGA è stato osservato che, tradizionalmente, per progettare questi dispositivi gli ingegneri utilizzano un linguaggio di descrizione dell'hardware (HDL) come Verilog o VHDL che coglie l'obiettivo del progetto a un livello di astrazione noto come livello di trasferimento del registro (RTL). Queste descrizioni RTL possono prima essere simulate per verificare che funzionino come richiesto, dopodiché vengono passate a uno strumento di sintesi che genera il file di configurazione utilizzato per programmare l'FPGA.

Nel passo successivo di astrazione viene colto l'obiettivo del progetto usando un linguaggio di programmazione come C/C++, o un'implementazione speciale come SystemC, ossia un insieme di classi C++ e macro che forniscono un'interfaccia di simulazione guidata dagli eventi e facilitano la simulazione di processi concomitanti, ognuno dei quali è descritto con una sintassi C++ semplice. Queste descrizioni possono essere analizzate e profilate eseguendole come dei normali programmi, dopodiché vengono passate a un motore di sintesi ad alto livello (HLS). L'RTL risultante viene quindi immesso nel normale motore di sintesi.

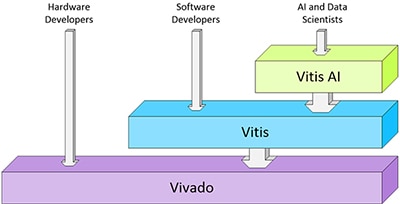

Tutte queste funzionalità sono incluse nelle Edizioni HLx di Vivado® Design Suite, che produce il bitstream di configurazione da caricare nei dispositivi di destinazione FPGA, SoC, MPSoC, RFSoC o ACAP. Oltre a consentire agli sviluppatori hardware di sfruttare la progettazione basata su C e il riutilizzo ottimizzato, Vivado fornisce anche il riutilizzo del sottosistema IP, l'automazione dell'integrazione e la chiusura accelerata del progetto (Figura 6).

Figura 6: Una vista di alto livello della nutrita serie di strumenti di progettazione Vivado e Vitis di Xilinx mostra come gli utenti possano utilizzarli ai livelli di astrazione più appropriati. I progettisti hardware lavorano con Vivado, gli sviluppatori software lavorano con Vitis e i data scientist e gli specialisti di intelligenza artificiale lavorano con Vitis AI. (Immagine per gentile concessione di Max Maxfield)

Figura 6: Una vista di alto livello della nutrita serie di strumenti di progettazione Vivado e Vitis di Xilinx mostra come gli utenti possano utilizzarli ai livelli di astrazione più appropriati. I progettisti hardware lavorano con Vivado, gli sviluppatori software lavorano con Vitis e i data scientist e gli specialisti di intelligenza artificiale lavorano con Vitis AI. (Immagine per gentile concessione di Max Maxfield)

Il successivo livello di astrazione è supportato dalla piattaforma software unificata Vitis, che offre agli sviluppatori software la possibilità di costruire senza soluzione di continuità applicazioni accelerate. Basata concettualmente su Vitis, Vitis AI consente agli esperti di IA e ai data scientist di lavorare al livello di astrazione TensorFlow. Vitis AI è una piattaforma di sviluppo per l'inferenza dell'IA sulle piattaforme hardware di Xilinx, inclusi sia i dispositivi periferici che le schede PCIe Alveo. È costituita da IP ottimizzati, strumenti, librerie, modelli e progetti di esempio, ed è studiata per sfruttare tutto il potenziale di accelerazione IA sui dispositivi FPGA e ACAP di Xilinx.

Vitis AI alimenta Vitis, che a sua volta alimenta Vivado. Ciò che emerge più chiaramente dalla Figura 6 è che gli utenti "vedono" solo ciò che devono "vedere". Gli sviluppatori hardware "vedranno" solo Vivado, gli sviluppatori software "vedranno" solo Vitis e gli esperti di IA e i data scientist "vedranno" solo Vitis AI. In questo modo, gli utenti possono lavorare con gli strumenti ai livelli di astrazione più appropriati.

Fornire agli sviluppatori software una suite di strumenti come Vitis, che li isola dall'hardware sottostante, apre gli FPGA a un pool di sviluppatori molto più ampio. La stessa cosa accade con gli esperti di IA e i data scientist che, disponendo di una suite di strumenti come Vitis AI, possono concentrarsi sul proprio livello di astrazione, essendo isolati dal software sottostante.

Nel fornire queste capacità, Xilinx è in prima linea per portare gli strumenti FPGA a livelli sempre più alti di astrazione progettuale che consentiranno agli sviluppatori di sfruttare più facilmente le capacità di questi dispositivi e di integrarli nei loro prossimi progetti.

Conclusione

Spesso le migliori soluzioni progettuali per l'elaborazione sono date da combinazioni di processori e FPGA, da soli FPGA o da FPGA dotati di hard core di processore integrati. La tecnologia degli FPGA si è evoluta rapidamente nel corso degli anni ed è in grado di soddisfare numerosi requisiti di progettazione in termini di flessibilità, velocità di elaborazione e potenza, il che rende questi dispositivi molto utili per un'ampia gamma di applicazioni, dalle interfacce intelligenti alla visione artificiale e all'intelligenza artificiale.

Come è stato dimostrato, Xilinx offre dispositivi programmabili con prestazioni e capacità da basiche a estremamente elevate in grado di coprire l'intero spettro di possibilità. Spaziano da FPGA tradizionali a SoC (struttura programmabile degli FPGA con un unico processore hard core), MPSoC (struttura programmabile degli FPGA con più hard core di processore), RFSoC (MPSoC con capacità RF) e ACAP (piattaforma di accelerazione del calcolo adattiva).

Per aiutare a creare progetti con questi dispositivi, Xilinx offre una suite di strumenti in grado di rispondere alle esigenze degli sviluppatori hardware (Vivado), degli sviluppatori software (Vitis) e degli esperti di IA e dei data scientist (Vitis AI).

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.