Come utilizzare gli FPGA in applicazioni con vincoli di risorse

Contributo di Editori nordamericani di DigiKey

2025-05-07

L'esigenza di logica configurabile è in aumento nei sistemi embedded dalle risorse limitate. Applicazioni come l'Edge IA, la visione artificiale e l'automazione industriale richiedono una logica flessibile e specifica per l'applicazione, in grado di soddisfare le esigenze di prestazioni in continua evoluzione e di funzionare entro rigorosi limiti in termini di potenza, dimensioni e costi. I moderni gate array programmabili sul campo (FPGA) possono rispondere a queste esigenze contrastanti.

Questo articolo esamina i principali criteri di progettazione da considerare nella scelta di un FPGA per applicazioni con vincoli di risorse. Descrive quindi come le diverse linee di prodotti si adattano a scenari specifici, utilizzando esempi tratti dal portafoglio di FPGA dalla potenza e dai costi ottimizzati di Altera. Si conclude evidenziando i kit di sviluppo e le schede di valutazione che possono essere utilizzati per prototipare e convalidare i concetti progettuali.

Considerazioni sulla scelta di un FPGA

La scelta di un FPGA per un sistema con risorse limitate implica la considerazione di molteplici requisiti di progettazione e la loro idoneità con la soluzione corretta. Sono diverse le caratteristiche chiave da considerare per un FPGA:

Capacità di elementi logici (LE): essendo il componente costitutivo di un FPGA, il numero di LE determina la quantità di logica personalizzata implementabile. Quantità più elevate portano a progetti più complessi: il compromesso è l'aumento della potenza, del costo e delle dimensioni del contenitore.

I/O e memoria: gli FPGA sono spesso utilizzati per collegare componenti diversi all'interno di un sistema, il che rende il numero di pin di I/O una considerazione fondamentale. Per aumentare le prestazioni di I/O, molti FPGA incorporano blocchi logici fissi e adatti a interfacce come PCI Express (PCIe), memoria ad alta velocità e transceiver multi-gigabit.

Inoltre, alcuni FPGA integrano funzioni come i convertitori analogico/digitale (ADC) e la memoria flash. Questi miglioramenti possono ridurre la necessità di chip complementari, risparmiando spazio sulla scheda e migliorando l'efficienza energetica.

Integrazione del processore: anziché utilizzare un processore esterno, è possibile implementare un'unità microprocessore (MPU) "soft" all'interno dell'FPGA. Questo approccio può ridurre l'ingombro di un sistema, ma è più adatto ad applicazioni con carichi di lavoro MPU meno impegnativi.

Per le applicazioni che richiedono MPU più veloci ed efficienti, i progettisti possono prendere in considerazione un FPGA con un HPS (Hard Processor System) che implementa una MPU come blocco logico fisso all'interno dell'FPGA.

Acceleratori hardware: gli FPGA di solito includono blocchi dedicati all'elaborazione di segnali digitali (DSP) che gestiscono in modo efficiente compiti ad alta intensità di calcolo come il controllo del movimento. I dispositivi di fascia più alta potrebbero essere dotati di blocchi tensoriali specializzati per i carichi di lavoro di IA. Le capacità di questi blocchi acceleratori variano in modo significativo tra le varie famiglie di FPGA e possono influire notevolmente sulle prestazioni complessive del sistema.

Ottimizzazione del contenitore e della potenza: alcuni FPGA sono progettati appositamente per ridurre al minimo l'ingombro fisico ed elettrico. Possono offrire ad esempio la modalità di sospensione a basso consumo.

Strumenti: la creazione di logica personalizzata può essere scoraggiante, soprattutto per i progettisti alle prime armi. Per semplificare il processo sono nati strumenti come Quartus Prime Design Software di Altera.

Creato per rendere più accessibile la progettazione di FPGA, Quartus Prime offre un'esperienza intuitiva per lo sviluppatore, un ampio catalogo di blocchi logici precostituiti e la possibilità di interconnetterli automaticamente. Lo strumento si integra con i più diffusi flussi di lavoro di IA e apprendimento automatico (ML), consentendo agli sviluppatori di implementare su un FPGA i sistemi operativi (OS) più diffusi, come Linux e Zephyr.

Funzionalità del genere possono accelerare in modo significativo la progettazione di FPGA, rendendo le caratteristiche dello strumento una considerazione fondamentale nella scelta del dispositivo.

Calcolo ad alte prestazioni per carichi di lavoro embedded avanzati

Per illustrare come i requisiti di progettazione influenzino la scelta dell'FPGA, è utile iniziare con applicazioni di fascia alta che richiedono una densità di calcolo, una larghezza di banda e un'integrazione eccezionali. Tra gli esempi vi sono le applicazioni di IA avanzate e i gateway industriali ad alte prestazioni.

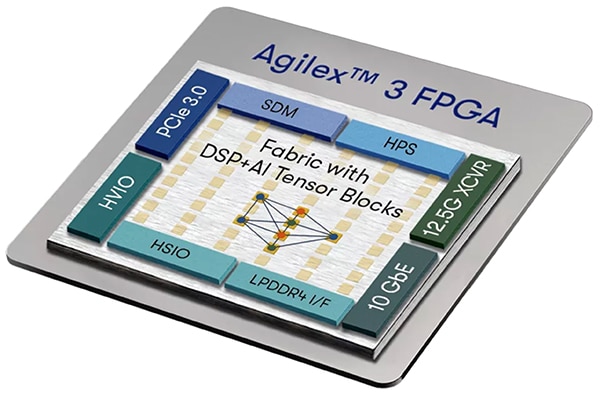

Gli FPGA Agilex 3 (Figura 1) sono progettati per soddisfare queste esigenze applicative, offrendo fino a 135K LE. I chip sono disponibili nelle varianti solo FPGA e System-on-Chip (SoC). I dispositivi SoC integrano un dual core ARM® Cortex®-A55 da 800 MHz, che consente all'FPGA di gestire complessi stack software come interfacce uomo-macchina (HMI) o stack di rete.

Il tessuto programmabile è dotato di blocchi tensoriali IA in grado di fornire fino a 2,8 tera di operazioni INT8 al secondo (TOPS). Questi blocchi supportano vari formati di calcolo, tra cui FP16, FP19, FP32 e BFLOAT16, e sono ottimizzati per l'esecuzione efficiente di carichi di lavoro di IA. Sono inclusi anche blocchi DSP a precisione variabile che offrono prestazioni fino a 180 giga di operazioni in virgola mobile al secondo (GFLOPS) per l'elaborazione generale dei segnali.

Figura 1: Agilex 3 si distingue per i suoi blocchi DSP e tensoriali IA ad alte prestazioni. (Immagine per gentile concessione di Altera)

Figura 1: Agilex 3 si distingue per i suoi blocchi DSP e tensoriali IA ad alte prestazioni. (Immagine per gentile concessione di Altera)

La connettività ad alta velocità è un altro punto di forza dell'architettura Agilex 3. I transceiver supportano velocità dati fino a 12,5 Gbps, con blocchi I/O disponibili per interfacce di memoria PCIe 3.0, 10 Gigabit Ethernet (GbE) e LPDDR4. Il supporto della sincronizzazione temporale di precisione IEEE 1588 ne aumenta ulteriormente l'idoneità per le reti industriali in tempo reale.

Il dispositivo A3CZ135BB18AE7S illustra le capacità di questa famiglia. Include 135K LE, 184 blocchi DSP e fornisce 2,54 TOPS.

Integrazione avanzata per sistemi complessi

Per applicazioni come l'automazione industriale e i sistemi di visione di fascia media, la potenza di calcolo grezza può essere meno importante della capacità di supportare configurazioni complesse con grandi quantità di logica e I/O personalizzati. Gli FPGA Cyclone V sono adatti a questi scenari, in quanto offrono fino a 300K LE ed estese interfacce ad alta velocità. Come Agilex 3, questi chip sono disponibili nelle varianti solo FPGA e SoC. In questo caso, i dispositivi SoC integrano un dual core ARM Cortex-A9.

La struttura programmabile di questi chip comprende blocchi DSP a precisione variabile che supportano la moltiplicazione tripla 9 × 9 e doppia 18 × 18 a virgola fissa e la moltiplicazione 27 × 27 a virgola fissa o flottante. Questi blocchi possono essere utilizzati per l'elaborazione avanzata dei segnali e l'IA.

Un'ampia gamma di I/O supporta diversi livelli di tensione e tipi di interfaccia. I blocchi logici consentono una connettività avanzata ad alta velocità, tra cui PCIe 2.0, controller DDR3 e transceiver funzionanti fino a 6,144 Gbps.

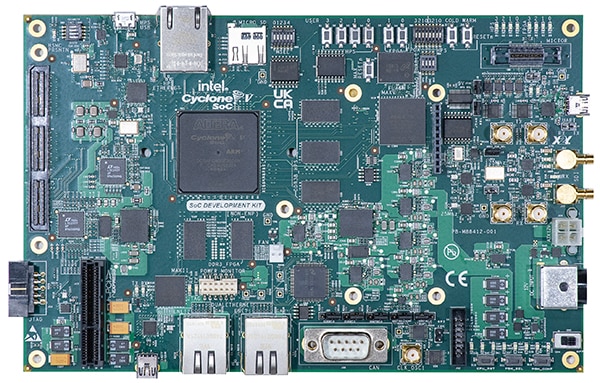

Gli sviluppatori possono valutare la famiglia di SoC Cyclone V utilizzando il kit di sviluppo DK-DEV-5CSXC6N-B (Figura 2). Questo kit è stato progettato per la prototipazione rapida di sistemi complessi ad alta produttività.

Figura 2: Il kit di sviluppo Cyclone V DK-DEV-5CSXC6N-B supporta la prototipazione ad alte prestazioni. (Immagine per gentile concessione di Altera)

Figura 2: Il kit di sviluppo Cyclone V DK-DEV-5CSXC6N-B supporta la prototipazione ad alte prestazioni. (Immagine per gentile concessione di Altera)

Il kit comprende diverse caratteristiche degne di nota:

- Due porte Ethernet, un connettore PCIe x4 e un HSMC (High-Speed Mezzanine Card) a 16 canali LVDS in ciascuna direzione

- USB 2.0 OTG, CAN, UART e un'interfaccia LCD a due righe di testo

- 1 GB di SDRAM DDR3 per FPGA e HPS, 128 MB di Flash Quad-SPI e una scheda microSD da 4 GB

La scheda offre il dispositivo 5CSXFC5D6F31C8N, che include un processore dual core ARM Cortex-A9 a 600 MHz, con 85.000 LE, 87 blocchi DSP e 288 pin di I/O in un contenitore 896-FBGA di 31 × 31 mm.

Logica configurabile ad alta efficienza energetica in un contenitore compatto

I vincoli di spazio e di consumo energetico sono critici per molte applicazioni. Tra gli esempi vi sono le interfacce di sensori, il sequenziamento della potenza e il controllo delle periferiche. Gli FPGA come la famiglia MAX 10 sono una soluzione efficace in questi casi. I dispositivi MAX 10 sono disponibili in configurazioni da 2000 a 50.000 LE e in contenitori di 3 × 3 mm.

Le caratteristiche principali includono fino a due ADC a 12 bit integrati, un'interfaccia di memoria DDR3 e blocchi moltiplicatori che supportano le modalità 18 × 18 e doppia 9 × 9 a virgola fissa. La flash su chip con supporto per due dispositivi di storage di immagini consente all'FPGA di configurarsi da solo senza un dispositivo di memoria esterno.

Le capacità di risparmio energetico sono uno degli attributi più caratteristici della famiglia MAX 10. La modalità di sospensione incorporata può ridurre il consumo energetico dinamico fino al 95%. Grazie alla flash su chip, i dispositivi possono anche essere completamente spenti e riprendere a funzionare in meno di 10 ms.

L'opzione di alimentazione singola semplifica ulteriormente la distribuzione dell'energia elettrica. Ciò rende i dispositivi MAX 10 particolarmente adatti a ruoli di supervisione, in cui i domini della potenza possono dover entrare in funzione prima del resto del sistema.

Gli sviluppatori interessati alla famiglia MAX 10 possono valutarla utilizzando la scheda di valutazione per FPGA MAX 10 EK-10M08E144 (Figura 3). Questa scheda consente l'accesso ai segnali esterni tramite i connettori Arduino UNO R3 e i punti di prova, con un layout progettato per supportare la misurazione delle prestazioni dell'ADC e il comportamento generale dell'alimentazione.

Figura 3: La scheda di valutazione per FPGA MAX 10 EK-10M08E144 offre un facile accesso agli I/O principali. (Immagine per gentile concessione di Altera)

Figura 3: La scheda di valutazione per FPGA MAX 10 EK-10M08E144 offre un facile accesso agli I/O principali. (Immagine per gentile concessione di Altera)

La scheda è dotata del dispositivo 10M08SAE144C8G, che include 8000 LE e un singolo ADC in un contenitore LQFP a 144 pin. Oltre alle risorse hardware incorporate, questo FPGA supporta il processore soft Nios V basato su RISC-V, che consente ai progettisti di implementare funzioni di controllo leggere senza bisogno di un'unità microcontroller (MCU) esterna.

Prestazioni equilibrate per applicazioni di fascia media

Alcune applicazioni richiedono una capacità di logica e di I/O superiore a quella che possono fornire gli FPGA entry-level. Tra gli esempi vi sono la fusione sensoriale, il controllo del movimento e la derivazione in parallelo chip-chip. Gli FPGA Cyclone 10 LP rispondono a questi requisiti offrendo fino a 120.000 LE e 525 pin di I/O in dispositivi ottimizzati per bilanciare potenza e larghezza di banda in applicazioni sensibili ai costi.

Come MAX 10, la famiglia include blocchi DSP adatti a carichi di lavoro quali filtraggio, anello di controllo e inferenza IA di base. A differenza di MAX 10, i dispositivi Cyclone 10 LP incorporano veri transceiver LVDS e terminazione su chip (OCT) per supportare l'interfacciamento digitale ad alta velocità.

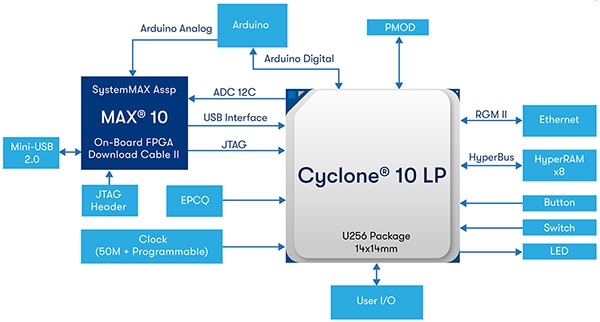

Gli sviluppatori interessati alla famiglia Cyclone 10 LP possono valutarla utilizzando il kit di valutazione per Cyclone 10 EK-10CL025U256 (Figura 4). Questa scheda offre connettori Arduino UNO R3 e Digilent Pmod per una facile espansione. Altre caratteristiche includono GbE, USB 2.0, 128 Mb di SDRAM e 64 Mb di memoria flash.

Figura 4: Il kit di valutazione per Cyclone 10 EK-10CL025U256 supporta una facile espansione delle periferiche. (Immagine per gentile concessione di Altera)

Figura 4: Il kit di valutazione per Cyclone 10 EK-10CL025U256 supporta una facile espansione delle periferiche. (Immagine per gentile concessione di Altera)

La scheda è dotata del dispositivo 10CL025YU256C8G, che include 25.000 LE, 66 blocchi DSP e 150 pin di I/O in un contenitore di 14 × 14 mm. Come MAX 10, la famiglia Cyclone 10 LP supporta il processore soft Nios V.

Conclusione

I progettisti hanno una flessibilità mai vista prima nell'implementazione di logica personalizzata nei sistemi embedded. Le applicazioni ad alte prestazioni possono beneficiare di FPGA con acceleratori IA integrati. I progetti a basso consumo possono sfruttare i dispositivi con modalità di sospensione. I sistemi ad alta intensità di I/O possono sfruttare chip con un elevato numero di pin e interfacce ad alta velocità. È importante notare che tutte queste funzionalità possono essere realizzate entro le rigide limitazioni dei sistemi embedded con risorse limitate, grazie a kit intuitivi.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.