Nozioni di base sulla sicurezza IoT - Parte 3: Garantire l'avvio sicuro e l'aggiornamento del firmware

Contributo di Editori nordamericani di DigiKey

2020-06-18

Nota del redattore: nonostante la proliferazione dei dispositivi IoT, la sicurezza è una preoccupazione costante, al punto che le sfide alla sicurezza possono rappresentare un ostacolo all'adozione di dispositivi connessi all'Internet delle cose industriale (IIoT) e ad applicazioni mission-critical in cui i dati aziendali e personali possono essere compromessi in caso di un attacco portato a segno. La sicurezza delle applicazioni IoT può rivelarsi complessa, ma in realtà la sicurezza dei dispositivi IoT può basarsi su alcuni principi relativamente semplici che sono supportati dai dispositivi di sicurezza hardware. Seguendo pratiche di sicurezza consolidate si possono affrontare queste preoccupazioni. Questa serie in più parti funge da guida pratica per aiutare gli sviluppatori a seguire fin dall'inizio le best practice. Nella Parte 1 sono discussi gli algoritmi di crittografia alla base di progetti sicuri. La Parte 2 tratta il ruolo delle chiavi private, la gestione delle chiavi e lo storage sicuro in sistemi sicuri. Questa Parte 3 esamina i meccanismi incorporati nei processori sicuri per mitigare altri tipi di minacce ai dispositivi IoT. La Parte 4 identifica e mostra come applicare i meccanismi di sicurezza nei processori avanzati per garantire l'isolamento necessario al fine di mitigare gli attacchi all'ambiente di runtime dei dispositivi IoT. La Parte 5 descrive come la sicurezza IoT continua dai dispositivi IoT attraverso misure di sicurezza di alto livello utilizzate per connettere tali dispositivi alle risorse cloud IoT.

Utilizzati in combinazione, la crittografia basata sull'hardware e lo storage sicuro forniscono le funzionalità essenziali per implementare progetti di Internet delle cose (IoT) sicuri. Una volta installati, tuttavia, i dispositivi IoT devono far fronte a molte minacce studiate per sovvertirli, per lanciare attacchi immediati o più persistenti e capillari.

Questo articolo descrive come gli sviluppatori possano migliorare la sicurezza dei dispositivi IoT, utilizzando una radice di attendibilità basata su meccanismi di sicurezza sottostanti per fornire un ambiente attendibile per l'esecuzione di software su processori sicuri di produttori come Maxim Integrated, Microchip Technology, NXP Semiconductors e Silicon Labs.

Che cos'è la radice di attendibilità e perché è necessaria?

I metodi crittografici e le chiavi sicure sono fattori determinanti cruciali per la sicurezza in qualsiasi dispositivo connesso. Come osservato nella Parte 1 e nella Parte 2 di questa serie, sono i meccanismi fondamentali utilizzati dai protocolli di livello superiore per proteggere i dati e le comunicazioni. La protezione del sistema stesso richiede agli sviluppatori di tener conto delle vulnerabilità che possono influenzare il funzionamento del sistema e l'esecuzione del software nei sistemi embedded.

In un tipico sistema embedded, il reset del sistema per via di un'interruzione di corrente o di un'eccezione software comporta il riavvio del software per ricaricare un'immagine del firmware dalla memoria non volatile. Normalmente, il riavvio del software è un importante meccanismo di sicurezza utilizzato per ripristinare il funzionamento di un sistema che si è destabilizzato accidentalmente o intenzionalmente. Nei sistemi connessi, in cui gli hacker utilizzano svariati strumenti black hat per compromettere il software, gli specialisti della sicurezza spesso raccomandano il riavvio per contrastare le intrusioni che influenzano l'esecuzione del software. Ad esempio, nel 2018 l'FBI ha raccomandato ai consumatori e agli imprenditori di riavviare i loro router per contrastare una massiccia campagna di hacking allora in corso.

Nella pratica però, il riavvio non è una garanzia di integrità del sistema. Dopo il riavvio con un'immagine del firmware compromessa, il sistema rimane ancora sotto il controllo dell'hacker. Per mitigare questo tipo di minacce, gli sviluppatori devono assicurarsi che il loro software funzioni su una catena di attendibilità basata su una radice di attendibilità stabilita al momento dell'avvio e che si estende a tutti i livelli dell'ambiente di esecuzione software. La capacità di raggiungere questo livello di sicurezza dipende in modo critico dalla garanzia che il processo di avvio inizi con un firmware attendibile.

Verifica delle immagini del firmware per l'avvio sicuro

In un sistema embedded, il processore host carica un'immagine del firmware dalla memoria flash principale e inizia a eseguirla (o inizia direttamente dalla flash con capacità execute-in-place (XIP)). Se gli hacker hanno compromesso l'immagine del firmware, il processo di avvio si traduce in un sistema compromesso.

Per verificare l'integrità del firmware prima dell'avvio, gli sviluppatori utilizzano un processo di firma del codice fin dall'inizio della supply chain. All'interno di una struttura sicura, l'immagine del firmware del sistema è firmata con una chiave privata da una coppia di chiavi private-pubbliche creata con un algoritmo crittograficamente robusto come l'algoritmo ECDSA (Elliptic Curve Digital Signature Algorithm). Se la chiave privata non lascia mai la struttura, la chiave pubblica invece viene spedita con il sistema. Durante l'avvio, il processore applica questa chiave pubblica del sistema per verificare la firma del firmware prima di utilizzare l'immagine.

Naturalmente, il processo appena descritto lascia la chiave pubblica stessa vulnerabile e, per estensione, lascia il firmware del sistema vulnerabile alla sostituzione non autorizzata. Se la chiave pubblica rimane non protetta nel sistema embedded, gli hacker potrebbero potenzialmente sostituirla con una chiave pubblica proveniente da una coppia di chiavi pubbliche-private da loro stessi generata. Se sostituiscono l'immagine del firmware del sistema con un firmware dannoso firmato con la relativa chiave privata in loro possesso, la firma del firmware compromesso supera la verifica e il processo di avvio procede, risultando in un sistema compromesso.

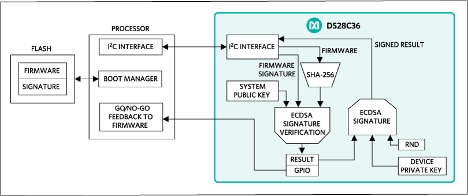

Per questo motivo, i sistemi sicuri si basano su una chiave pubblica valida che viene fornita in un elemento sicuro all'interno dell'impianto di sicurezza. I CI di sicurezza come DS28C36 di Maxim Integrated e ATECC608A di Microchip Technology offrono sia la memorizzazione sicura di un elemento di sicurezza tradizionale, sia l'esecuzione sicura degli algoritmi di autenticazione, come ECDSA per la verifica della firma del firmware.

Prima dell'avvio, il processore host ad esempio può inviare a DS28C36 il firmware tramite un'interfaccia seriale. A sua volta, DS28C36 utilizza la chiave pubblica del sistema fornita in precedenza nella struttura sicura per verificare che la firma del firmware sia stata effettivamente creata con la chiave privata associata nella stessa struttura sicura. Infine, DS28C36 segnala il risultato della verifica al processore host, che procede a caricare l'immagine del firmware se la firma è valida (Figura 1).

Figura 1: Gli sviluppatori possono utilizzare CI di sicurezza come DS28C36 di Maxim Integrated per verificare le firme del firmware ed evitare che il processore host avvii un firmware compromesso. (Immagine per gentile concessione di Maxim Integrated)

Figura 1: Gli sviluppatori possono utilizzare CI di sicurezza come DS28C36 di Maxim Integrated per verificare le firme del firmware ed evitare che il processore host avvii un firmware compromesso. (Immagine per gentile concessione di Maxim Integrated)

Un processo di avvio più sicuro protegge l'immagine del firmware per eliminare qualsiasi timore che le chiavi o le immagini siano compromesse. Grazie all'utilizzo di acceleratori per lo storage sicuro e la crittografia, un numero crescente di processori è dotato di efficaci capacità di avvio sicuro, tra questi i processori Gecko Series 2 di Silicon Laboratories, LPC55S69JBD100 di NXP, MAX32520 di Maxim Integrated e ATSAML11D16A di Microchip Technology. Utilizzando queste capacità, questa classe di processori sicuri può fornire la radice di attendibilità necessaria per creare un ambiente attendibile per l'esecuzione di software di sistema e applicativo.

Fornire una radice di attendibilità attraverso l'avvio sicuro

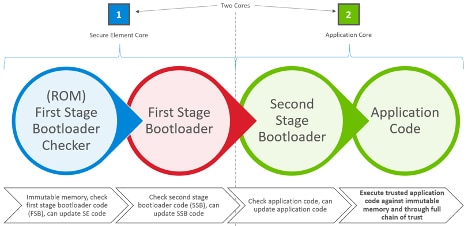

I processori sicuri di questa classe offrono opzioni di avvio sicuro, progettate per garantire l'integrità dell'immagine del firmware alla base della radice di attendibilità. Ad esempio, i processori Gecko Series 2 EFR32MG21A e EFR32BG22 di Silicon Laboratories generano questa radice di attendibilità attraverso un processo di avvio multistadio basato rispettivamente su un elemento hardware sicuro e su un elemento virtuale sicuro (VSE) (Figura 2).

Figura 2: Il processore Gecko Series 2 EFR32MG21A di Silicon Laboratories utilizza un elemento hardware integrato sicuro nel primo stadio del processo di avvio multistadio (mostrato qui), mentre EFR32BG22 avvia il processo di avvio multistadio con un elemento virtuale sicuro. (Immagine per gentile concessione di Silicon Laboratories)

Figura 2: Il processore Gecko Series 2 EFR32MG21A di Silicon Laboratories utilizza un elemento hardware integrato sicuro nel primo stadio del processo di avvio multistadio (mostrato qui), mentre EFR32BG22 avvia il processo di avvio multistadio con un elemento virtuale sicuro. (Immagine per gentile concessione di Silicon Laboratories)

In EFR32MG21A, un core di processore dedicato fornisce funzionalità crittografiche insieme a un elemento hardware sicuro per la memorizzazione sicura delle chiavi. Supportato da questa capacità dedicata, il processore esegue il processo di avvio utilizzando il codice residente nella memoria di sola lettura (ROM) per verificare il codice del bootloader di primo stadio (FSB). Una volta verificato, esegue il codice FSB, che a sua volta verifica la firma del codice del bootloader di secondo stadio (SSB). La sequenza di avvio continua con l'esecuzione dell'SSB verificato, che a sua volta verifica la firma del codice applicativo, che tipicamente comprende sia il codice a livello di sistema che il codice applicativo di livello superiore. Infine, viene eseguito il codice applicativo verificato e le operazioni di sistema procedono come richiesto dall'applicazione.

Poiché questo processo inizia con il codice ROM ed esegue solo codice FSB, SSB e codice applicativo verificati, questo approccio si traduce in una catena di attendibilità verificata per l'esecuzione del codice. Dato che il primo anello di questa catena di attendibilità si basa su un codice ROM immodificabile, ogni anello successivo della catena estende questo ambiente di attendibilità. Al tempo stesso, questo approccio permette agli sviluppatori di aggiornare in modo sicuro il codice applicativo e anche il codice del bootloader di primo e secondo stadio. Fintantoché ogni pacchetto di codice fornisce una firma verificata, l'ambiente di attendibilità rimane intatto.

I processori che offrono questo tipo di avvio sicuro con una radice di attendibilità tipicamente supportano più modalità e opzioni. Ad esempio, i processori Gecko Series 2 di Silicon Laboratories offrono una maggiore capacità di avvio sicuro basato su certificato.

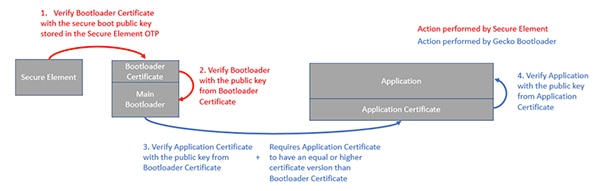

Utilizzati nelle transazioni di routine delle infrastrutture a chiave pubblica (PKI), i certificati contengono la chiave pubblica e un riferimento a uno o più certificati associati che in ultima analisi puntano a un certificato radice concesso da un'autorità di certificazione (CA). Ogni certificato di questa catena serve a verificare il certificato o i certificati sottostanti, dando luogo a una catena di attendibilità basata su una CA attendibile. I browser si affidano a questa catena di attendibilità durante la fase di autenticazione del Transport Layer Security (TLS) per confermare l'identità dei server Web. Allo stesso modo, i sistemi embedded possono utilizzare i certificati per confermare l'identità della fonte del bootloader o del codice applicativo. Qui, il processo di avvio in più fasi procede come descritto in precedenza, ma con un'ulteriore verifica del certificato associato a ogni fase (Figura 3).

Figura 3: I processori Gecko Series 2 di Silicon Laboratories migliorano la sicurezza del sistema verificando i certificati delle chiavi pubbliche utilizzate durante la verifica della firma in ogni fase del processo di avvio. (Immagine per gentile concessione di Silicon Laboratories)

Figura 3: I processori Gecko Series 2 di Silicon Laboratories migliorano la sicurezza del sistema verificando i certificati delle chiavi pubbliche utilizzate durante la verifica della firma in ogni fase del processo di avvio. (Immagine per gentile concessione di Silicon Laboratories)

Altri processori, come LPC55S69JBD100 di NXP, supportano una svariate altre opzioni per l'immagine del firmware. Oltre alle immagini firmate del firmware, questi processori supportano le immagini di avvio utilizzando lo standard industriale del Trusted Computing Group, il motore di composizione dell'identificativo del dispositivo (DICE). Una terza opzione permette agli sviluppatori di memorizzare le immagini in speciali regioni della flash del processore che supportano il cifrario PRINCE, un cifrario a blocchi a bassa latenza che può raggiungere un livello di sicurezza paragonabile ad altri cifrari ma su un'area di silicio molto più piccola. Implementato in LPC55S69JBD100, il cifrario PRINCE può eseguire la decodifica al volo del codice criptato o dei dati memorizzati nelle regioni della flash PRINCE dedicate del processore. Poiché le chiavi segrete utilizzate per la decrittazione sono accessibili solo al motore di crittografia PRINCE, questo processo rimane sicuro. Infatti, queste chiavi segrete sono protette da una chiave di cifratura a chiave (KEK) generata dalla funzione fisica non clonabile (PUF) di LPC55S69JBD100. (Per ulteriori informazioni sull'uso di PUF e KEK, vedere la Parte 2.)

Questo approccio dà agli sviluppatori la possibilità di memorizzare ulteriori immagini del firmware - una capacità necessaria per fornire ai dispositivi IoT metodi di aggiornamento del firmware via etere (FOTA) senza il rischio di far stallare il dispositivo. Se il processore può usare una sola posizione per memorizzare le immagini del firmware, un'immagine del firmware difettosa può portare il processore in uno stato indeterminato o bloccato che lo blocca. Memorizzando le immagini del firmware nelle regioni flash abilitate per PRINCE di LPC55S69JBD100, gli sviluppatori possono utilizzare strategie di back-off che ripristinano una precedente versione funzionante del firmware se la nuova versione si avvia in uno stato non funzionale.

Poiché tutte queste nuove immagini del firmware devono superare i controlli di verifica della firma richiesti nel processo di avvio sottostante, gli sviluppatori possono sfruttare appieno il FOTA sicuro per aggiungere altre funzionalità o per correggere i bug senza compromettere il sistema o la sua catena di attendibilità.

Conclusione

La sicurezza a livello di sistema e di applicazione richiede un ambiente di esecuzione che permetta solo al software autorizzato di funzionare. Sebbene la verifica della firma in codice sia una caratteristica essenziale per abilitare questo tipo di ambiente, i sistemi sicuri devono attingere a una serie più completa di funzionalità per creare la catena di attendibilità necessaria a garantire l'esecuzione di un software attendibile. La base di questi ambienti di attendibilità risiede in una radice di attendibilità fornita attraverso meccanismi di avvio sicuri supportati da processori sicuri. Utilizzando questa classe di processori, gli sviluppatori possono implementare dispositivi IoT sicuri in grado di resistere agli attacchi destinati a paralizzare l'esecuzione del software in un sistema o a violare completamente il sistema.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.