Soddisfare diversi requisiti funzionali e di sicurezza con i processori multicore

Contributo di Editori nordamericani di DigiKey

2020-10-01

Le applicazioni automotive, industriali, robotiche, di controllo degli edifici e altre di tipo critico dei sistemi embedded devono assumersi carichi di lavoro più diversificati che vanno dal monitoraggio in tempo reale a bassa potenza ad applicazioni multimediali di alto livello con display grafici multischermo per interfacce uomo-macchina (HMI). Pur soddisfacendo questi ampi requisiti funzionali, devono anche essere in grado di supportare rigorosi standard di sicurezza, costi e ingombri inferiori e ottimizzare il rapporto potenza/prestazioni.

Per soddisfare questi requisiti, spesso conflittuali, finora gli sviluppatori sono stati costretti a sacrificare le capacità funzionali o a complicare la progettazione e la produzione con l'aggiunta di dispositivi necessari a supportare requisiti specifici per la grafica, la sicurezza e la protezione. Ciò di cui gli sviluppatori hanno realmente bisogno è un'unica soluzione in grado di supportare un'ampia gamma di prodotti che soddisfino questi requisiti in molte applicazioni critiche di sistemi embedded.

Questo articolo descrive brevemente l'evoluzione della progettazione di sistemi embedded critici. Mostrerà quindi come i processori per applicazioni multicore - progettati specificamente da NXP Semiconductors per supportare una serie in rapida espansione di requisiti sia per ampie funzionalità sia per capacità di sicurezza certificabili - possano essere utilizzati per affrontare le sfide degli sviluppatori.

L'evoluzione delle considerazioni sulla progettazione di sistemi embedded

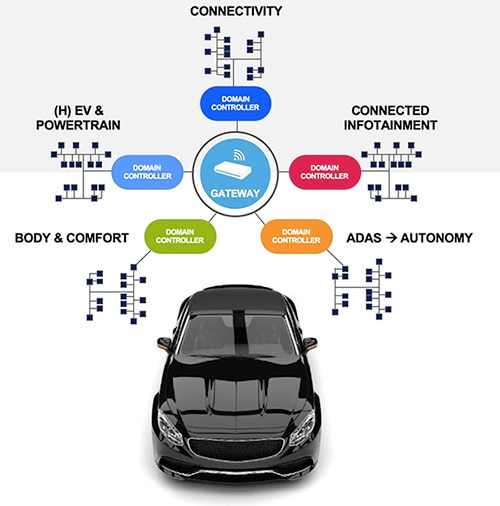

Il ruolo tradizionale dei dispositivi embedded nel supportare un insieme limitato di funzioni di sistema è stato ampiamente sostituito dalla domanda di dispositivi che forniscono ampie capacità. Nelle applicazioni industriali, ad esempio, la necessità di migliorare le capacità HMI in strumenti e apparecchiature intelligenti richiede processori in grado di fornire una grafica ottimizzata e al tempo stesso di soddisfare i requisiti industriali più tradizionali in tempo reale. Allo stesso modo, la tendenza delle applicazioni automotive verso architetture gerarchiche che comprendono cluster di dominio funzionale e gateway determina la necessità di processori in grado di soddisfare pienamente tali requisiti (Figura 1).

Figura 1: La tendenza verso architetture di sistemi automotive più gerarchiche ha creato la necessità di soluzioni di processore più integrate e scalabili. (Immagine per gentile concessione di NXP Semiconductors)

Figura 1: La tendenza verso architetture di sistemi automotive più gerarchiche ha creato la necessità di soluzioni di processore più integrate e scalabili. (Immagine per gentile concessione di NXP Semiconductors)

All'interno di ogni dominio funzionale, la richiesta di capacità più sofisticate continua ad alzare la soglia delle prestazioni e delle capacità integrate. Ad esempio, l'emergere dei visori a sovrimpressione richiede soluzioni in grado di garantire la fornitura continua di informazioni grafiche vitali ai conducenti. Insieme a questi display di nuova generazione, la crescente necessità di una maggiore consapevolezza del conducente aggiunge ulteriori requisiti per le interfacce delle telecamere e l'esecuzione ad alte prestazioni di un software di riconoscimento avanzato in grado di rilevare la sonnolenza.

Mentre le applicazioni continuano ad evolversi, diventa sempre più urgente trovare soluzioni altamente integrate e scalabili per soddisfare requisiti sempre più diversificati, riducendo al minimo l'ingombro, i costi e la complessità della progettazione. Utilizzando la famiglia di processori per applicazioni i.MX 8 di NXP, gli sviluppatori possono sfruttare una piattaforma di processori compatibile con la gamma di capacità e prestazioni necessarie per supportare un'ampia gamma di requisiti applicativi. All'interno della famiglia i.MX 8, la serie i.MX 8X di NXP risponde alle esigenze emergenti di processori di sicurezza certificabili richiesti nelle applicazioni automotive e industriali di fascia media.

L'architettura multicore gestisce diversi carichi di lavoro

Una delle difficoltà che gli sviluppatori incontrano nell'implementazione di dispositivi per applicazioni automotive e industriali è la vastità dei requisiti. Laddove gli sviluppatori potevano aspettarsi di dover gestire carichi di lavoro di elaborazione applicativa in tempo reale o di alto livello, la richiesta di sottosistemi intelligenti ha unito queste tipologie di calcolo molto diverse tra loro. Sempre più spesso gli sviluppatori hanno bisogno di soluzioni in grado di fornire sia una risposta affidabile in tempo reale sia un'esecuzione delle applicazioni ad alte prestazioni, supportando al contempo i requisiti di sicurezza funzionale.

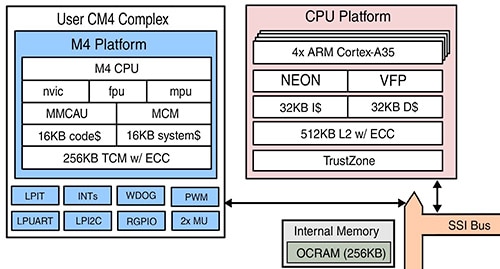

Progettati per fornire capacità in tempo reale, elaborazione ad alte prestazioni e basso consumo energetico, i processori serie i.MX 8X di NXP sfruttano al massimo i vantaggi di una sofisticata architettura di unità di elaborazione centrale (CPU) multicore per gestire diversi carichi di lavoro computazionali (Figura 2).

Figura 2: La serie i.MX 8X di NXP utilizza un'architettura multicore che comprende un processore embedded Arm Cortex-M4 (CM4) e molteplici processori per applicazioni Arm Cortex-A35 per supportare carichi di lavoro software misti. (Immagine per gentile concessione di NXP Semiconductors)

Figura 2: La serie i.MX 8X di NXP utilizza un'architettura multicore che comprende un processore embedded Arm Cortex-M4 (CM4) e molteplici processori per applicazioni Arm Cortex-A35 per supportare carichi di lavoro software misti. (Immagine per gentile concessione di NXP Semiconductors)

Per compiti generali di elaborazione in tempo reale, i dispositivi i.MX 8X includono un processore Arm Cortex-M4 (CM4) con unità a virgola mobile (FPU), unità di protezione di memoria (MPU), unità di accelerazione crittografica con mappatura in memoria (MMCAU) e modulo di controllo vari (MCM). Per supportare periferiche esterne come sensori e attuatori, questo complesso CM4 utente combina un controller di interrupt a vettorizzazione annidata (NVIC) con un set completo di interfacce e moduli, incluso il timer di interrupt periodico a bassa potenza (LPIT), la modulazione della larghezza di impulso (PWM) e altre funzioni comunemente richieste nelle applicazioni automotive e industriali. Una coppia di memorie cache e memoria strettamente accoppiata (TCM) con capacità di correzione errori (ECC) aiuta a ridurre al minimo l'accesso alla memoria esterna, la velocità di esecuzione e la gestione degli errori di memoria.

Per una rapida esecuzione dei carichi di lavoro delle applicazioni, la piattaforma CPU comprende più processori per applicazioni (AP) Arm Cortex-A35 ad alta efficienza energetica - due AP in processori 8DualXPlus come MIMX8UX6AVLFZAC e quattro AP in processori 8QuadXPlus come MIMX8QX6AVLFZAC. Insieme alla cache dedicata alle istruzioni (I$) e ai dati (D$), la piattaforma CPU include una cache condivisa di 512 kB livello 2 (L2) con ECC.

I core Arm Cortex-A35 dell'architettura forniscono sia la compatibilità software sia la scalabilità delle prestazioni, supportando la retrocompatibilità a 32 bit e prestazioni a 64 bit. Per velocizzare ulteriormente l'esecuzione di algoritmi ad alta intensità di calcolo come l'elaborazione dei segnali e l'apprendimento automatico, i processori Arm Cortex-A35 forniscono l'elaborazione a virgola mobile vettoriale (VFP) e le estensioni dell'architettura Arm Neon SIMD (istruzione singola, dati multipli). Per accelerare l'esecuzione di software per l'elaborazione delle immagini, la visione artificiale e l'apprendimento automatico, la libreria Arm Compute Library offre funzioni ottimizzate per le architetture di processore Arm e dell'unità di elaborazione grafica (GPU) e la libreria open-source Ne10 C fornisce funzioni ottimizzate per Arm per le operazioni ad alta intensità di calcolo.

I motori dedicati alleviano il carico dalle CPU primarie

Oltre al complesso CM4 utente e alla piattaforma CPU multicore Arm Cortex-A35, l'architettura fornisce ulteriori motori dedicati per applicazioni multimediali. Insieme a un processore di segnali digitali (DSP) per l'elaborazione di codec audio e vocali, l'architettura integra sia una GPU che un'unità di elaborazione video (VPU). La GPU del dispositivo supporta librerie grafiche standard, accelerando le operazioni mediante quattro vettori in virgola mobile a quattro componenti separati (vec4) con 16 unità di esecuzione e un motore bit blit bidimensionale ad alte prestazioni. La VPU gestisce i formati video più diffusi, accelerando la decodifica fino a 4Kp30 (progressiva, 30 Hz) e la codifica fino a 1080p30. A sua volta, il blocco del controller display dedicato del chip può comandare l'uscita grafica per un massimo di tre display indipendenti.

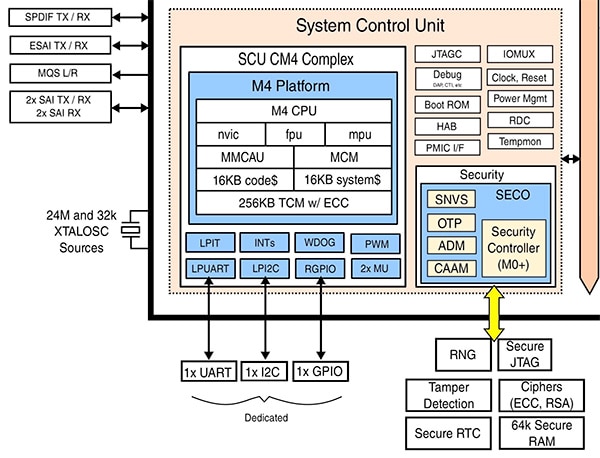

Per massimizzare ulteriormente le prestazioni, l'architettura i.MX 8X integra anche core di processore aggiuntivi progettati per alleviare le piattaforme di CPU primarie dal carico di elaborazione aggiuntivo tipicamente sostenuto nell'esecuzione dei servizi di gestione del sistema e di sicurezza. Per la gestione del sistema, l'unità di controllo del sistema (SCU) dell'architettura integra un complesso CM4 che corrisponde al complesso CM4 utente ma rimane completamente dedicato alle operazioni SCU e non è disponibile per l'uso da parte degli sviluppatori (Figura 3).

Figura 3: Integrata nei processori i.MX 8X di NXP e non disponibile per gli sviluppatori, la SCU utilizza un sottosistema dedicato Arm Cortex-M4 (CM4) per alleviare i processori principali del dispositivo dai compiti di gestione del sistema. (Immagine per gentile concessione di NXP Semiconductors)

Figura 3: Integrata nei processori i.MX 8X di NXP e non disponibile per gli sviluppatori, la SCU utilizza un sottosistema dedicato Arm Cortex-M4 (CM4) per alleviare i processori principali del dispositivo dai compiti di gestione del sistema. (Immagine per gentile concessione di NXP Semiconductors)

Oltre a gestire l'alimentazione, il clocking e altre funzioni interne, la SCU controlla il multiplexing dei pin e la forza di azionamento del canale di ingresso/uscita (I/O) nel funzionamento normale. Infatti, il complesso CM4 utente e gli AP Arm Cortex-A35 non possono accedere direttamente a queste capacità hardware di basso livello. Invece, la SCU serve ad astrarre queste capacità, quindi il software in esecuzione sul CM4 utente o sugli AP deve semplicemente chiamare le funzioni dell'interfaccia di programmazione di applicazioni (API) del firmware della SCU per eseguire funzioni come lo spegnimento dei domini di alimentazione non necessari. Se quel dominio di alimentazione viene condiviso con un altro processore, ad esempio, la SCU si limita a riconoscere la richiesta, ma mantiene alimentato il dominio fino a quando anche l'altro processore non genera una richiesta di spegnimento.

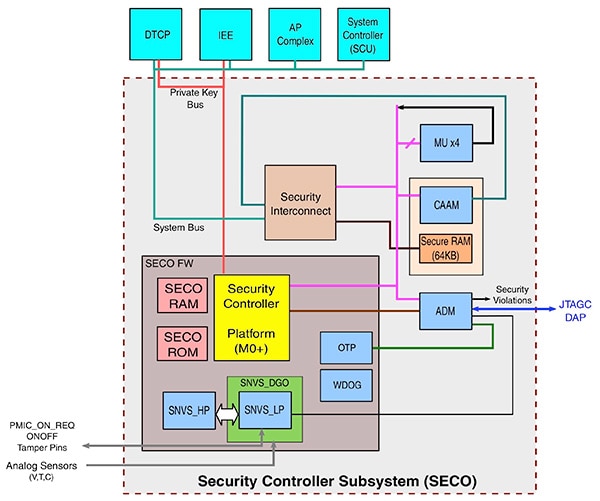

Per gestire l'ampio supporto di sicurezza del dispositivo i.MX 8X, un altro processore dedicato entra in gioco nel sottosistema del controller di sicurezza del dispositivo (SECO). All'interno del sottosistema SECO, un processore a bassa potenza integrato Arm Cortex-M0+ esegue un firmware che supporta funzionalità di sicurezza basate sull'hardware, tra cui l'accesso al bus privato per chiavi sicure, memoria programmabile una sola volta (OTP) per per la memorizzazione sicura delle chiavi e una memoria non volatile sicura (SNVS) per ulteriori dati privati o chiavi effimere (Figura 4).

Figura 4: All'interno del sottosistema del controller di sicurezza (SECO) i.MX 8X di NXP, un processore dedicato a bassa potenza Arm Cortex-M0+ gestisce le operazioni di sicurezza, attingendo da un bus a chiave privata e da più moduli hardware per la memorizzazione sicura, l'accelerazione della crittografia e l'accesso al debug autenticato. (Immagine per gentile concessione di NXP Semiconductors)

Figura 4: All'interno del sottosistema del controller di sicurezza (SECO) i.MX 8X di NXP, un processore dedicato a bassa potenza Arm Cortex-M0+ gestisce le operazioni di sicurezza, attingendo da un bus a chiave privata e da più moduli hardware per la memorizzazione sicura, l'accelerazione della crittografia e l'accesso al debug autenticato. (Immagine per gentile concessione di NXP Semiconductors)

Oltre a questi meccanismi di sicurezza fondamentali, il sottosistema SECO coordina le operazioni di sicurezza per il rilevamento delle manomissioni e il debug sicuro mediato attraverso il modulo di debug autenticato (ADM). Per l'esecuzione sicura, il modulo di accelerazione crittografica e di sicurezza (CAAM) supporta una suite completa di algoritmi di sicurezza che includono la crittografia simmetrica e asimmetrica, funzioni hash e un generatore di numeri casuali (RNG).

Nel funzionamento normale, le unità di elaborazione dei dispositivi, tra cui la SCU, gli AP e l'acceleratore DTCP (protezione di contenuti per trasporto digitale) utilizzano l'interconnessione di sicurezza SECO per accedere alle funzionalità CAAM attraverso il bus di sistema. Oltre all'accesso tramite la funzionalità di accesso diretto alla memoria CAAM (DMA), il processore dedicato Cortex-M0+ del SECO non può accedere al bus di sistema. Utilizza invece connessioni interne protette per accedere alle periferiche, alla memoria ad accesso casuale (RAM) sicura, alla memoria di sola lettura (ROM) e al suo speciale bus a chiave privata.

Insieme all'uso dell'acceleratore DTCP, questo bus a chiave privata svolge un ruolo centrale nel supporto del processore i.MX 8X per la cifratura e la decifratura al volo. Qui, il processore di sicurezza usa le sue risorse per fornire le chiavi private necessarie al modulo IEE (motore in linea di crittografia/decrittografia) del dispositivo mentre legge o scrive in modo sicuro dalla memoria criptata, senza il coinvolgimento del processore richiedente, del controller DMA o del dispositivo I/O.

Basandosi sulla tecnologia TrustZone di Arm integrata nei processori Cortex-A35 del dispositivo, il sottosistema SECO lavora anche con la SCU durante il processo di avvio sicuro. In questo processo, la SCU interpreta le impostazioni di avvio, configura le sorgenti di avvio e carica le immagini di avvio nella memoria interna o esterna. A sua volta, il sottosistema SECO utilizza le sue funzioni di crittografia per autenticare le immagini firmate del firmware dopo averle caricate ma prima di eseguirle.

Salvaguardia dei display critici e delle funzionalità di controllo

Se la capacità di elaborare diversi carichi di lavoro in modo efficiente e sicuro è importante, per le applicazioni mission-critical nei segmenti automotive e industriale, salvaguardare le capacità chiave è altrettanto vitale. La famiglia i.MX 8X di NXP combina le capacità di elaborazione alle capacità di sicurezza certificabili richieste per soddisfare questi requisiti critici.

Il supporto della sicurezza nella famiglia di processori è integrato a diversi livelli, a partire dalla fabbricazione con tecnologia di processo FD-SOI (silicio su isolante completamente esaurito) che migliora l'affidabilità del sistema. Poiché la sicurezza del sistema dipende da una solida base di sicurezza, la combinazione di AP abilitati da TrustZone, del sottosistema SECO e delle capacità di avvio sicuro può costituire il tipo di ambiente affidabile necessario per contrastare le minacce alla sicurezza e alla protezione.

Al tempo stesso, la capacità di gestire in modo indipendente le attività critiche in termini di tempo con il complesso CM4 utente e di scaricare le attività critiche del sistema alla SCU e ai sottosistemi SECO aiuta a garantire che le capacità delle applicazioni mission-critical rimangano disponibili nonostante il diverso carico di elaborazione. Infatti, NXP estende questo concetto al supporto per i display mission-critical attraverso la tecnologia SafeAssure, che integra un percorso di failover del display hardware predisposto per il livello B di integrità per la sicurezza automotive (ASIL B) per dispositivi i.MX 8X. Con SafeAssure, agli utenti viene fornita automaticamente un'immagine di failover se il dispositivo rileva un errore nell'integrità dei dati o della GPU. Eseguita in background, questa immagine di failover assicura che le informazioni critiche siano sempre disponibili anche durante il guasto del display primario.

Il supporto per le applicazioni di sicurezza si estende all'accesso alla memoria nei sistemi basati su i.MX 8X. Tra le interfacce di memoria supportate, i dispositivi i.MX 8X forniscono un ECC a 8 bit per la memoria a bassa tensione a doppia velocità 3 bassa tensione (DDR3L). Insieme all'ECC nella cache L2 (vedere di nuovo la Figura 2), questa capacità ECC DDR3L supporta il livello di integrità di sicurezza industriale 3 (SIL 3). L'architettura i.MX 8X estende il supporto ECC anche ai dispositivi di memorizzazione flash esterni. Qui, un modulo integrato encoder/decoder Bose, Ray-Chaudhuri, Hocquenghem (BCH) fornisce un ECC a 62 bit in grado di correggere da 2 a 20 errori a singolo bit all'interno di un blocco di dati letti da questi dispositivi di memorizzazione.

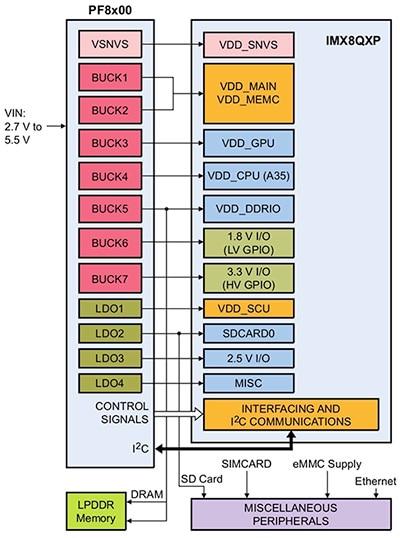

Presentazione delle applicazioni basate su i.MX 8X

Come per qualsiasi processore di questa classe, l'implementazione di un progetto basato su i.MX 8X richiede molta attenzione ai rigorosi requisiti di alimentazione, comprese le sequenze di accensione critiche. I dispositivi i.MX 8X richiedono l'alimentazione in sequenza o contemporaneamente a quattro diversi gruppi, iniziando dal sottosistema SVNS e poi passando alla SCU, agli I/O e alle interfacce di memoria e solo per ultimo al resto del dispositivo. Gli sviluppatori possono soddisfare questo requisito semplicemente utilizzando i dispositivi per circuito integrato di gestione della potenza (PMIC) PF8x00 di NXP, che forniscono una serie completa di rail di tensione e segnali di controllo necessari per supportare i processori i.MX 8X, nonché la memoria esterna e le tipiche periferiche di sistema (Figura 5).

Figura 5: I PMIC PF8x00 di NXP forniscono un set completo di rail di tensione e segnali di controllo necessari per alimentare i processori i.MX 8X. (Immagine per gentile concessione di NXP Semiconductors)

Figura 5: I PMIC PF8x00 di NXP forniscono un set completo di rail di tensione e segnali di controllo necessari per alimentare i processori i.MX 8X. (Immagine per gentile concessione di NXP Semiconductors)

Nell'implementazione di progetti basati su i.MX 8X, gli sviluppatori possono utilizzare il PMIC MC33PF8100CCES di NXP, preprogrammato per l'uso con i processori 8QuadXPlus come MIMX8QX6AVLFZAC. Altre varianti PF8x00 come MC33PF8100A0ES e MC33PF8200A0ES supportano i processori i.MX 8X ma non sono preprogrammati.

Per le applicazioni di sicurezza, i dispositivi serie PF8200 come MC33PF8200A0ES integrano funzionalità progettate per supportare i sistemi ASIL B. Insieme a più monitor interni, compreso un monitor della tensione di uscita con un riferimento di bandgap dedicato, i PMIC PF8200 includono un pin di uscita a sicurezza intrinseca (FSOB) progettato per mantenere il sistema in uno stato di sicurezza durante l'accensione o durante un evento di interruzione di corrente. Inoltre, una routine analogica integrata di auto-test (ABIST) verifica tutti i monitor di tensione, mentre una routine di autotest verifica le altre funzionalità del dispositivo.

Sebbene i PMIC PF8x00 possano semplificare la progettazione hardware dei sistemi basati su i.MX 8X, alcuni sviluppatori potrebbero dover iniziare subito a valutare i dispositivi i.MX 8X e a prototipare rapidamente le applicazioni basate su i.MX 8X. Il kit di abilitazione multisensoriale (MEK) i.MX 8X MCIMX8QXP-CPU di NXP fornisce una piattaforma di sviluppo pronta all'uso che combina un processore i.MX 8QuadXPlus, PMIC F8100, 3 GB di RAM, 32 GB di memoria integrata eMMC e 64 MB di memoria flash. Insieme alle interfacce per display, telecamera e audio, la scheda MEK comprende una serie di sensori tipicamente utilizzati in applicazioni automotive o industriali. Per ulteriori opzioni di connettività, audio e di espansione, gli sviluppatori possono anche aggiungere la scheda base opzionale MCIMX8-8X-BB di NXP.

Conclusione

Per un numero crescente di applicazioni nei settori automotive, industriale, di controllo degli edifici e HMI, i carichi di lavoro di elaborazione si sono ampliati fino a comprendere sia la tradizionale elaborazione di I/O in tempo reale sia l'elaborazione emergente a livello di applicazione con grafica multimediale. Sebbene esistano opzioni di progettazione per ogni tipo di carico di lavoro, poche soluzioni disponibili soddisfano la crescente necessità di soluzioni ad alte prestazioni e ad alta efficienza energetica in grado di rispondere ai requisiti di progetti certificabili per la sicurezza nelle applicazioni automotive e industriali.

Come mostrato, utilizzando una famiglia di processori multicore di NXP Semiconductors, gli sviluppatori possono implementare in modo più efficace progetti in grado di soddisfare questi diversi requisiti e scalarli facilmente per rispondere alle esigenze emergenti in fatto di alte prestazioni.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.