Sfruttate i vantaggi dell'I3C per una comunicazione tra CI più veloce, più semplice e più flessibile

Contributo di Editori nordamericani di DigiKey

2024-12-17

Le interfacce seriali su scheda per le comunicazioni tra circuiti integrati (CI) sono dominate dal circuito inter-integrato (I²C) e dall'interfaccia periferica seriale (SPI), presenti dagli anni '80. Queste interfacce sono ampiamente utilizzate per collegare sensori e CI a bassa velocità a unità microcontroller (MCU) per la comunicazione all'interno della scheda su brevi distanze. Tuttavia, con l'aumento della velocità dei sistemi digitali, queste interfacce, limitate a velocità di trasmissione dati tipiche di 1 Mbps per I²C e 10 Mbps per SPI, sono diventate un fattore limitante. Altre limitazioni, tra cui le linee di interrupt o di abilitazione del chip dedicate, richiedono connessioni di segnale aggiuntive, aumentando il numero di fili e la complessità delle connessioni del bus.

Il bus di circuito inter-integrato migliorato (I3C) è destinato a migliorare le comunicazioni inter-CI. Offre velocità di trasmissione dati più elevate, maggiore flessibilità e una vera interfaccia a due fili con interrupt in banda (IBI) anziché esterni.

Questo articolo illustra le caratteristiche dell'interfaccia I3C e i motivi per cui potrebbe essere un buon aggiornamento rispetto alle interfacce seriali I²C e SPI. Per mostrarne l'applicazione verranno utilizzati tipici dispositivi MCU, switch in CI e sensori.

Bus di comunicazione integrati

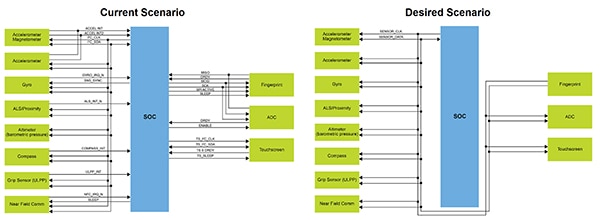

Le interconnessioni seriali integrate come I²C e SPI sono state utilizzate per molti anni per le comunicazioni all'interno della scheda. Sono utilizzate principalmente come bus di comunicazione tra i sensori e i dispositivi di interfaccia utente e i relativi processori di controllo. Il numero di sensori nei sistemi tipici è cresciuto fino a dieci o venti in un telefonino e molto di più nei veicoli. Allo stesso tempo, i requisiti di comunicazione sono diventati più impegnativi per i progettisti, di pari passo all'aumento della richiesta di maggiore velocità, ridotto consumo energetico e minor numero di conduttori. I progettisti devono soddisfare queste esigenze mantenendo il controllo del processore tramite linee di interrupt e abilitazione (Figura 1).

Figura 1: Le comunicazioni integrate devono supportare velocità più elevate, consumi ridotti e un numero minimo di fili. (Immagine per gentile concessione di NXP Semiconductors)

Figura 1: Le comunicazioni integrate devono supportare velocità più elevate, consumi ridotti e un numero minimo di fili. (Immagine per gentile concessione di NXP Semiconductors)

La tecnologia attuale implementa l'interfaccia del sensore e del dispositivo di controllo utente utilizzando interfacce I²C a due fili o SPI a quattro fili. Le linee di interrupt, abilitazione e altre linee di controllo sono separate dalle linee di clock e di dati, con un conseguente numero maggiore di linee per interfaccia.

I progettisti hanno bisogno di un approccio all'interfaccia più lungimirante, che elimini questi conduttori extra dalle interconnessioni e gestisca queste operazioni in banda utilizzando solo le linee di clock e di dati. Inoltre, il bus dovrebbe essere in grado di funzionare a velocità più elevate e con minori perdite di potenza.

Interfaccia I3C

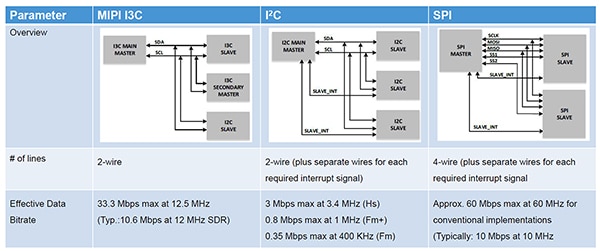

L'I3C è stato sviluppato dalla Mobile Industry Processor Interface (MIPI) Alliance per soddisfare questi requisiti. L'interfaccia è disponibile sia come MIPI I3C per i membri MIPI, sia come MIPI I3C Basic con funzionalità ridotte per i non membri. Come le interfacce I²C e SPI tradizionali, la forma migliorata è seriale e viene implementata utilizzando due fili per ridurre al minimo il numero di pin e il numero di percorsi di segnale tra i componenti. Ha una velocità di trasmissione dati fino a 12,5 Mbps con un clock di 12,5 MHz in modalità a velocità dati singola (SDR). Funziona a livelli di potenza ridotti e utilizza un'architettura di progettazione semplice e flessibile.

In particolare, lo standard I3C mantiene una limitata retrocompatibilità con il sistema I²C, consentendo di collegare al bus I3C i dispositivi I²C esistenti e permettendo al contempo al bus di passare a velocità di dati più elevate per la comunicazione tra dispositivi I3C conformi. La Figura 2 mostra un confronto tra le configurazioni di sistema.

Figura 2: Il confronto tra le configurazioni di base delle interfacce I3C, I²C e SPI mostra la maggiore velocità e la semplicità di cablaggio dell'I3C. (Immagine per gentile concessione di NXP Semiconductors)

Figura 2: Il confronto tra le configurazioni di base delle interfacce I3C, I²C e SPI mostra la maggiore velocità e la semplicità di cablaggio dell'I3C. (Immagine per gentile concessione di NXP Semiconductors)

L'interfaccia SPI a quattro fili può funzionare più velocemente e supporta la comunicazione full-duplex. I²C comunica in half-duplex su un bus a due fili composto da linee di clock (SCL) e dati (SDA). Entrambe richiedono linee aggiuntive per supportare gli interrupt e altre funzioni di controllo come chip-select. I3C riduce a due il numero di fili utilizzati nell'interfaccia, eliminando le linee separate di interrupt, abilitazione e chip-select utilizzate in I²C e SPI. Questa riduzione del numero di fili è un vantaggio significativo in un sistema che richiede dieci o venti sensori singoli collegati al processore, ciascuno con diversi fili secondari. Le linee di interrupt e altre linee di controllo sono sostituite dagli IBI. In questo metodo, un sensore o un dispositivo di destinazione impone il proprio indirizzo nell'intestazione dell'indirizzo del bus I3C per notificare al processore un interrupt.

La differenza di frequenze di clock tra I²C e I3C è significativa. I²C funziona generalmente a 100 kHz, 400 kHz o 1 MHz, mentre l'I3C può funzionare a 12,5 MHz. In precedenza, l'SPI veniva utilizzato per frequenze di clock superiori a 1 MHz. Il compromesso progettuale era tra la frequenza di clock e il numero di fili. I3C ha cambiato questa situazione offrendo frequenze di clock e velocità dati più elevate, utilizzando una vera topologia a due fili.

Le uscite push-pull, che possono commutare più velocemente rispetto ai driver a drain aperto o a collettore, contribuiscono in modo significativo all'aumento della frequenza di clock dell'I3C. Per mantenere la compatibilità con i dispositivi I²C, I3C può passare da driver a drain aperto a push-pull a seconda dello stato del bus. Il design a drain aperto o a collettore viene utilizzato durante l'indirizzamento iniziale o l'arbitrato, quando entrambi i dispositivi I²C e I3C possono essere sulla linea contemporaneamente. I3C utilizza il push-pull quando la comunicazione è unidirezionale e non c'è la possibilità che un dispositivo I²C comunichi contemporaneamente.

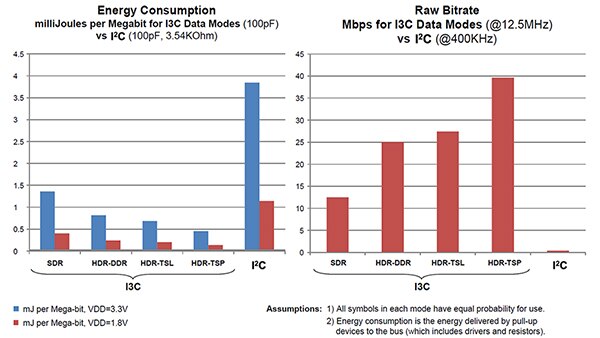

Oltre all'SDR standard, I3C supporta diverse modalità opzionali ad alta velocità di trasmissione dei dati (HDR). Queste modalità HDR funzionano con la stessa frequenza di clock, ma trasmettono con una densità di dati più elevata. La prima delle modalità HDR è HDR a velocità dati doppia (HDR-DDR), in cui i dati viaggiano su entrambi i fronti del segnale di clock, fornendo quasi due volte la velocità di trasmissione dei dati. Per un clock di 12,5 MHz, la modalità DDR raggiunge una velocità di trasmissione dati effettiva di 20 Mbps.

I simboli ternari HDR hanno due versioni: simbolo ternario HDR puro (HDR-TSP) per i soli dispositivi I3C e simbolo ternario HDR legacy (HDR-TSL) per i bus che includono sia dispositivi I²C sia I3C. Le modalità a simboli ternari consentono di ottenere tre bit di dati per clock utilizzando simboli a tre bit (ternari) codificati sulle linee SCL e SDA.

La modalità HDR a trasporto di massa (HDR-BT) offre i dati più elevati supportando le comunicazioni su linee dati SDA quadruple, doppie o singole. In questo modo si ottengono prestazioni otto, quattro o due volte superiori alla velocità di trasmissione dei dati singoli a parità di frequenza di clock.

Questi aumenti della velocità dati consentono di accendere i dispositivi per un periodo più breve, riducendo il ciclo di lavoro dell'alimentazione del bus. Ciò riduce il consumo energetico rispetto a I²C (Figura 3). Il passaggio da driver a collettore aperto con resistori pull-up esterni a driver push-pull riduce ulteriormente il consumo energetico, poiché i resistori pull-up richiedono una potenza significativa per funzionare.

Figura 3: I3C offre miglioramenti nella velocità dati e nel consumo energetico rispetto a I²C. (Immagine per gentile concessione di NXP Semiconductors)

Figura 3: I3C offre miglioramenti nella velocità dati e nel consumo energetico rispetto a I²C. (Immagine per gentile concessione di NXP Semiconductors)

Indirizzamento

I²C utilizza indirizzi statici di lunghezza pari a 7 o 10 bit per ciascun dispositivo del bus. I3C utilizza un indirizzamento dinamico a 7 bit, in cui il master del bus imposta l'indirizzo del dispositivo durante l'assegnazione dinamica dell'indirizzo (DAA) e lo memorizza in un registro del dispositivo. L'indirizzamento statico, come nel caso di una periferica I²C, può ancora essere utilizzato in I3C.

Grazie all'indirizzamento dinamico, gli indirizzi dei dispositivi possono essere modificati in seguito. Questo supporta l'inclusione a caldo, che consente di aggiungere un nuovo dispositivo al bus mentre questo è in funzione. Il nuovo dispositivo, collegato al bus I3C, segnala la sua presenza al master I3C inviando una richiesta di inclusione a caldo. Il controller master conferma la richiesta e assegna un indirizzo per aggiungere il dispositivo al bus.

IBI

I3C è un vero bus a due fili che utilizza gli IBI invece di linee di interrupt dedicate come I²C. Gli IBI si verificano quando un dispositivo di destinazione segnala la propria disponibilità al master abbassando la linea SDA. Il master avvia quindi il clock sulla linea SCL e il dispositivo di destinazione trasmette il proprio indirizzo sul bus I3C per notificare al controller un interrupt.

Codici di comando comuni

I codici di comando comuni (CCC) sono comandi standardizzati che il controller può trasmettere come trasmissione generale a tutti i dispositivi I3C contemporaneamente o a un dispositivo di destinazione specifico. Questi comandi riguardano le voci relative alla gestione del bus. Il formato del protocollo CCC inizia con l'indirizzo di trasmissione I3C, riconosciuto da tutti i dispositivi I3C sul bus. Qualsiasi dispositivo I²C sul bus non riconoscerà la richiesta, poiché si tratta di un indirizzo I²C riservato.

Ogni comando comprende un campo ID descrittore di 8 bit e può essere seguito da un carico utile di comando. Un comando inviato a un dispositivo specifico passa l'indirizzo del dispositivo nel primo byte del carico utile. Ci sono più di quaranta comandi CCC, tra cui:

- Inserisci assegnazione dinamica dell'indirizzo (ENTDAA)

- Imposta assegnazione nuovo indirizzo dinamico (SETNEWDA)

- Abilita eventi (ENEC)/Disabilita eventi (DISEC)

- Azzera assegnazione dinamica degli indirizzi (RSTDAA)

- Passa alla modalità Alta velocità dati (ENTHDRx)

- Carica registro delle caratteristiche dispositivo (GETDCR)

I fornitori hanno a disposizione una gamma dedicata di ID CCC per implementare i propri comandi.

Rilevamento e recupero degli errori

A differenza di I²C, I3C include disposizioni per il rilevamento e il recupero degli errori. Sono obbligatori sei metodi di errore e di recupero per i dispositivi di destinazione, mentre un altro è opzionale. Sono inoltre disponibili ulteriori metodi di errore e di recupero specifici per gli errori sul lato master.

Componenti supportati da I3C

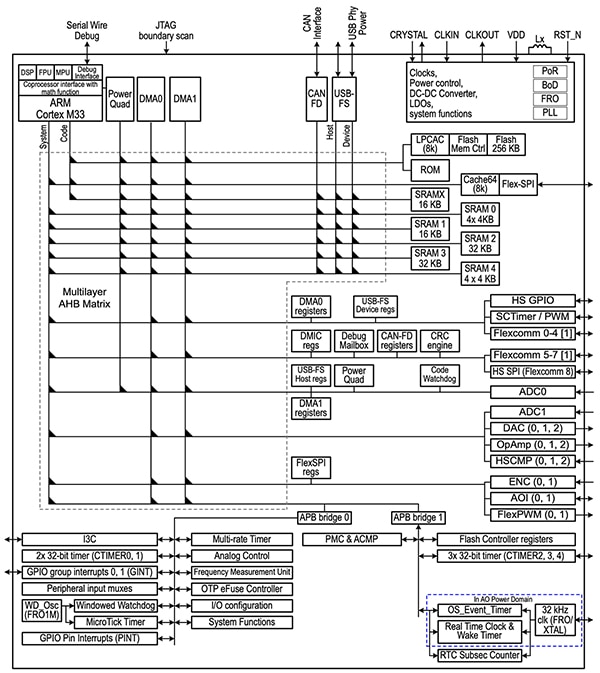

Come mostrato nella Figura 2 (a sinistra), una rete I3C di base comprende almeno un controller master e uno o più dispositivi di destinazione I3C o slave. Il master principale può essere un MCU come il modello LPC5534JHI48-00MP di NXP Semiconductors (Figura 4). Si tratta di un MCU ARM® Cortex®-M33 a 32 bit con 128 kB di SRAM e 256 kB di Flash. L'interfaccia Flexcomm supporta otto diverse interfacce seriali, tra cui I3C.

Figura 4: L'MCU LPC5534JHI48/00MP comprende un'interfaccia I3C e altre sette interfacce seriali. (Immagine per gentile concessione di NXP Semiconductors)

Figura 4: L'MCU LPC5534JHI48/00MP comprende un'interfaccia I3C e altre sette interfacce seriali. (Immagine per gentile concessione di NXP Semiconductors)

Il bus I3C consente l'aggiunta di master secondari introdotti sul bus come slave. L'I3C può avere più master, ma solo uno può essere il controller. Una volta iscritto, il master secondario può richiedere lo stato di master corrente e, se il master corrente accetta, il suo controllo passa al master secondario richiedente.

Un tipico sensore I3C è il modello P3T2030CUKAZ di NXP. Questo sensore di temperatura converte temperature da -40 °C a +125 °C in un valore digitale a 12 bit con una precisione di ±2 °C. Include un'interfaccia seriale in modalità I²C e I3C SDR.

Un sensore più sofisticato è il giroscopio e accelerometro a tre assi per sistemi microelettromeccanici (MEMS) ICM-42605 di TDK InvenSense. Come giroscopio, misura velocità di rotazione da ±15,2 a ±2000°/s. La sua portata come accelerometro è compresa tra ±2 e ±15 g. Rileva il movimento, l'inclinazione, il tocco o i passi (pedometro). Come sensore I3C, funziona a 12,5 MHz in modalità SDR e a 25 MHz in modalità DDR.

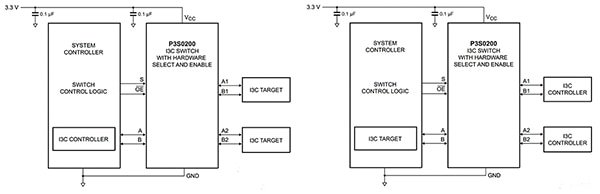

I CI, come lo switch I3C P3S0200GMX di NXP, possono riconfigurare il bus I3C instradando i segnali del bus I3C tra un controller I3C e più gruppi di dispositivi di destinazione, o tra un singolo dispositivo di destinazione e più controller I3C come determinato da un MCU esterno (Figura 5).

Figura 5: Lo switch I3C P3S0200GMX può essere utilizzato per riconfigurare un bus I3C instradando i segnali del bus I3C tra un controller I3C e più serie di dispositivi di destinazione o tra un singolo dispositivo di destinazione e più controller I3C. (Immagine per gentile concessione di NXP Semiconductors)

Figura 5: Lo switch I3C P3S0200GMX può essere utilizzato per riconfigurare un bus I3C instradando i segnali del bus I3C tra un controller I3C e più serie di dispositivi di destinazione o tra un singolo dispositivo di destinazione e più controller I3C. (Immagine per gentile concessione di NXP Semiconductors)

La commutazione tra due dispositivi di destinazione può essere necessaria se entrambi hanno lo stesso indirizzo e non possono risiedere sullo stesso bus. In alternativa, un singolo dispositivo di destinazione potrebbe dover essere condiviso tra due processi, richiedendo uno switch tra i due controller I3C.

Conclusione

I3C è un'interfaccia seriale che estende il bus I²C aumentando la velocità dei dati, riducendo il numero di fili e aggiungendo flessibilità al controllo del bus. Si tratta di un miglioramento che estende l'utilità delle interfacce legacy I²C e SPI.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.