Comprendere e ridurre al minimo l'impatto del jitter sui circuiti ad alta velocità

Contributo di Editori nordamericani di DigiKey

2023-12-21

Gli oscillatori di clock sono il cuore pulsante dei circuiti moderni e determinano la temporizzazione dei componenti di un sistema. Con l'aumento della velocità dei sistemi oltre le centinaia di megahertz, per assicurare le prestazioni dei sistemi questi clock devono essere più veloci e fornire un jitter molto basso, in genere inferiore a 100 fs. Devono inoltre mantenere le specifiche di basso jitter nel tempo, nonostante le variazioni di temperatura e tensione.

Parte del jitter è indotta dal rumore e dalla distorsione del percorso del segnale e può essere in qualche modo ridotta mediante tecniche di reclocking e ritemporizzazione. Tuttavia, il jitter è generato anche dalla sorgente di clock, che di solito è un oscillatore. Ciò è dovuto a vari fenomeni fisici, tra cui il rumore termico, le imperfezioni del processo, il rumore dell'alimentazione, altri disturbi esterni che entrano nell'oscillatore di clock, le sollecitazioni dei materiali e molti altri fattori. Indipendentemente dalla fonte, spetta al progettista fare tutto il possibile per ridurre al minimo il jitter di clock intrinseco, poiché le conseguenze sono irreversibili.

Questo articolo esamina i problemi di jitter sotto vari punti di vista. Presenta quindi i diversi oscillatori di clock di Abracon LLC e mostra come sia possibile ridurre al minimo il jitter adattando le prestazioni dell'oscillatore di clock all'applicazione.

Principi base del jitter

Il jitter di clock è la deviazione di un fronte di clock dalla sua posizione ideale nel tempo. Questo jitter inficia la precisione temporale e l'accuratezza della trasmissione dei segnali di dati che il segnale di clock sta scandendo, portando a un deterioramento del rapporto segnale/rumore (SNR) nei circuiti di decodifica/demodulazione del ricevitore o in altri CI del sistema. Ciò porta a un tasso di errori di bit (BER) più elevato, un aumento delle ritrasmissioni e una riduzione del throughput effettivo dei dati.

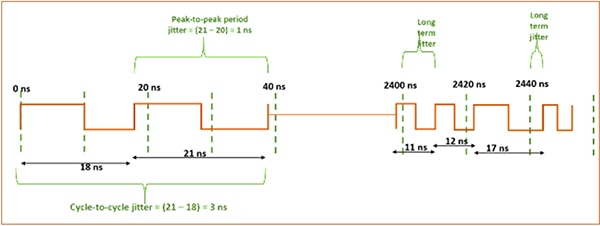

Data la sua criticità, il jitter di clock è ampiamente analizzato nei sistemi che fanno passare un segnale da una fonte trasmittente a un ricevitore attraverso cavi, connettori o schede a circuiti stampati. A seconda dell'applicazione, può essere caratterizzato in molti modi, tra cui ciclo-ciclo, periodo e a lungo termine (Figura 1).

Figura 1: Il termine "jitter" comprende molte variazioni di temporizzazione, tra cui il jitter ciclo-ciclo, il jitter di periodo e il jitter a lungo termine. (Immagine per gentile concessione di VLSI Universe)

Figura 1: Il termine "jitter" comprende molte variazioni di temporizzazione, tra cui il jitter ciclo-ciclo, il jitter di periodo e il jitter a lungo termine. (Immagine per gentile concessione di VLSI Universe)

- Il jitter ciclo-ciclo indica la variazione del periodo di clock tra due cicli consecutivi e non è correlato alla variazione della frequenza nel tempo.

- Il jitter di periodo è la deviazione di un periodo di clock rispetto al suo periodo medio. È la differenza tra i periodi di clock ideali e quelli effettivi e può essere specificata come jitter di periodo al valore quadratico medio (RMS) o jitter di periodo picco-picco.

- Il jitter a lungo termine è la deviazione del fronte di clock dalla sua posizione ideale per un periodo di tempo maggiore. In qualche modo, è analogo alla deriva.

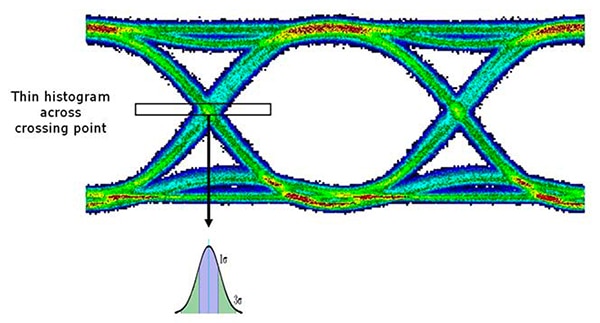

Il jitter può alterare la temporizzazione utilizzata da sottofunzioni, componenti o sistemi utilizzati per il recupero dei dati a basso BER o altri componenti come elementi di memoria o processori in un sistema sincrono. Nel diagramma a occhio della Figura 2 è visibile come l'allargamento del punto di incrocio nella temporizzazione dei bit.

Figura 2: In un diagramma a occhio, il jitter è visibile come l'allargamento del punto critico di incrocio di temporizzazione nel flusso di dati. (Immagine per gentile concessione di Kevin K. Gifford/University of Colorado)

Figura 2: In un diagramma a occhio, il jitter è visibile come l'allargamento del punto critico di incrocio di temporizzazione nel flusso di dati. (Immagine per gentile concessione di Kevin K. Gifford/University of Colorado)

Per i circuiti dati seriali, la circuiteria all'estremità ricevente deve cercare di ristabilire il proprio clock per la decodifica ottimale del flusso di dati. A tale fine, deve sincronizzarsi e riferirsi al clock di origine, spesso utilizzando un circuito ad aggancio di fase (PLL). Il jitter influisce sulla capacità del sistema di eseguire con precisione questa operazione, compromettendo la capacità di recuperare i dati con un basso BER.

Si noti che il jitter può essere misurato sia nel dominio temporale sia in quello della frequenza; entrambi sono prospettive ugualmente valide dello stesso fenomeno. Il rumore di fase è una visione nel dominio della frequenza dello spettro di rumore intorno al segnale dell'oscillatore, mentre il jitter è una misura nel dominio temporale della precisione temporale del periodo di oscillazione.

Le misure del jitter possono essere espresse in diversi modi. Tipicamente viene rappresentato in unità temporali, ad esempio "jitter di 10 ps". Il jitter di fase in valore quadratico medio (RMS) è un parametro del dominio temporale derivato dalla misura del rumore di fase (dominio della frequenza). Il jitter è talvolta indicato anche come jitter di fase, il che può creare confusione, ma si tratta comunque di un parametro di jitter nel dominio temporale.

Via via che le frequenze operative dei circuiti e i relativi clock passano da poche decine di MHz a centinaia di MHz e oltre, il jitter ammissibile sul generatore di clock diminuisce a circa 100 fs o meno. Queste frequenze si applicano a moduli ottici, cloud computing, connettività di rete ed Ethernet ad alta velocità, tutte funzioni e applicazioni che richiedono una frequenza portante compresa tra 100 e 212/215 MHz e velocità di trasmissione dati fino a 400 Gbps.

Gestione del cristallo

Il modo più comune per creare un segnale di clock stabile, coerente e preciso consiste nell'uso di un oscillatore a cristallo di quarzo. Un circuito oscillatore associato supporta il cristallo. Esistono molte famiglie di circuiti di questo tipo, ognuna con vari compromessi. I cristalli sono stati utilizzati in questo ruolo fin dagli anni '30 per le comunicazioni radio wireless nelle bande RF a media frequenza (da 300 kHz a 3 MHz) e ad alta frequenza (da 3 a 30 MHz).

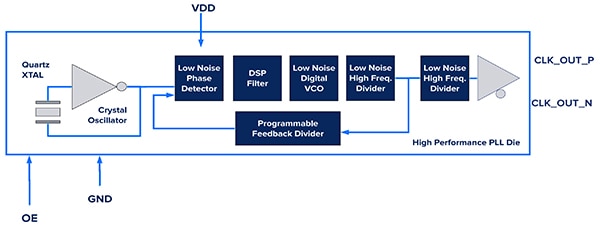

Un approccio ampiamente utilizzato per generare clock a basso jitter è l'uso di una delle numerose varianti di architetture basate su PLL. Ad esempio, i dispositivi delle famiglie AX5 e AX7 ClearClock™ di Abracon sono disponibili rispettivamente in contenitori di 5 × 3,2 mm e 5 × 7 mm e utilizzano una sofisticata tecnologia PLL per prestazioni superiori a basso jitter (Figura 3).

Figura 3: Gli oscillatori di clock AX5 e AX7 di Abracon utilizzano uno dei tanti progetti basati su PLL, ma con lievi miglioramenti per ridurre al minimo il jitter. (Immagine per gentile concessione di Abracon)

Figura 3: Gli oscillatori di clock AX5 e AX7 di Abracon utilizzano uno dei tanti progetti basati su PLL, ma con lievi miglioramenti per ridurre al minimo il jitter. (Immagine per gentile concessione di Abracon)

Oltre alla frequenza operativa e alla progettazione dell'oscillatore, le prestazioni di jitter sono influenzate dalle dimensioni fisiche del cristallo di quarzo nel nucleo dell'oscillatore. Con la riduzione delle dimensioni di questo cristallo, diventa più difficile fornire prestazioni di jitter RMS superiori.

Per le soluzioni di clock nella banda da 100 a 200 MHz e in fattori di forma più piccoli rispetto ai dispositivi AX5 e AX7 basati su PLL, è necessaria una nuova architettura di oscillatori. Questi requisiti di miniaturizzazione sono tipicamente associati ai transceiver e ai moduli ottici di ultima generazione. Esistono quattro modi consolidati per progettare un oscillatore di clock nell'intervallo tra 100 e 200 MHz:

- Utilizzare un oscillatore al quarzo con un cristallo grezzo inverted-mesa come elemento risonatore

- Utilizzare un oscillatore al quarzo con un cristallo grezzo di terza armonica come elemento risonatore

- Utilizzare un circuito oscillatore basato su un cristallo grezzo a terza armonica/fondamentale a meno di 50 MHz o un oscillatore a cristallo termocompensato a meno di 50 MHz accoppiato a un CI PLL in modo intero o frazionario

- Utilizzare un circuito oscillatore basato su un risonatore MEMS (sistema microelettromeccanico) a meno di 50 MHz, accoppiato con un CI PLL in modo intero o frazionario

L'opzione 1 non offre le migliori prestazioni di jitter RMS e non è la soluzione più economicamente vantaggiosa. L'opzione 3 è complicata e non offre ottime prestazioni, mentre l'approccio con risonatore MEMS dell'opzione 4 non soddisfa i criteri prestazionali primari di 200 fs di jitter RMS massimo. L'opzione 2, invece, utilizza un cristallo grezzo a terza armonica progettato in modo ottimale, tenendo conto della geometria degli elettrodi e dell'ottimizzazione dell'angolo di taglio. Questa combinazione è ottimale in termini di costi, prestazioni e dimensioni.

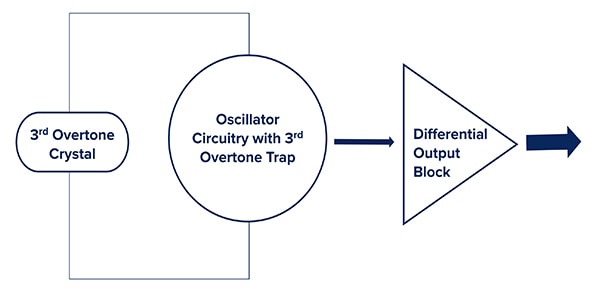

Con questo approccio, Abracon ha sviluppato soluzioni ClearClock "a terza armonica" (Figura 4). Questi dispositivi utilizzano un'architettura più silenziosa per offrire prestazioni superiori a bassissimo jitter RMS ed estrema efficienza energetica in contenitori miniaturizzati di soli 2,5 × 2,0 x 1,0 mm.

Figura 4: La soluzione ClearClock "a terza armonica" di Abracon utilizza un'architettura più silenziosa per migliorare le prestazioni complessive e l'efficienza energetica. (Immagine per gentile concessione di Abracon)

Figura 4: La soluzione ClearClock "a terza armonica" di Abracon utilizza un'architettura più silenziosa per migliorare le prestazioni complessive e l'efficienza energetica. (Immagine per gentile concessione di Abracon)

In questo schema, l'attenta progettazione del cristallo grezzo di terza armonica, insieme all'appropriato filtraggio e "intrappolamento" del segnale portante desiderato, garantisce prestazioni eccezionali di jitter RMS alle frequenze portanti desiderate.

Questa architettura non utilizza un approccio PLL tipico, quindi non presenta conversione in salita. Di conseguenza, non è necessaria la moltiplicazione frazionaria o intera del PLL standard e la frequenza di uscita finale ha una correlazione 1:1 con la frequenza di risonanza del cristallo di quarzo a terza armonica. L'assenza di moltiplicazione frazionaria o intera semplifica il progetto e consente di ridurre al minimo il jitter nelle dimensioni più piccole possibili.

Specifiche e prestazioni nella realtà

Gli oscillatori di clock sono più di un semplice cristallo e del suo circuito analogico. Includono il buffering per garantire che il carico di uscita dell'oscillatore e le sue variazioni a breve e lungo termine non influiscano sulle prestazioni dell'unità. Inoltre, supportano vari livelli di uscita logica digitale differenziale per la compatibilità dei circuiti. Questa compatibilità elimina la necessità di un CI di traslazione dei livelli logici esterno. Un CI di questo tipo aumenterebbe il costo, l'ingombro e il jitter.

Poiché gli oscillatori di clock sono utilizzati in molte applicazioni diverse con tensioni di alimentazione differenti, devono essere offerti in una varietà di tensioni di alimentazione come +1,8 V, +2,5 V o +3,3 V, oltre a valori personalizzati che vanno tipicamente da 2,25 a 3,63 V. Devono inoltre essere disponibili con diverse opzioni di formato di uscita, come la logica positiva a bassa tensione/pseudo-accoppiata a emettitore (LVPECL) e la segnalazione differenziale a bassa tensione (LVDS), ma anche altri formati.

Uno sguardo a due famiglie di oscillatori a cristallo, AK2A e AK3A, dimostra cosa si può ottenere attraverso una sofisticata comprensione e integrazione di materiali, progettazione, architettura e test. Le due famiglie sono simili e si differenziano per le dimensioni e la frequenza massima.

La famiglia AK2A: questa famiglia di oscillatori a cristallo è offerta con frequenze nominali da 100 a 200 MHz ed è disponibile con tensioni di funzionamento di 2,5 V, 3,3 V e da 2,25 a 3,63 V con logica di uscita differenziale LVPECL, LVDS e HCSL.

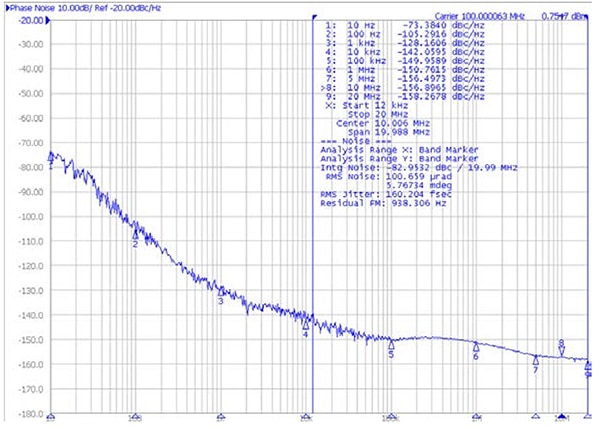

Tutti i componenti della famiglia hanno prestazioni simili, compreso un basso jitter RMS. Ad esempio, AK2ADDF1-100.000T è un dispositivo da 100,00 MHz, 3,3 V con uscite LVDS e un jitter RMS di 160,2 fs (Figura 5). La sua stabilità di frequenza è eccellente, superiore a ±15 ppm nell'intervallo di temperatura, ed è offerto in un contenitore a sei conduttori per dispositivi a montaggio superficiale (SMD) di 2,5 × 2,0 × 1,0 mm.

Figura 5: Il jitter è di 160 fs per AK2ADDF1-100.000T, un dispositivo da 3,3 V e 100 MHz con uscite LVDS. (Immagine per gentile concessione di Abracon)

Figura 5: Il jitter è di 160 fs per AK2ADDF1-100.000T, un dispositivo da 3,3 V e 100 MHz con uscite LVDS. (Immagine per gentile concessione di Abracon)

Tuttavia, con l'aumento delle frequenze di clock, il jitter deve diminuire per mantenere le prestazioni a livello di sistema. Per AK2ADDF1-156.2500T, un oscillatore LVDS da 156,25 MHz, il jitter RMS tipico scende a 83 fs.

La famiglia AK3A: i dispositivi della famiglia AK3A sono leggermente più grandi di quelli della famiglia AK2A, con un ingombro di 3,2 × 2,5 × 1,0 mm (Figura 6). Sono disponibili versioni con specifiche fino a 212,5 MHz, leggermente superiori al limite di 200 MHz della famiglia AK2A.

Figura 6: Gli oscillatori a cristallo AK3A (a destra) sono leggermente più lunghi e più larghi della serie AK2A (a sinistra); sono disponibili in versioni per frequenze fino a 212,5 MHz, rispetto ai 200 MHz de modello AK2A. (Immagine per gentile concessione di Abracon)

Figura 6: Gli oscillatori a cristallo AK3A (a destra) sono leggermente più lunghi e più larghi della serie AK2A (a sinistra); sono disponibili in versioni per frequenze fino a 212,5 MHz, rispetto ai 200 MHz de modello AK2A. (Immagine per gentile concessione di Abracon)

Le specifiche generali del dispositivo AK3A sono simili a quelle del corrispondente della famiglia AK2A. Un esempio è AK3ADDF1-156.2500T3, un oscillatore LVDS da 156,25 MHz con un jitter RMS tipico di 81 fs, leggermente migliore del corrispondente della famiglia AK2A.

Il jitter per entrambe le famiglie varia a seconda della frequenza operativa, della tensione di funzionamento, delle dimensioni del contenitore e della scelta delle uscite.

Ulteriori considerazioni sul mondo reale

Non è sufficiente avere un oscillatore di clock che funziona secondo le specifiche solo il giorno in cui esce dalla fabbrica. Come tutti i componenti, soprattutto quelli analogici e passivi, questi oscillatori sono soggetti a deriva nel tempo dovuta all'invecchiamento dei materiali che li compongono e alle sollecitazioni interne.

Questa realtà è particolarmente vera per gli oscillatori di clock ad alte prestazioni, in quanto non esistono modi pratici o semplici per correggere o compensare questa deriva aggiungendo software o circuiti intelligenti. Tuttavia, esistono alcuni modi per mitigare gli effetti della deriva. Tra questi, lunghi periodi di burn-in da parte dell'utente finale per accelerare l'invecchiamento dell'oscillatore, oppure l'uso di un oscillatore in un involucro termostabilizzato. Il primo richiede tempo ed è una grande sfida per la supply chain, mentre il secondo è grande, costoso ed energivoro.

Riconoscendo che l'invecchiamento è un parametro critico, la famiglia ClearClock di Abracon offre una precisione di frequenza rigorosa e completa per l'intera durata del prodotto finale, da 10 a 20 anni. Abracon garantisce una stabilità di frequenza migliore di ±50 ppm in questo periodo. Ciò è possibile grazie a un'accurata selezione e fabbricazione del cristallo a terza armonica e al suo condizionamento per ottenere una stabilità di ±15 ppm su valori compresi tra -20 °C e +70 °C e di ±25 ppm su valori compresi tra -40 °C e +85 °C.

Come sempre, l'ingegneria è una questione di compromessi. Le serie AK2A e AK3A di Abracon offrono prestazioni migliori in termini di jitter-rumore rispetto alle serie precedenti (rispettivamente AK2 e AX3 di I generazione) grazie all'utilizzo di un oscillatore ASIC di prossima generazione (II generazione), che garantisce bassissime prestazioni di jitter RMS.

Questo miglioramento è a scapito di un leggero aumento del consumo energetico. Il consumo massimo passa da 50 mA per la Gen I a 60 mA per la Gen II, anche se i dispositivi a bassa tensione consumano circa la metà. Gli oscillatori ClearClock di seconda generazione, quindi, offrono un bassissimo jitter RMS pur mantenendo un basso consumo energetico.

Conclusione

Gli oscillatori di temporizzazione sono il cuore pulsante di un circuito dati o di una funzione di clock e la loro precisione, il jitter e la stabilità sono parametri critici per ottenere le prestazioni richieste a livello di sistema, tra cui un SNR elevato e un BER basso. Frequenze di clock più elevate sono possibili grazie alla selezione di materiali e architetture innovative che soddisfano le rigorose specifiche prestazionali richieste dal settore e dai suoi vari standard. Le serie AK2A e AK3A di Abracon sono caratterizzate da un jitter inferiore a 100 fs nell'intervallo da 100 a 200 MHz in contenitori SMD minuscoli.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.