Utilizzare un processore multicore efficiente per creare prodotti abilitati alla voce più intelligenti

Contributo di Editori nordamericani di DigiKey

2020-02-14

La domanda di prodotti più intelligenti permea in quasi tutte le aree applicative via via che gli utenti acquisiscono familiarità e si affidano agli assistenti digitali virtuali come Amazon Alexa, Assistente Google, Apple Siri e Microsoft Cortana. Oltre a offrire praticità, questi assistenti svolgono un ruolo crescente nel miglioramento della sicurezza e nella protezione in una vasta gamma di prodotti per sistemi industriali e applicazioni sanitarie. Per gli sviluppatori, tuttavia, i progetti sottostanti questi prodotti a volte comportano richieste contrastanti per i processori in grado di offrire prestazioni ottimizzate, costi e ingombri ottimizzati e un funzionamento efficiente.

Questo articolo spiega agli sviluppatori come utilizzare un processore multicore, in questo caso i.MX 8M Nano di NXP per soddisfare le diverse esigenze di elaborazione e interfacciamento dei prodotti intelligenti emergenti in segmenti applicativi che vanno dall'automazione domestica intelligente e industriale ai sistemi medicali. In particolare, questo articolo mostra come utilizzare questo processore per facilitare l'implementazione di soluzioni vocali di prossima generazione con funzionalità di elaborazione audio avanzate.

L'evoluzione dei prodotti intelligenti

Il rapido aumento delle tecnologie di assistente vocale ha indotto gli utenti a cercare maggiori funzionalità nei prodotti intelligenti. I prodotti emergenti non devono solo rispondere ai comandi vocali, ma devono anche incorporare una maggiore intelligenza, utilizzando una maggiore varietà di dati di ingresso provenienti da sensori, telecamere e altri prodotti. Non è sufficiente che gli interruttori intelligenti accendano e spengano le luci o che la lavastoviglie funzioni a comandi vocali. Con la crescita di applicazioni sofisticate, i dispositivi sottostanti dovranno supportare combinazioni diversificate di sensori, capacità di elaborazione avanzate utilizzando metodi di intelligenza artificiale (IA) e display grafici 3D.

La necessità di prodotti più intelligenti va oltre il desiderio di una maggiore comodità. In aree applicative critiche come l'automazione industriale e l'assistenza sanitaria, la capacità di un dispositivo di avvisare in modo proattivo gli utenti di pericoli o condizioni patologiche può fare la differenza. Un operaio che indossa un elmetto in grado di monitorare l'ambiente circostante può evitare più facilmente i pericoli; un paziente a rischio che indossa un minuscolo monitor sanitario che ne controlla continuamente i parametri vitali può ricevere l'intervento necessario molto prima che vada in crisi.

Questi e altri prodotti intelligenti impongono requisiti di progettazione specifici tanto diversi quanto le loro applicazioni finali, ma la maggior parte condivide la necessità di elaborazione ad alte prestazioni, capacità multimediali e funzionamento sicuro. Per gli sviluppatori, questi requisiti funzionali si combinano con la necessità fondamentale di soluzioni scalabili per servire applicazioni più robuste, mentre si riducono fisicamente per soddisfare le aspettative degli utenti in termini di dimensioni, costi e consumi ridotti. Basato su un'architettura eterogenea multicore, la famiglia di processori di applicazioni i.MX 8M Nano di NX soddisfa i requisiti ampi e diversificati dei progetti per prodotti intelligenti emergenti.

Core ad alte prestazioni

i.MX 8M Nano di NXP è l'ultima aggiunta alla famiglia di processori i.MX 8M di NXP, progettata come una piattaforma di elaborazione multicore scalabile. Per applicazioni video di fascia alta, i processori di punta i.MX 8M di NXP, come MIMX8MQ5DVAJZAB offre una risoluzione dello schermo con decodifica hardware di video 4K in alta gamma dinamica (HDR). Per video 1080p, i processori i.MX 8M Mini di NXP come MIMX8MM6CVTKZAA forniscono il supporto per la decodifica hardware 1080p. Entrambe le serie i.MX 8M e 8M Mini combinano fino a quattro core del processore per applicazioni Arm® Cortex®-A53 con un core per microcontroller Arm Cortex-M4F.

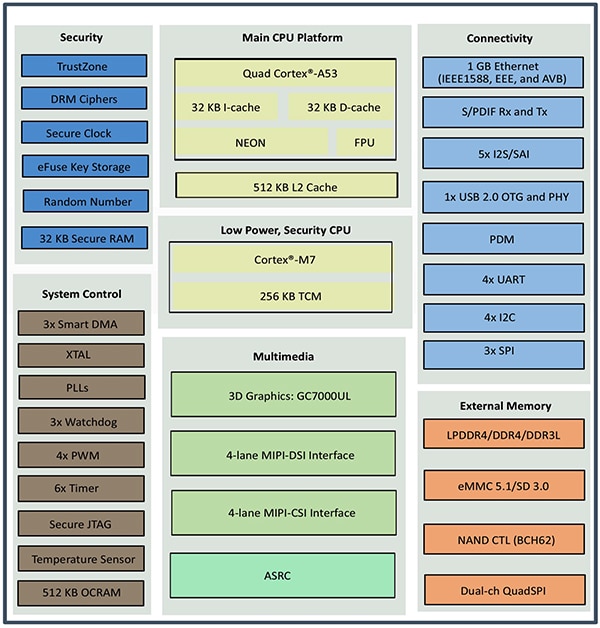

Per contro, i.MX 8M Nano MIMX8MN6CVTIZAA di NXP è un processore che combina quattro core Arm Cortex-A53 con un core Arm Cortex-M7, per offrire le massime prestazioni tra i core della serie Arm Cortex-M, incluso Cortex-M4F.

Oltre a complementare i core di processore, i processori i.MX 8M Nano supportano una vasta gamma di dispositivi di memoria esterni e offrono una gamma completa di interfacce periferiche esterne che in genere sono richieste dalle applicazioni consumer e industriali (Figura 1).

Figura 1: Il processore i.MX 8M Nano di NXP combina fino a quattro processori per applicazioni Arm Cortex-A53, un microcontroller Arm Cortex-M7, sottosistemi hardware specializzati e interfacce periferiche esterne complete tipiche delle applicazioni consumer e industriali. (Immagine per gentile concessione di NXP)

Figura 1: Il processore i.MX 8M Nano di NXP combina fino a quattro processori per applicazioni Arm Cortex-A53, un microcontroller Arm Cortex-M7, sottosistemi hardware specializzati e interfacce periferiche esterne complete tipiche delle applicazioni consumer e industriali. (Immagine per gentile concessione di NXP)

Le varianti disponibili nella serie di processori i.MX 8M Nano consentono agli sviluppatori di soddisfare requisiti specifici in termini di costi e prestazioni. Ad esempio, i componenti ad alte prestazioni integrano una vasta gamma di sottosistemi specializzati per sicurezza, display grafici 3D, elaborazione audio e altro. Altri modelli della serie i.MX 8M Nano offrono opzioni con un numero minore di core Cortex-A53 e versioni "Lite" dalle funzionalità grafiche ridotte.

Tutti i modelli della serie di processori i.MX 8M Nano offrono comunque una combinazione di prestazioni per applicazioni e le capacità in tempo reale necessarie per gli emergenti prodotti intelligenti.

Progettato per l'esecuzione ad alte prestazioni del software applicativo, ciascun core del processore per applicazioni Arm Cortex-A53 può funzionare a frequenze di clock fino a 1,5 GHz con una cache di istruzioni dedicate di livello 1 (L1) da 32 kB (I- cache), una cache dati da 32 kB (D-cache) e una cache unificata L2 da 512 kB condivisa. Insieme all'unità a virgola mobile (FPU) integrata, questi core supportano la tecnologia Neon di Arm per operazioni SIMD (istruzione singola, dati multipli) avanzate utilizzate nell'elaborazione dei segnali digitali e in altri algoritmi avanzati per applicazioni che fanno uso intensivo dei dati.

Per i requisiti dei sistemi embedded, il core per microcontroller Arm Cortex-M7 funziona a frequenze fino a 750 MHz fornendo al contempo esecuzione ad alte prestazioni per i processi in tempo reale che richiedono bassa latenza e un funzionamento deterministico. Per velocizzare ulteriormente l'elaborazione, il core include una FPU integrata e 256 kB di memoria strettamente accoppiata (TCM) utilizzata per le istruzioni e la cache di dati.

Tuttavia, per attività di elaborazione in tempo reale complesse, la capacità di riconoscere rapidamente fonti di interrupt distinte può essere tanto fondamentale quanto la pura potenza elaborativa. Nei processori i.MX 8M Nano, un controller di interrupt globale (GIC) integrato in ciascun core Arm Cortex-A53 e un controller di interrupt a vettorizzazione annidata (NVIC) nel core Arm Cortex-M7, consentono di gestire gli interrupt con precisione, da quasi 128 fonti di richiesta interrupt distinte corrispondenti a stati principali, timer, eventi dell'interfaccia periferica, operazioni di accesso diretto alla memoria (DMA), processi hardware specializzati e molto altro.

Elaborazione multicore eterogenea

Ciascun core di processore i.MX 8M Nano offre separatamente una solida risorsa di elaborazione. Utilizzati congiuntamente, questi core multipli offrono una piattaforma dalla potenza di elaborazione capace di gestire differenti requisiti sia in termini di prestazioni in tempo reale sia per l'esecuzione del software applicativo che può confondere la progettazione di prodotti intelligenti. Un prodotto intelligente basato su questo processore può, ad esempio, utilizzare il core Cortex-M7 per elaborare flussi audio in tempo reale, mentre al contempo utilizza algoritmi in esecuzione su uno o più core Cortex-A53 per analizzare i dati risultanti e fornire agli utenti una visualizzazione grafica in 3D dei risultati.

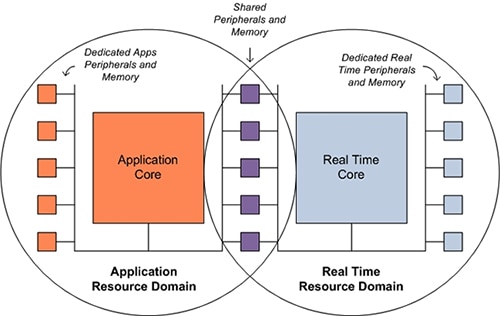

Tuttavia, per eseguire in modo affidabile questo tipo di elaborazione multicore eterogenea coordinata, un sistema multicore richiede un'attenta orchestrazione delle operazioni di elaborazione e di scambio dati tra vari core, blocchi hardware specializzati e periferiche. Nel processore i.MX 8M Nano tale orchestrazione è integrata in meccanismi basati su hardware per semafori e messaggistica generalmente utilizzati da servizi software di basso livello in ambienti multiprocessore.

Nei sistemi embedded, l'esecuzione orchestrata si estende anche a risorse hardware come memoria e periferiche. Per questa attività, il processore integra un Resource Domain Controller (RDC) dedicato, progettato per garantire la condivisione sicura delle risorse laddove appropriato o l'isolamento affidabile quando necessario. Di conseguenza, il software applicativo e il codice in tempo reale possono controllare indipendentemente le risorse di controllo dedicate al proprio dominio mentre condividono un insieme di risorse comuni (Figura 2).

Figura 2: I meccanismi basati su hardware nel processore i.MX 8M Nano di NXP assicurano l'isolamento delle risorse dedicate al dominio dell'applicazione Cortex-A53 o al dominio in tempo reale Cortex-M7, consentendo al contempo la condivisione sicura delle risorse laddove necessario. (Immagine per gentile concessione di NXP)

Figura 2: I meccanismi basati su hardware nel processore i.MX 8M Nano di NXP assicurano l'isolamento delle risorse dedicate al dominio dell'applicazione Cortex-A53 o al dominio in tempo reale Cortex-M7, consentendo al contempo la condivisione sicura delle risorse laddove necessario. (Immagine per gentile concessione di NXP)

Supporto specializzato per prodotti intelligenti

Utilizzando solo i core multipli e le capacità di condivisione delle risorse del processore i.MX 8M Nano, gli sviluppatori possono creare applicazioni sofisticate per gli emergenti prodotti intelligenti realizzati con assistenti vocali e grafica 3D. Queste applicazioni ricevono un ulteriore incremento prestazionali riducendo al contempo il footprint software grazie al supporto hardware specializzato per prodotti intelligenti integrato nei processori i.MX 8M Nano.

In termini di grafica, l'unità di elaborazione grafica (GPU) integrata del processore fornisce accelerazione grafica 2D e 3D e supporta le librerie grafiche standard tra cui Vulkan, Open Computing Language (OpenCL) e Open Graphics Library (OpenGL). Un controller con interfaccia per display a cristalli liquidi (LCDIF) integrato supporta display a 1080p60 (1080 di scansione progressiva 60 fotogrammi al secondo).

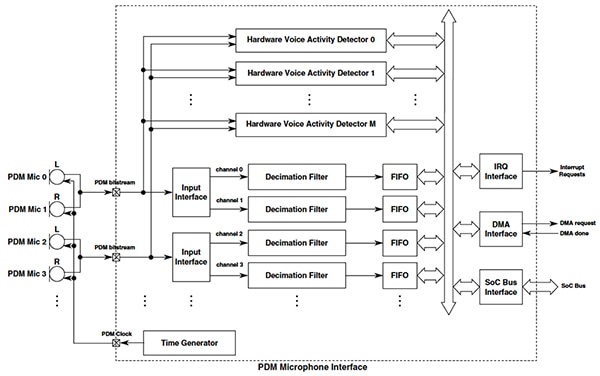

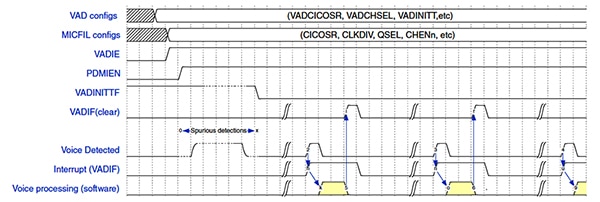

Mentre la GPU su chip scarica l'elaborazione di visualizzazione dai core, un altro set di sottosistemi hardware scarica svariate attività di elaborazione audio basate su processori convenzionali che in genere rallentano i sistemi. Per l'elaborazione degli ingressi microfono, l'interfaccia del microfono (MICFIL) a modulazione di densità di impulso (PDM) del processore fornisce una pipeline multistadio progettata per generare dati di modulazione impulso/codice (PCM) a 16 bit filtrati dall'ingresso a 1 bit ricevuto dai microfoni PDM (Figura 3).

Figura 3: Il sottosistema di interfaccia del processore i.MX 8M Nano di NXP per l'ingresso microfono PDM combina pipeline hardware distinte per l'elaborazione del segnale audio e il rilevamento dell'attività vocale. (Immagine per gentile concessione di NXP)

Figura 3: Il sottosistema di interfaccia del processore i.MX 8M Nano di NXP per l'ingresso microfono PDM combina pipeline hardware distinte per l'elaborazione del segnale audio e il rilevamento dell'attività vocale. (Immagine per gentile concessione di NXP)

Per una tipica applicazione vocale, i progettisti devono solo collegare un microfono PDM a uno degli otto canali PDM supportati dal processore. Nel sottosistema di interfaccia del microfono PDM, un'interfaccia di ingresso combina i dati PDM multiplati nel tempo da una coppia di microfoni per formare una corsia comprendente i canali sinistro e destro.

Nella fase successiva per ciascun canale, un filtro di decimazione programmabile dedicato fornisce diverse bande passanti a seconda della velocità di uscita desiderata e una delle sei impostazioni di selezione della qualità (QSEL) tra cui alta, media e bassa qualità, nonché tre livelli aggiuntivi di qualità molto bassa. Ad esempio, con una velocità di uscita di 48 kHz, le modalità di qualità molto bassa impostano la banda passante del filtro da 10,5 Hz a 11,25 kHz rispetto a una banda passante da 21 Hz a 22,5 kHz per le modalità alta, media e bassa. Infine, i risultati per ciascun canale sono resi disponibili in buffer FIFO (first-in, first-out) separati per ciascun canale per la generazione degli interrupt, il trasferimento tramite DMA o l'accesso al bus.

Rilevamento dell'attività vocale basata su hardware

Parallelamente a questa pipeline di condizionamento del segnale audio, l'interfaccia del microfono PDM fornisce una serie di rilevatori hardware di attività vocale (HWVAD) che monitorano i canali di ingresso microfono desiderati. (Nota: la figura sopra suggerisce che ogni HWVAD è associato a un corsia ma la documentazione sostiene il supporto da parte di canali e del nome di un registro, VADCHSEL.) Per supportare il funzionamento di HWVAD, il processore fornisce un set completo di registri di dispositivi con i quali gli sviluppatori possono definire la configurazione HWVAD specifica necessaria per la loro applicazione (Tabella 1).

|

Tabella 1: I registri del processore i.MX 8M Nano di NXP generalmente utilizzati per configurare i rilevatori hardware di attività vocale integrati nell'interfaccia del microfono PDM (MICFIL) del processore. (Tabella per gentile concessione di DigiKey, basata su dati di NXP)

Sulla base di queste impostazioni del registro, HWVAD utilizza algoritmi di rilevamento vocale integrati per identificare l'attività vocale. Al rilevamento, HWVAD genera un interrupt per riattivare un core, in genere Cortex-M7, per l'ulteriore elaborazione (Figura 4).

Figura 4: Con le impostazioni di configurazione programmate, i rilevatori hardware di attività vocale del processore i.MX 8M Nano di NXP consentono ai core di processore di portarsi in sospensione o di eseguire l'elaborazione fino a quando non viene rilevata una voce e diventa necessaria l'ulteriore elaborazione vocale. (Immagine per gentile concessione di NXP)

Figura 4: Con le impostazioni di configurazione programmate, i rilevatori hardware di attività vocale del processore i.MX 8M Nano di NXP consentono ai core di processore di portarsi in sospensione o di eseguire l'elaborazione fino a quando non viene rilevata una voce e diventa necessaria l'ulteriore elaborazione vocale. (Immagine per gentile concessione di NXP)

In un'applicazione di assistente vocale, il core controllerebbe il flusso audio per rilevare la parola di riattivazione appropriata. Se la rileva, in genere il core dovrebbe fornire il flusso audio ai servizi di assistente vocale basati su cloud supportati dall'applicazione.

Oltre al sottosistema di interfaccia del microfono PDM, il processore i.MX 8M Nano offre anche cinque moduli di interfaccia audio sincrona (SAI) che supportano molti formati audio standard, tra cui Inter-IC Sound (I2S), codec audio 97 (AC97), audio multiplato a divisione di tempo (TDM) e Direct Stream Digital (DSD), nonché dati di codec o di elaborazione di segnali digitali (DSP).

Per soddisfare specifici requisiti applicativi, agli sviluppatori viene spesso affidato il compito di convertire i campioni di input audio in un'altra frequenza di campionamento e una risoluzione diversa. Anziché utilizzare i cicli del processore per questa attività comune, il processore i.MX 8M Nano integra un sottosistema dotati di convertitore di frequenza di campionamento asincrono (ASRC) dedicato,

capace di elaborare simultaneamente fino a 32 canali audio, per convertire automaticamente i campioni sorgente nella frequenza di campionamento desiderata (tra 8 kHz e 384 kHz) e nella risoluzione (in formato a virgola mobile o virgola fissa IEEE con precisione singola a 16, 20, 24 o 32 bit per campione). Nel processo, per ottenere il risultato desiderato l'ASRC converte tutti i dati di input al formato a virgola mobile IEEE a 64 bit per garantire la conversione in salita o a scalare accurata dei dati di campionamento audio in base alle esigenze.

Gestione della potenza mediante un controller di alimentazione generale

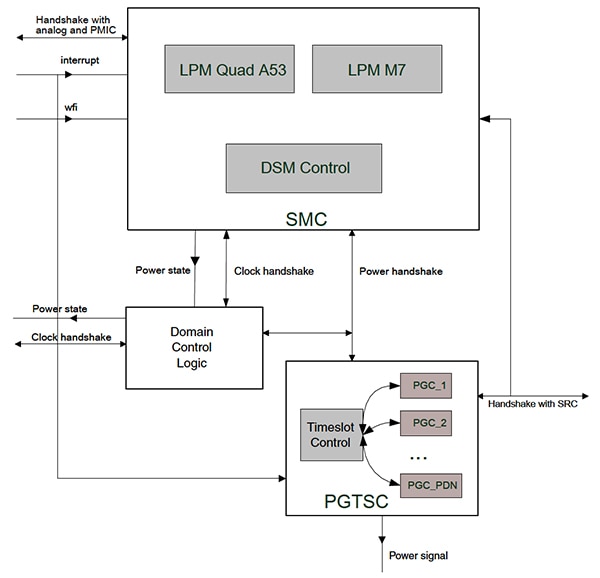

Con la vasta integrazione di core di processore e sottosistemi hardware, l'architettura del processore i.MX 8M Nano di NXP combina una serie di domini e modalità di potenza separati e integrati nei singoli core e sottosistemi. Per gestire la potenza di questo insieme di core e blocchi specializzati, il processore i.MX 8M Nano include un sofisticato controller di potenza generale (GPC) progettato per coordinare molteplici funzionalità di gestione della potenza. All'interno del GPC, il controller della modalità di sistema (SMC) gestisce la modalità a bassa potenza (LPM) di ciascun core e la modalità di sospensione profonda (DSM) generale, mentre un controller di slot temporale con power gating (PGTSC) gestisce le funzionalità di clock gating utilizzate per ridurre la potenza del sistema disabilitando l'alimentazione ai sottosistemi inattivi (Figura 5).

Figura 5: Per ottimizzare la potenza a livello di sistema, i.MX 8M Nano di NXP integra un controller di potenza completo che gestisce le funzionalità di power gating e di bassa potenza integrate nei core di processore. (Immagine per gentile concessione di NXP)

Figura 5: Per ottimizzare la potenza a livello di sistema, i.MX 8M Nano di NXP integra un controller di potenza completo che gestisce le funzionalità di power gating e di bassa potenza integrate nei core di processore. (Immagine per gentile concessione di NXP)

Sotto controllo software o hardware, GPC utilizza 20 diversi slot temporali nel PGTSC per accendere o spegnere uno dei vari domini di potenza con clock gating nel processore. Qui, il controller procede in maniera sequenziale attraverso questi slot temporali, attivando qualsiasi richiesta di accensione o spegnimento prima di passare allo slot successivo. Oltre a soddisfare specifici requisiti di sequenziamento della potenza, questo approccio consente agli sviluppatori di ridurre la corrente di rampa durante l'accensione del sistema o quando si riattiva il sistema da una modalità a basso consumo o di sospensione profonda.

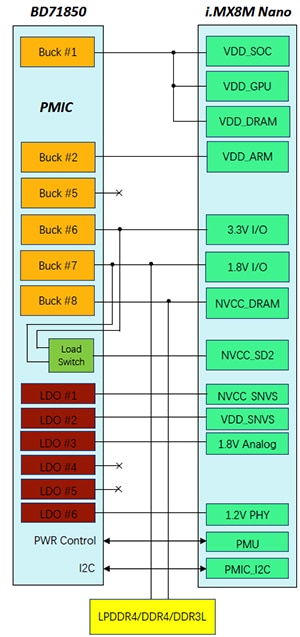

Alimentare i molteplici domini della potenza del processore i.MX 8M Nano è semplice. Progettato appositamente per supportare il processore i.MX 8M Nano di NXP, BD71850MWV di ROHM Semiconductor è un circuito integrato di gestione della potenza (PMIC) che fornisce tutti i rail di alimentazione necessari al processore e ad altre periferiche di sistema. Infatti, il PMIC BD71850MWV integra il proprio sequenziatore di potenza, semplificando ulteriormente l'accensione e lo spegnimento in sicurezza, non solo per il processore ma anche per la memoria esterna, i sensori o altri dispositivi del sistema (Figura 6). Per gli sviluppatori, l'integrazione del PMIC BD71850MWV in un progetto non richiede componenti aggiuntivi, oltre ai tipici condensatori di disaccoppiamento (non illustrati).

Figura 6: I vari core e sottosistemi hardware del processore i.MX 8M Nano di NXP determinano la necessità di più rail di alimentazione, ma il circuito integrato di gestione della potenza (PMIC) BD71850MWV di ROHM è una soluzione pronta all'uso. (Immagine per gentile concessione di NXP)

Figura 6: I vari core e sottosistemi hardware del processore i.MX 8M Nano di NXP determinano la necessità di più rail di alimentazione, ma il circuito integrato di gestione della potenza (PMIC) BD71850MWV di ROHM è una soluzione pronta all'uso. (Immagine per gentile concessione di NXP)

Supporto per lo sviluppo

Sebbene i requisiti dell'interfaccia hardware per i progetti basati su i.MX 8M Nano siano relativamente semplici, NXP solleva gli sviluppatori anche da questa incombenza progettuale relativamente semplice di dover valutare il processore o prototipare nuovi prodotti intelligenti. Grazie a un kit di sviluppo già implementato e un progetto di riferimento per il processore i.MX 8M Nano, il kit di valutazione 8MNANOD4-EVK combina il processore i.MX 8M Nano e il PMIC BD71850MWV con il modulo transceiver Wi-Fi/Bluetooth LBEE5HY1MW di Murata Electronics per creare una piattaforma ideale per la valutazione e lo sviluppo di prototipi. Insieme a molteplici opzioni di interfaccia e connettori correlati, il kit di valutazione include un set completo di dispositivi di memoria esterni tra cui RAM dinamica statica (SDRAM), Flash NOR e Flash NAND. Utilizzando il kit di valutazione, gli sviluppatori possono esplorare diverse modalità operative e configurazioni, incluso l'avvio da flash esterna o l'avvio sicuro tramite immagini di avvio provviste di firma digitale.

Agli sviluppatori pronti a iniziare lo sviluppo di software personalizzato, NXP fornisce i driver, i BSP (board support package) e il middleware compatibili con l'ambiente di sviluppo integrato (IDE) MCUXpresso e con IDE di terzi. Per creare applicazioni progettate per sfruttare i metodi di apprendimento automatico, gli sviluppatori possono affidarsi all'ambiente di sviluppo software ML eIQ di NXP e alle librerie di inferenze ottimizzate per i.MX come eIQ for TensorFlow Lite per l'inferenza basata su Cortex-M7 o la porta di NXP del kit di sviluppo software per reti neurali (NN SDK) di Arm per l'inferenza basata su Cortex-A53.

Conclusione

Spinti dalla rapida accettazione dei prodotti di assistente vocale, i prodotti intelligenti di nuova generazione devono far fronte ad aspettative crescenti non solo per un miglior supporto audio, ma anche per prestazioni maggiori, grafica migliore e il funzionamento efficiente dal punto di vista energetico. Per gli sviluppatori, la progettazione efficace di un sistema per questi prodotti richiede una combinazione di esecuzione di software applicativo ad alte prestazioni e capacità in tempo reale a bassa latenza. Tutto questo è stato difficile realizzare finora nell'ottica dei vincoli imposti in termini di dimensioni, costi e potenza. Con la disponibilità di una famiglia scalabile di processori multicore da NXP, gli sviluppatori possono soddisfare i requisiti di progettazione di prodotti intelligenti per un ampio ventaglio di applicazioni, tra cui consumer, industriali e medicali.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.