Utilizzare moduli con amplificatori integrati per eliminare la "magia nera" dalla progettazione di ADC ad alta velocità

Contributo di Editori nordamericani di DigiKey

2021-04-29

I progettisti di sistemi come l'acquisizione dei dati, Hardware in the Loop (HiL) e analizzatori di potenza hanno bisogno di una catena di convertitori di segnali analogici che possa raggiungere un'alta risoluzione e un'alta precisione a frequenze di campionamento molto elevate, spesso fino a 15 Msps. Tuttavia, per molti sviluppatori i progetti analogici ad alta velocità possono sembrare "magia nera", specialmente quando si trovano di fronte a una serie di elementi parassiti occulti che minano l'integrità del segnale.

Ad esempio, i progetti tipici sono discreti e contengono diversi circuiti integrati e componenti, tra cui un amplificatore completamente differenziale (FDA), un filtro passa-basso di primo (1o) ordine (LPF), un riferimento di tensione e un convertitore analogico/digitale (ADC) ad alta velocità e risoluzione. Le correnti parassite capacitive e resistive esistono all'interno e intorno all'amplificatore del driver ADC (FDA), al filtro di ingresso ADC e all'ADC.

Eliminare, ridurre o mitigare gli effetti di questi elementi parassiti è una sfida che richiede un alto grado di abilità e molti cicli di progettazione e iterazioni del layout PCB, compromettendo i tempi di sviluppo e i budget. Quello che serve è una soluzione più completa e integrata che risolva molti di questi problemi.

Questo articolo descriverà un circuito di acquisizione dati discreto e i relativi problemi di layout e poi introdurrà un modulo integrato che contiene un ADC ad alta risoluzione e ad alta velocità con registro ad approssimazioni successive (SAR) con un front-end FDA. L'articolo mostra come il modulo completo ADAQ23875 di Analog Devices e la scheda di sviluppo associata superano i problemi di progettazione ad alta velocità semplificando e accelerando il processo, pur ottenendo i risultati di conversione richiesti.

Percorso del segnale di acquisizione dati ad alta velocità

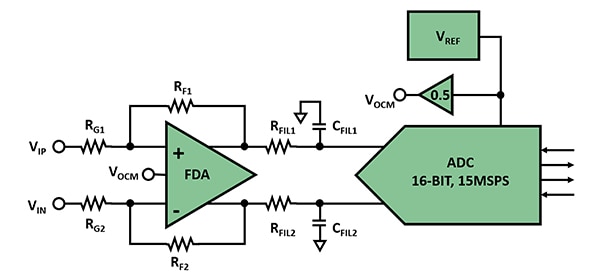

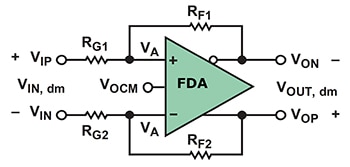

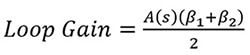

Gli ADC ad alte prestazioni utilizzano ingressi differenziali per migliorare le prestazioni complessive bilanciando i segnali di ingresso e respingendo il rumore di modo comune e le interferenze. Un driver ADC analogico ha prestazioni ottimali quando gli ingressi al driver ADC analogico e all'ADC sono completamente differenziali (Figura 1). L'uso di un'interfaccia seriale LVDS (segnalazione differenziale a bassa tensione), a destra, permette al sistema di funzionare a velocità estremamente elevate per servire applicazioni di acquisizione dati, HiL e analizzatori di potenza.

Figura 1: Un sistema di acquisizione dati ad alta frequenza con un front-end FDA, un filtro analogico di 1o ordine e un ADC SAR con ingresso differenziale e un'interfaccia seriale LVDS ad alta velocità. (Immagine per gentile concessione di Bonnie Baker)

Figura 1: Un sistema di acquisizione dati ad alta frequenza con un front-end FDA, un filtro analogico di 1o ordine e un ADC SAR con ingresso differenziale e un'interfaccia seriale LVDS ad alta velocità. (Immagine per gentile concessione di Bonnie Baker)

La configurazione in Figura 1 esegue molte funzioni essenziali, tra cui la scalatura dell'ampiezza, la conversione da sbilanciato a differenziale, il buffering, la regolazione dell'offset di modo comune e il filtraggio.

Tecnologia dei driver FDA

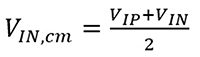

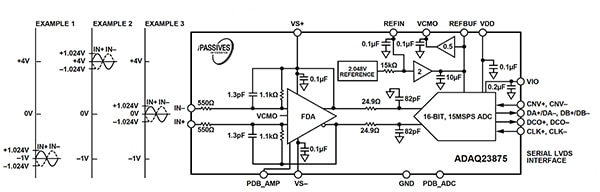

Il funzionamento del driver ADC con feedback di tensione FDA è come un amplificatore tradizionale, ma con due differenze. Anzitutto, l'FDA ha una uscita differenziale con un ulteriore terminale di uscita negativo (VON). Secondo, ha un terminale di ingresso aggiunto (VOCM) che imposta la tensione di modo comune in uscita (Figura 2).

Figura 2: L'FDA ha due ingressi con anelli di retroazione e regolazione di tensione (VOCM) di modo comune in uscita. Questa configurazione crea tensioni di ingresso differenziale (VIN, dm) e di uscita differenziale (VOUT, dm) indipendenti. (Immagine per gentile concessione di Analog Devices)

Figura 2: L'FDA ha due ingressi con anelli di retroazione e regolazione di tensione (VOCM) di modo comune in uscita. Questa configurazione crea tensioni di ingresso differenziale (VIN, dm) e di uscita differenziale (VOUT, dm) indipendenti. (Immagine per gentile concessione di Analog Devices)

Internamente, l'FDA ha tre amplificatori: due all'ingresso e il terzo che funge da stadio di uscita. La retroazione negativa (RF1, RF2) e l'alto guadagno ad anello aperto dei due amplificatori di ingresso interni fanno sì che il comportamento dei terminali di ingresso, VA+ e VA-, sia virtualmente equivalente. Invece di una uscita sbilanciata, l'FDA produce un'uscita differenziale bilanciata tra VOP e VON, con una tensione di modo comune di VOCM.

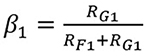

I segnali di ingresso differenziali (VIP e VIN) sono uguali in ampiezza e opposti in fase intorno a una tensione di riferimento di modo comune (VIN, cm) con un segnale di ingresso bilanciato. Le equazioni 1 e 2 mostrano come calcolare la tensione di ingresso di modo differenziale (VIN, dm) e la tensione di ingresso di modo comune (VIN, cm).

![]() Equazione 1

Equazione 1

Equazione 2

Equazione 2

Le equazioni 3 e 4 forniscono le definizioni di modo comune e differenziale dell'uscita.

![]() Equazione 3

Equazione 3

![]() Equazione 4

Equazione 4

Si noti l'aggiunta di VOCM nell'equazione 4.

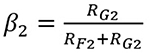

Come per i tipici circuiti amplificatori, il guadagno del sistema FDA dipende dai valori di RGx e RFx. Le equazioni 5 e 6 definiscono i due fattori di retroazione in ingresso, β1 e β2, per l'FDA.

Equazione 5

Equazione 5

Equazione 6

Equazione 6

Quando β1 è uguale a β2, l'equazione 7 dà il guadagno ideale ad anello chiuso per l'FDA.

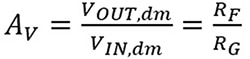

Equazione 7

Equazione 7

VOUT, dm fornisce un'idea delle prestazioni dei disadattamenti resistivi. L'equazione generale ad anello chiuso per VOUT, dm include VIP, VIN, β1, β2 e VOCM. L'equazione 8 mostra la formula per VOUT, dm con il guadagno di tensione ad anello aperto dell'amplificatore indicato come A(s).

![VOUT,dm = [2 / β1 + β2] [VOCM(β1-β2)+VIP(1-β1)-VIN(1-β2) / 1 + 2/ A(S)(β1+β2)] Equazione 8](http://sc-a.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation8.jpg?la=en&ts=fc1271d3-3f9d-4f4e-8cbc-609177a3d0b0) Equazione 8

Equazione 8

Quando β1 ≠ β2, l'errore della tensione di uscita differenziale (VOUT, dm) dipende principalmente da VOCM. Questo risultato indesiderato produce un offset e un eccesso di rumore nell'uscita differenziale. Se β1 = β2 ≡ β, l'equazione 8 diventa l'equazione 9.

![VOUT,dm / VIN,dm = [RF/RG] [1 / 1 + 1/A(S)(β)] Equazione 9](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation9.jpg?la=en&ts=f057ce79-c262-4b25-a568-5a964b24c988) Equazione 9

Equazione 9

Le due componenti dell'equilibrio di uscita sono l'ampiezza e la fase. Il bilanciamento dell'ampiezza misura se le due ampiezze di uscita corrispondono; nel caso ideale, corrispondono esattamente. L'equilibrio di fase misura la vicinanza delle differenze di fase tra le due uscite con l'ideale che equivale a 180°.

Le considerazioni sulla stabilità dell'FDA sono le stesse degli amplificatori operazionali standard. La specifica chiave è il margine di fase. Le schede tecniche dei prodotti forniscono il margine di fase di una particolare configurazione dell'amplificatore; tuttavia, gli effetti parassiti del layout della scheda CS possono ridurre significativamente la stabilità. Nel caso di un amplificatore a retroazione negativa, è abbastanza semplice: la stabilità dipende dal guadagno dell'anello, A(s) × β, dal segno e dalla grandezza. L'FDA, al contrario, ha due fattori di retroazione. Le equazioni 8 e 9 hanno il guadagno dell'anello nei loro denominatori. L'equazione 10 descrive il guadagno dell'anello per il caso del fattore di retroazione non corrisposto (β1 ≠ β2).

Equazione 10

Equazione 10

La mitigazione di tutti gli errori di cui sopra dipende dal noioso e costoso processo di accoppiamento con resistori discreti RG1, RG2, RF1 e RF2.

Prestazioni combinate FDA e ADC

La combinazione di FDA, resistori discreti, filtro di 1o ordine e ADC racconta la storia del rapporto segnale/rumore (SNR), della distorsione armonica totale (THD), del segnale/rumore e della distorsione (SINAD) e dell'intervallo dinamico senza spurie (SFDR) che si aggiungono alle caratteristiche di prestazione dell'FDA nella precisione e risoluzione globale del circuito. Le specifiche combinate includono SNR, THD, SINAD e SFDR. L'FDA ha numerose specifiche che hanno un impatto su queste specifiche di frequenza, come la larghezza di banda, il rumore della tensione di uscita, la distorsione, la stabilità e il tempo di assestamento, che influenzano le prestazioni dell'ADC. L'ADC ha il suo set di specifiche. Il problema principale è quello di selezionare l'FDA appropriato da abbinare all'ADC.

Layout della scheda

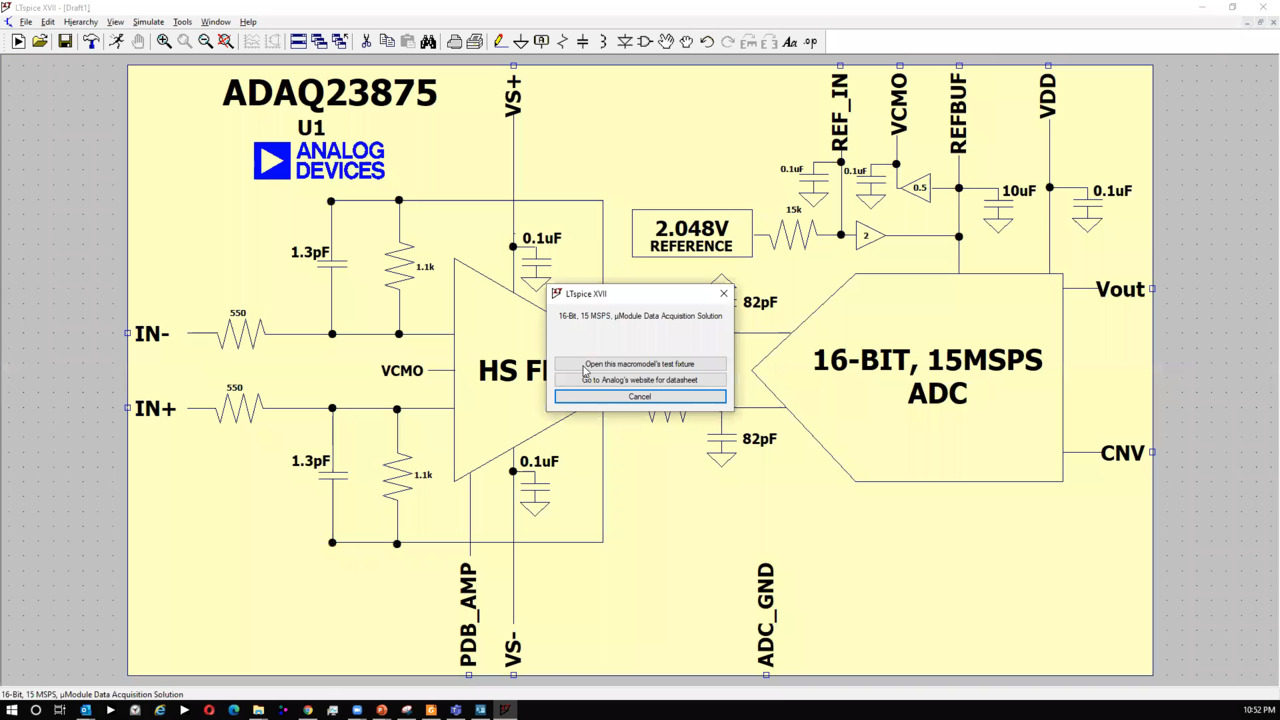

Il layout della scheda CS è l'ultimo passo del processo di progettazione. Sfortunatamente, il layout può essere un passo trascurato, con il risultato di una cattiva progettazione della scheda, che può compromettere o rendere inutile il circuito. Questo circuito discreto completo ha tre circuiti integrati, sei resistori e diversi condensatori di disaccoppiamento (Figura 3).

Figura 3: FDA e ADC SAR con LPF di 1o ordine con condensatori di disaccoppiamento dell'alimentazione. (Immagine per gentile concessione di Analog Devices)

Figura 3: FDA e ADC SAR con LPF di 1o ordine con condensatori di disaccoppiamento dell'alimentazione. (Immagine per gentile concessione di Analog Devices)

Nella Figura 3, gli elementi parassiti che minano le prestazioni dei circuiti ad alta velocità sono la capacità e l'induttanza parassita della scheda CS. La colpa è delle piazzole dei componenti, delle tracce, dei fori di via e della terra in parallelo ai piani di alimentazione. Queste capacità e induttanze sono particolarmente pericolose nei nodi sommatori dell'amplificatore dove introducono poli e zeri nella risposta di retroazione, causando picchi e instabilità.

Soluzione integrata

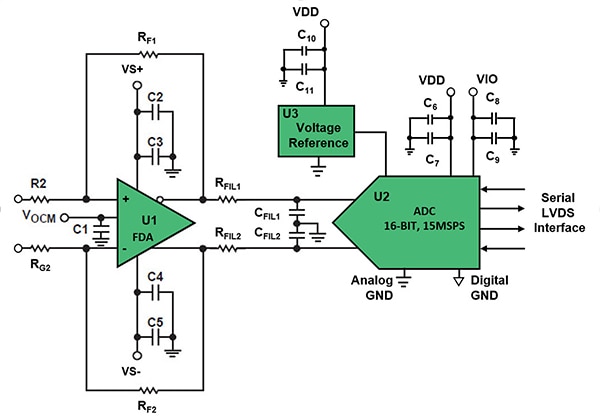

I convertitori SAR possono offrire un FDA, componenti passivi cruciali, filtri di 1o ordine, un riferimento di tensione e condensatori di disaccoppiamento per migliorare la risoluzione effettiva. Ad esempio, ADAQ23875 di Analog Devices è un modulo di acquisizione dati a 16 bit, 15 Msps con tutti questi elementi (Figura 4). Come tale, riduce il ciclo di sviluppo dei sistemi di misurazione di precisione trasferendo l'onere della selezione dei componenti, l'ottimizzazione e il layout dal progettista al circuito integrato.

Figura 4: ADAQ23875 semplifica la progettazione di ADC ad alta velocità combinando un FDA, un filtro di 1o ordine e un ADC SAR in un unico modulo supportato da resistori di guadagno tarati a laser intorno all'FDA, nonché da condensatori di disaccoppiamento su chip. (Immagine per gentile concessione di Analog Devices)

Figura 4: ADAQ23875 semplifica la progettazione di ADC ad alta velocità combinando un FDA, un filtro di 1o ordine e un ADC SAR in un unico modulo supportato da resistori di guadagno tarati a laser intorno all'FDA, nonché da condensatori di disaccoppiamento su chip. (Immagine per gentile concessione di Analog Devices)

I componenti resistivi passivi su chip hanno caratteristiche di adattamento e deriva superiori per minimizzare le fonti di errore parassite dipendenti e offrono prestazioni ottimizzate per garantire la corrispondenza di β1 e β2. La corrispondenza di questi guadagni dell'anello aiuta a creare l'offset di ±1 mV del modulo e le specifiche di rumore RMS totale di 91,6 µVRMS.

Il riferimento di tensione di bandgap a 2,048 V ha basso rumore e bassa deriva (20 ppm/°C) per supportare il sistema FDA e ADC a 16 bit. Insieme all'FDA, queste specifiche si traducono in una precisione ADC SAR di 90 dB SNR e una deriva del guadagno di ±1 ppm/°C. Il pin VOCM dell'FDA utilizza i 2,048 V del riferimento per fornire la tensione di modo comune in uscita.

Un buffer di riferimento interno moltiplica il riferimento di 2,048 V per due per creare 4,096 V per la tensione di riferimento ADC. La differenza di tensione tra il riferimento dell'ADC e GND determina l'intervallo di ingresso a fondo scala dell'ADC SAR ADAQ23875. Inoltre, ADAQ23875 ha un condensatore di disaccoppiamento su chip da 10 μF tra il buffer di riferimento e GND per assorbire i picchi di carica della conversione di riferimento ADC SAR e alleviare le limitazioni di progettazione discreta.

Come mostra la Figura 4, la tensione di modo comune in ingresso dell'FDA è indipendente dalla tensione di modo comune in uscita. Negli esempi da uno a tre, le tensioni di alimentazione sono:

VS+ = 7 V (tensione di alimentazione positiva FDA)

VS- = -2 V (tensione di alimentazione negativa FDA)

VDD = +5 V (tensione di alimentazione ADC)

VIO = 2,5 V (alimentazione dell'uscita analogica e digitale)

L'esempio 1 mostra un intervallo della tensione di ingresso di ±1,024 V con una tensione di ingresso di modo comune di -1 V. L'FDA applica un guadagno di 2 V/V a questi segnali e il livello FDA trasla la tensione di uscita del valore a VCMO o 2,048 V. Il processo presenta un intervallo di segnali di ±2,048 V con una tensione di modo comune da VCMO di 2,48 V all'uscita dell'FDA. La frequenza d'angolo del filtro di 1o ordine è 1/(2pR x C) Hz o ~78 MHz. L'intervallo di ingresso del segnale all'ADC è di ±2,048 V, con una tensione di modo comune di +2,048 V.

ADAQ23875 è dotato di un'interfaccia digitale LVDS con modalità di uscita a uno o due canali, che consente all'utente di ottimizzare la velocità dati dell'interfaccia di ciascuna applicazione. L'alimentazione digitale dell'interfaccia è VIO.

ADAQ23875 ha quattro alimentatori: uno interno del core ADC (VDD), uno dell'interfaccia di ingresso/uscita digitale (VIO), uno positivo FDA (VS+) e uno negativo (VS-). Per alleviare i problemi di layout per le schede CS, tutti i pin di alimentazione hanno condensatori di disaccoppiamento su chip da 0,1 mF o 0,2 mF. Sono necessari condensatori di disaccoppiamento ceramici di buona qualità da 2,2 μF (0402, X5R) sulla scheda CS presso l'uscita dei regolatori LDO. Questi regolatori generano i rail di alimentazione μModule (VDD, VIO, VS+ e VS-) per minimizzare la suscettibilità alle interferenze elettromagnetiche (EMI) e ridurre l'effetto dei glitch sulla linea di alimentazione. Tutti gli altri condensatori di disaccoppiamento richiesti sono all'interno di ADAQ23875, per migliorare il rapporto di reiezione dell'alimentazione (PSRR) del sottosistema e risparmiare spazio e costi aggiuntivi. Per utilizzare il riferimento interno e il buffer di riferimento interno, disaccoppiare il pin REFIN a GND con un condensatore ceramico da 0,1 μF.

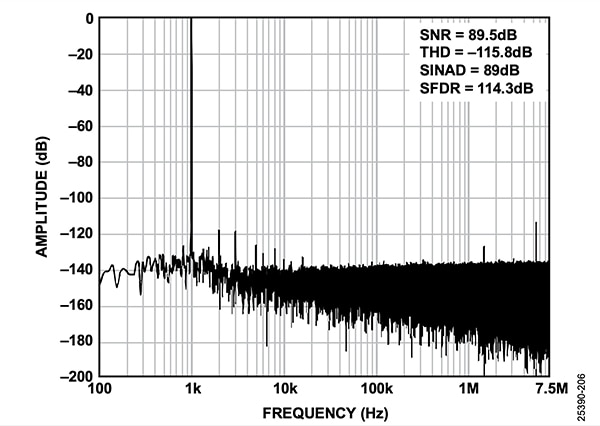

Il modulo ADAQ23875 elimina i grattacapi della selezione dell'FDA e della rete e resistiva appropriata per l'ADC, pur garantendo alte prestazioni e specifiche strette per SNR, THD, SINAD e SFDR (89,5 dB, -115,8 dB, 89 dB e 114,3 dB, rispettivamente) (Figura 5). Di solito, la raccolta delle specifiche del sistema spetta al progettista. L'approccio sistemico di ADAQ23875 aiuta i progettisti a soddisfare queste specifiche in modo più efficiente.

Figura 5: Il modulo ADAQ23875 crea le specifiche SNR, THD, SINAD, SFDR che passano attraverso l'FDA su chip, il filtro di 1o ordine e l'ADC SAR. (Immagine per gentile concessione di Analog Devices)

Figura 5: Il modulo ADAQ23875 crea le specifiche SNR, THD, SINAD, SFDR che passano attraverso l'FDA su chip, il filtro di 1o ordine e l'ADC SAR. (Immagine per gentile concessione di Analog Devices)

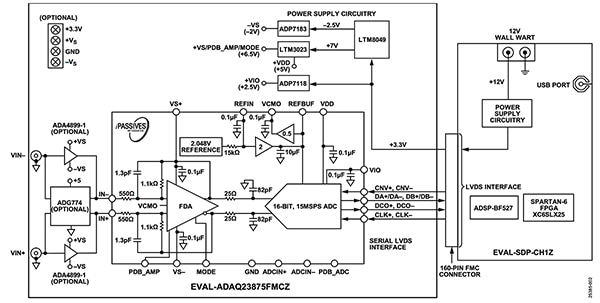

La Figura 5 mostra i risultati dei test SNR, THD, SINAD e SFDR per un segnale di ingresso differenziale a 1 kHz in ADAQ23875. Per un'applicazione specifica, la scheda EVAL-ADAQ23875FMCZ per ADAQ23875 è dotata di un software per assistere nelle valutazioni tra cui, programmazione del dispositivo, forma d'onda, istogramma e acquisizione FFT. I progettisti possono collegare la scheda di valutazione alla piattaforma dimostrativa EVAL-SDP-CH1Z di ADI per l'alimentazione e per permetterne il controllo da un PC attraverso la porta USB di SDP-CH1Z (Figura 6).

Figura 6: La scheda di valutazione ADAQ23875FMCZ (a sinistra) collegata alla scheda SDP (a destra) permette di controllare la scheda di valutazione attraverso la porta USB di un PC. (Immagine per gentile concessione di Analog Devices)

Figura 6: La scheda di valutazione ADAQ23875FMCZ (a sinistra) collegata alla scheda SDP (a destra) permette di controllare la scheda di valutazione attraverso la porta USB di un PC. (Immagine per gentile concessione di Analog Devices)

Il software della scheda di valutazione, il plugin ACE per scheda ADAQ23875 1.2021.8300 [18 feb 21] e il software ACE Installer 1.21.2994.1347 [08 feb 21], permette all'utente di configurare il valore di sovracampionamento di ogni canale, l'intervallo di ingresso, il numero di campioni e la selezione del canale attivo. Inoltre, questo software permette anche di salvare e aprire file con i dati dei test.

Conclusione

Per superare le sfide della progettazione analogica ad alta velocità e fornire le migliori prestazioni generali nell'acquisizione dati, i progettisti possono rivolgersi al modulo ADAQ23875. Si tratta di un sistema completo di conversione ad alta velocità che include un FDA, un filtro passa-basso di 1o ordine, un ADC SAR e una serie di condensatori di disaccoppiamento che amplificano i segnali di eccitazione e forniscono i segnali di pilotaggio appropriati, così come il filtraggio e la retroalimentazione dei segnali secondari. Essendo altamente integrato, il modulo del sistema di acquisizione dati ADAQ23875 elimina dal progetto la "magia nera" analogica con una soluzione completa da FDA a ADC SAR per l'acquisizione dati ad alta velocità, Hardware in the Loop (HiL) e analizzatori di potenza.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.