Perché espandere la memoria di programma del microcontroller con memoria flash che supporta un'interfaccia SPI XiP e come fare

Contributo di Editori nordamericani di DigiKey

2019-05-08

Le applicazioni basate su microcontroller stanno diventando sempre più complesse, per cui gli sviluppatori si trovano a dover usare più memoria di programma flash per il firmware dell'applicazione. Questo è particolarmente vero per gli endpoint Internet delle cose (IoT) che stanno iniziando a eseguire operazioni di edge computing relativamente complesse. Tuttavia, a volte le applicazioni possono espandersi tanto da richiedere una memoria di programma esterna e a quel punto gli sviluppatori devono scegliere tra una flash parallela e una seriale.

L'aggiunta di un chip di memoria flash parallela esterna collega le linee di I/O, aumenta la complessità e occupa più spazio su scheda. Questo articolo descriverà brevemente come espandere la memoria di programma flash di un microcontroller aggiungendo un chip di memoria flash seriale esterna di Adesto Technologies che supporta un'interfaccia SPI eXecute in Place (XiP). Verrà anche spiegato come mappare la flash XiP nello spazio di memoria di un microcontroller di Microchip Technology, in modo da rendere l'esecuzione del codice quasi trasparente al firmware.

Perché espandere la memoria esterna

Quando possibile, come prima cosa gli sviluppatori dovrebbero scegliere per la loro applicazione un microcontroller che preveda un percorso di dispositivi a piedinatura compatibile con più memoria. Se, durante lo sviluppo, il firmware dell'applicazione si espande fino a superare la memoria flash del dispositivo di destinazione, si può facilmente sostituire il dispositivo con uno a piedinatura compatibile ma avente più memoria flash. Questo permette di espandere la memoria dell'applicazione senza dover riprogettare la scheda per un altro microcontroller.

L'applicazione potrebbe però richiedere più memoria di quella disponibile sul chip per una famiglia di microcontroller a piedinatura compatibile, per cui si rende necessario l'uso di memoria flash non su chip. Questa situazione sta diventando sempre più comune e può essere dovuta a vari motivi, tra cui i seguenti:

- Durante la fase di sviluppo, l'ambito del sistema potrebbe andare oltre il suo intento iniziale. All'ultimo minuto potrebbero essere stati apportati dei cambiamenti all'applicazione, potrebbero essere state introdotte altre funzionalità oppure la memoria prevista potrebbe essersi rivelata non adeguata. In questo caso si può optare per l'aggiornamento con un microcontroller a piedinatura compatibile che ha più memoria di programma flash, oppure aggiungere altra memoria di programma flash esterna, ma se lo sviluppo è già in fase avanzata il progetto potrebbe subire dei ritardi.

- I futuri aggiornamenti del firmware sul campo possono richiedere più memoria di programma flash di quella disponibile nel microcontroller già presente nella scheda di sistema. Stando così le cose, le opzioni non sono molte: sostituire i sistemi esistenti con altri con più memoria flash oppure annullare l'aggiornamento.

- Lo sviluppo della famiglia di prodotti di sistema potrebbe richiedere un nuovo prodotto che ha bisogno di più memoria di programma flash di quella già disponibile per la famiglia di microcontroller con piedinatura compatibile. Le opzioni praticabili sono: riprogettare il sistema utilizzando una nuova famiglia di microcontroller oppure aggiungere memoria di programma flash esterna.

Per uno sviluppatore è ovviamente importante prevedere di quanta memoria in più avranno bisogno i sistemi presenti e futuri e pianificare di conseguenza. Se è probabile che al progetto servirà una memoria flash esterna, lo sviluppatore dovrebbe predisporre lo spazio per la futura espansione della scheda. Anche se il chip di memoria flash non richiede il montaggio sulla scheda, è meglio stare dalla parte del sicuro e predisporre in anticipo lo spazio.

Tradizionalmente, per espandere la memoria di programma flash si utilizzava un'interfaccia flash parallela con indirizzo e linee dati. Ma anche l'uso più efficiente della memoria flash parallela che non sacrifica la velocità può richiedere 16 bit di indirizzo, 16 bit di dati e quattro o più segnali di controllo. Questo significa che il microcontroller dovrebbe avere almeno 36 pin.

Oltre a rappresentare un uso poco efficiente delle risorse di un microcontroller, questo limita la scelta a dispositivi con un bus esterno, il che aumenta ulteriormente il numero di pin del microcontroller. Inoltre, un bus parallelo esterno occupa molto spazio su scheda e l'indirizzo e il bus dati ad alta velocità aumentano la possibilità di interferenze elettromagnetiche (EMI).

Esecuzione del codice SPI XiP

L'uso di un dispositivo di memoria di programma flash esterna che supporta un'interfaccia SPI XiP rappresenta un'opzione più efficace. Per interfacciarsi col microcontroller host un'interfaccia SPI XiP richiede solo sei pin. Diversamente da un'interfaccia SPI convenzionale, la memoria sul dispositivo di memoria flash esterna non è accessibile direttamente con un driver firmware SPI, ma è mappata nella memoria di programma del microcontroller.

Un buon esempio di dispositivo di memoria flash progettato per interfacciarsi tramite un'interfaccia SPI XiP è AT25SL321-UUE-T di Adesto Technologies (Figura 1). Si tratta di una memoria flash da 32 Mbit che supporta le modalità SPI singola, dual e quad. Supporta un clock SPI a 104 MHz, che in modalità dual SPI fornisce una frequenza di clock equivalente di 266 MHz, mentre in modalità quad SPI la frequenza di clock equivalente è di 532 MHz.

Figura 1: AT25SL321 di Adesto è una memoria flash da 32 Mbit che supporta le modalità SPI singola, dual e quad. Fornisce 32 Mbit di memoria flash in un contenitore SOIC, DFN8 o TSSOP8 a 8 pin. (Immagine per gentile concessione di Adesto Technologies)

Oltre ai 32 Mbit di flash, il dispositivo ha registri di stato per la sua configurazione. La lettura di questi registri può indicare al firmware se nel dispositivo è in corso un'operazione di scrittura o di cancellazione. La scrittura nei registri di stato consente di proteggere i blocchi di memoria flash dalla scrittura.

AT25SL321 di Adesto ha anche 4 kbit di memoria programmabile una sola volta (OTP) che possono essere utilizzati per archiviare informazioni di sicurezza come un numero di serie univoco. È racchiusa in un contenitore SOIC, DFN8 o TSSOP8 a 8 pin.

Come tutti i dispositivi di memoria seriale che supportano SPI XiP, AT25SL321 di Adesto è configurato tramite un set di istruzioni specifiche per i dispositivi Adesto. Questo set è costituito da 38 comandi che vengono utilizzati dal microcontroller host per controllare la flash seriale. Una periferica SPI XiP su un microcontroller host includerà una macchina a stati programmabili che viene inizializzata all'accensione del microcontroller con il set di istruzioni della flash seriale di destinazione. Una volta inizializzata, il funzionamento della periferica SPI è trasparente al firmware che esegue il codice nella regione SPI XiP mappata in memoria.

Ad esempio, se il firmware del microcontroller host legge i dati dalla regione mappata in memoria, la SPI XiP configurata con il set di istruzioni Adesto invia alla memoria seriale Adesto un codice di istruzioni Read Data seguito da un indirizzo di byte di 24 bit. La memoria seriale Adesto invia quindi il suo contenuto al microcontroller host un byte alla volta. Al firmware questo appare come una normale operazione di lettura dalla memoria.

Oltre a un pin di selezione del clock SPI, di dati e chip, AT25SL321 di Adesto ha altri due pin per una migliore funzionalità in-system. WP\ è un pin attivo basso che impedisce la scrittura nel registro di stato per proteggere i blocchi di codice. Il microcontroller può utilizzare questo pin per evitare che attività con una bassa priorità effettuino modifiche non autorizzate. HOLD\ viene utilizzato per mettere in pausa un trasferimento dati in corso. La messa in pausa può essere utile se il microcontroller riceve un segnale di interrupt ad alta priorità mentre è in corso un trasferimento dati nella memoria che deve essere messo in pausa finché l'interrupt non viene risolto.

Il dispositivo flash a 32 Mbit AT25SL321 di Adesto supporta quattro modalità di funzionamento:

- Funzionamento SPI standard: alla memoria flash si accede come avviene nel caso di un dispositivo di memoria SPI standard con clock SPI (SCLK), selezione chip (CS\) attivo basso, dati di ingresso seriale (SI) e dati di uscita seriale (SO). Sono supportate le modalità bus SPI standard 0 e 3.

- Funzionamento Dual SPI: questa modalità offre una velocità dati doppia rispetto a quella del funzionamento SPI standard utilizzando SI e SO come pin dati bidirezionali, designati IO0 e IO1.

- Funzionamento Quad SPI: questa modalità offre una velocità dati che è quattro volte quella del funzionamento SPI standard. Oltre a IO0 e IO1, anche WP\ e HOLD\ sono usati come pin dati bidirezionali, IO2 e IO3. Nel funzionamento Quad SPI, le funzioni WP\ e HOLD\ non sono disponibili.

- Funzionamento QPI: questa modalità è utilizzata solo per il funzionamento SPI XiP. Mentre le modalità SPI standard, dual e quad supportano l'invio di comandi alla memoria SPI utilizzando solo il pin IO0, il funzionamento QPI supporta l'invio di comandi utilizzando i quattro pin IO[0:3], cosa che migliora in modo significativo le prestazioni di SPI XiP.

Se i 32 Mbit di AT25SL321 non sono sufficienti, Adesto offre anche AT25QL641-UUE-T a 64 Mbit. I due dispositivi hanno una piedinatura compatibile, per cui AT25QL641 può essere un'alternativa drop-in. L'unica differenza tra i due dispositivi è data dal fatto che, oltre ad avere più memoria, per impostazione predefinita AT25QL641 all'accensione si porta sul funzionamento QPI. Quindi, in sistemi ad alte prestazioni il tempo di configurazione del dispositivo si riduce. Entrambi i dispositivi di memoria Adesto assorbono solo 5 mA durante un ciclo di lettura dalla memoria. Entrambi funzionano su un singolo rail tra 1,7 e 2,0 V e possono interfacciarsi con qualsiasi microcontroller compatibile con la tensione che abbia un'interfaccia SPI XiP.

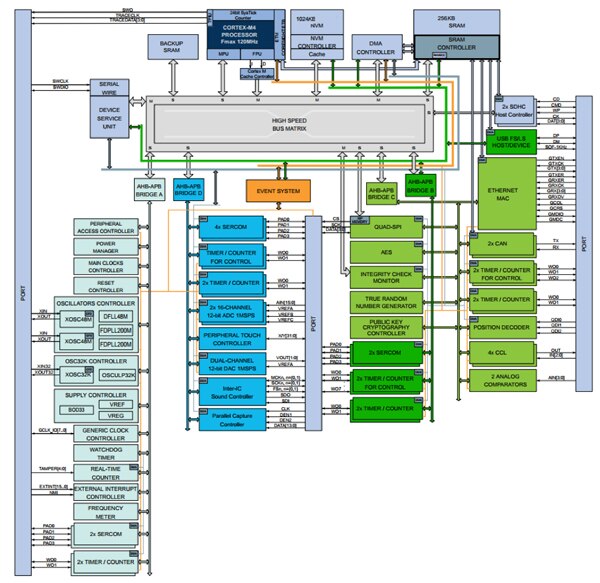

Per un microcontroller host, Microchip Technology ha interfacce SPI XiP nella sua serie ATSAMD51, fra cui il microcontroller ATSAMD51J20A-UUT basato su Arm® Cortex®-M4F a 120 MHz. Questo dispositivo ha 1 MB di flash e 256 kB di RAM. Ha una gamma completa di periferiche, tra cui un convertitore analogico/digitale (ADC), un convertitore digitale/analogico (DAC), una porta USB e I2S. Inoltre ha una periferica di crittografia a chiave pubblica e un generatore di numeri casuali reali (TRNG) per le funzioni di sicurezza.

Figura 2: ATSAMD51J20A di Microchip ha un set completo di periferiche, tra cui un'interfaccia seriale SPI XiP, ADC, DAC e supporto per la crittografia dei dati. (Immagine per gentile concessione di Microchip Technology)

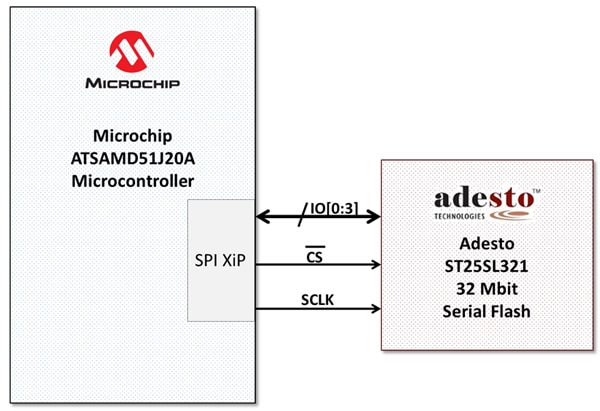

Per collegarsi alla memoria flash esterna, gli sviluppatori possono utilizzare la periferica QSPI di ATSAMD51J20A che supporta SPI XiP. Questo consente di eseguire il codice direttamente dalla memoria flash Adesto. ATSAMD51J20A mappa la flash Adesto nello spazio di memoria del programma Advanced High-Performance Bus (AHB) di Arm. Per proteggere i dati nella memoria flash seriale, la SIP XiP ATSAMD51J20A supporta lo scrambling trasparente dei dati scritti nella memoria SPI esterna e il descrambling dei dati letti dalla stessa memoria. Questo può aiutare a impedire la copia non autorizzata del firmware e azioni di pirateria ai danni del sistema.

Figura 3: Il microcontroller a 32 bit ATSAMD51J20A di Microchip ha una periferica QSPI che supporta una porta seriale SPI XiP. Può interfacciarsi facilmente con la flash seriale AT25SL321 di Adesto utilizzando solo sei pin. (Immagine per gentile concessione di DigiKey)

Utilizzo di ATSAMD51J20A di Microchip con un dispositivo di memoria flash seriale Adesto

La periferica SPI XiP ATSAMD51J20A di Microchip ha tre registri utilizzati per inviare comandi a una flash seriale XiP esterna. Dato che i dispositivi di memoria flash XiP seriale di fornitori diversi utilizzano codici di istruzione diversi, lo sviluppatore deve configurare questi registri come segue per lo specifico fornitore di memoria utilizzato:

- L'Instruction Code Register contiene le istruzioni per accedere alla memoria flash seriale. Per un dispositivo di memoria flash Adesto che opera in modalità quad SPI, questo registro contiene un'istruzione Fast Read Quad Output 0x6B se il firmware sta eseguendo il codice dalla regione XiP mappata in memoria. Il registro deve essere cambiato nel codice di istruzione appropriato se viene eseguita un'operazione di scrittura, cancellazione o registro di stato.

- L'Instruction Address Register contiene l'indirizzo della memoria flash a cui si accede nella memoria flash seriale esterna. Quando la SPI XiP ATSAMD51J20A di Microchip è configurata per la modalità memoria seriale, questo indirizzo viene impostato automaticamente dalla periferica SPI XiP sull'indirizzo che il firmware sta eseguendo nell'intervallo da 0x0400 0000 a 0x0500 0000 dello spazio di memoria AHB mappato in memoria.

- L'Instruction Frame Register configura la SPI XiP per il formato del frame di istruzioni specifico per il dispositivo di memoria esterna utilizzato. Le operazioni comprendono la selezione della lunghezza dell'indirizzo di 24 o 32 bit, l'abilitazione della trasmissione a doppia velocità dati (DDR), se è supportata la modalità di lettura continua, e la lunghezza dell'opcode.

Il resto dell'interfaccia SPI XiP di Microchip può essere facilmente configurato tramite i driver SPI di Microchip.

Se il firmware dell'applicazione nel microcontroller esegue il codice dalla regione mappata nella memoria SPI XiP, non è necessario riconfigurare la periferica SPI XiP sul microcontroller. La memoria flash Adesto supporta anche una modalità di lettura con il solo pin SI singolo con il codice di istruzione 0x03. Se si utilizza solo la modalità dual SPI, il codice di istruzione è 0x3B. Questi codici sono scritti dal firmware dell'applicazione nel registro dei codici di istruzione.

Quando si cambia il registro dei codici di istruzione, è buona pratica svuotare le cache associate allo spazio dell'indirizzo mappato in memoria. Quando si legge o si scrive nei registri di stato della memoria flash seriale, la cache dovrebbe essere prima svuotata e poi disabilitata. La stessa cosa dovrebbe avvenire anche quando si scrive nella flash nelle regioni mappate in memoria. Quando si riprendono le operazioni di lettura dalla memoria la cache dovrebbe essere riattivata.

Trattandosi di trasferimenti di dati ad alta velocità, sulla scheda la flash seriale dovrebbe essere posizionata il più vicino possibile alla porta SPI XiP del microcontroller. Se ciò non fosse possibile, nessuna traccia dovrebbe essere più lunga di 120 mm. Per evitare interferenze, la distanza tra il segnale di clock e gli altri segnali dovrebbe essere pari ad almeno tre volte la larghezza delle tracce della scheda. Per evitare la distorsione, tutti i segnali dei dati bidirezionali IO[0:3] dovrebbero essere entro 10 mm l'uno dall'altro.

Conclusione

I dispositivi di memoria flash seriale esterna possono fornire una rapida esecuzione del codice del firmware senza la complessità e lo spazio su scheda occupato dai chip di memoria flash parallela. Questo consente sia di espandere facilmente il codice del programma nel corso del tempo, sia di applicare gli aggiornamenti sul campo senza dover riprogettare la scheda di sistema.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.